SNOSD95C April 2020 – December 2020 LM7480-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Applications and Implementation

- 10.1 Application Information

- 10.2 Typical 12-V Reverse Battery Protection Application

- 10.3 200-V Unsuppressed Load Dump Protection Application

- 10.4 Do's and Don'ts

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DRR|12

Thermal pad, mechanical data (Package|Pins)

- DRR|12

Orderable Information

10.2.2.3 Input Micro-Short Protection: LV124 E-10

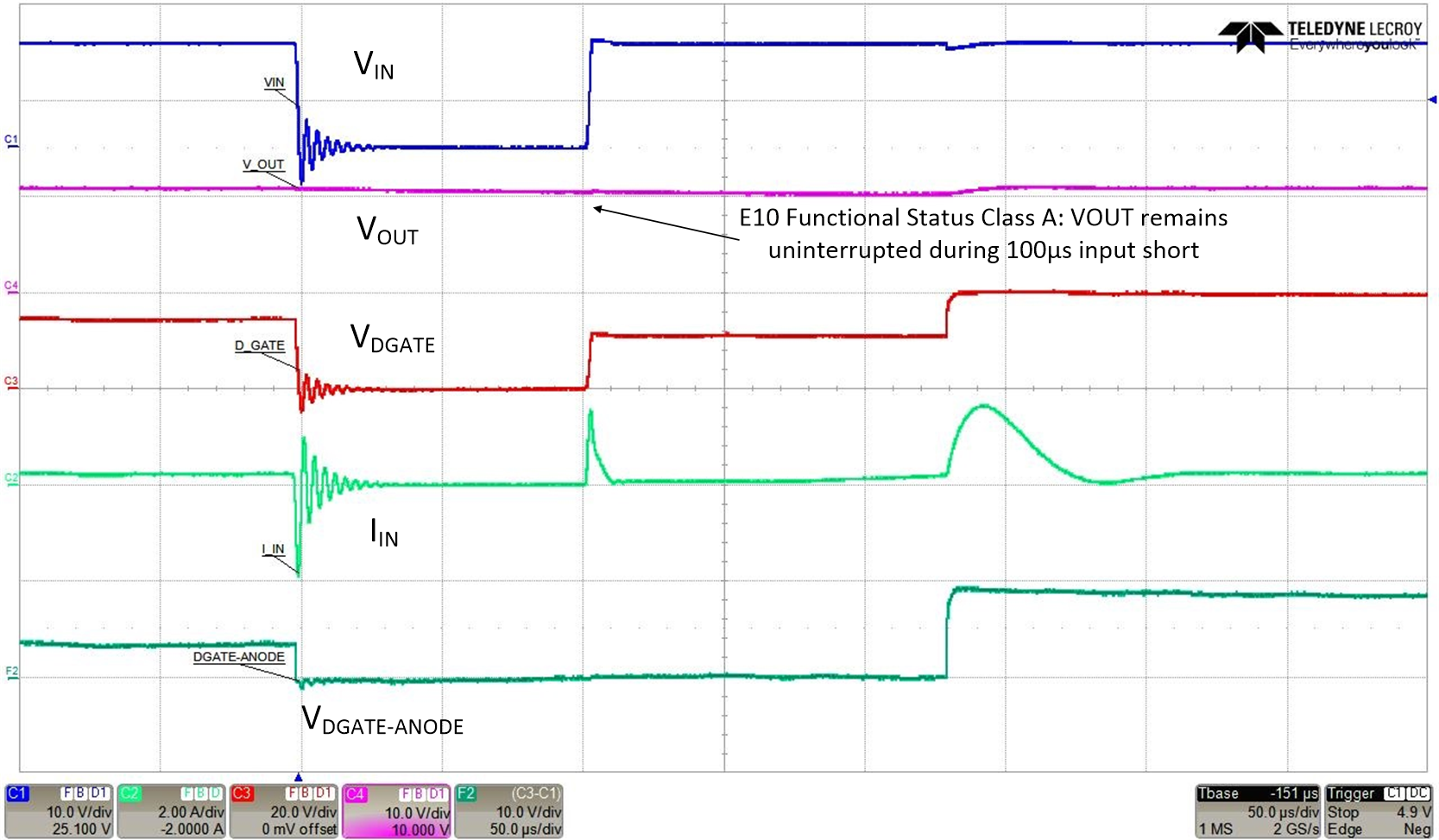

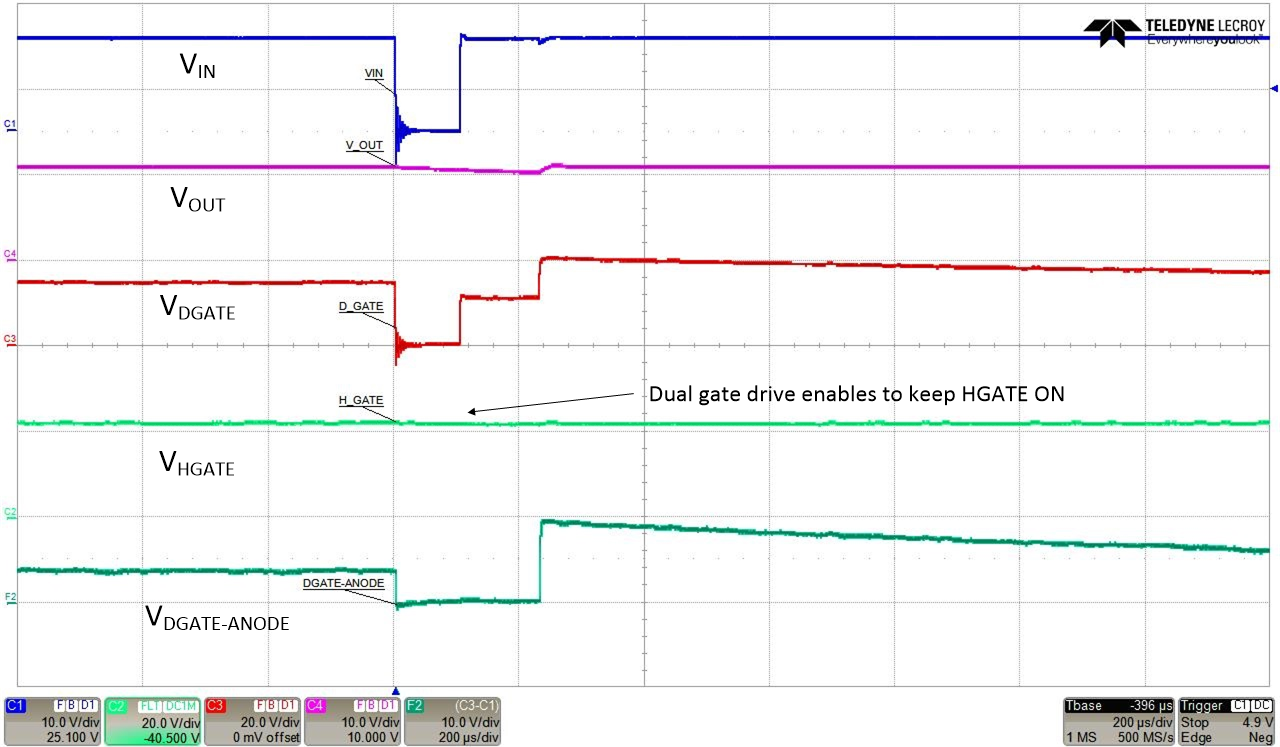

E-10 test specified in LV124 standard checks for immunity of electronic modules to short interruptions in power supply input due to contact issues or relay bounce. During this test (case 2), micro-short is applied on the input for a duration as low as 10 µs to several ms. For a functional pass status A, electronic modules are required to run uninterrupted during the E-10 test (case 2) with 100-µs duration. Dual-Gate drive architecture of LM7480x-Q1 - DGATE and HGATE - enables to achieve a functional pass status A with optimum hold up capacitance on the output when compared to a single gate drive controller. When input micro-short is applied for 100 µs, LM7480x-Q1 quickly turns off MOSFET Q1 by shorting DGATE to ANODE (source of MOSFET) within 0.5µs to prevent the output from discharging and the HGATE remains ON keeping MOSFET Q2 ON, enabling fast recovery after the input short is removed.

Performance of LM74800-Q1 during E10 input power supply interruption test case 2 is shown in Figure 10-5. After the input short is removed, input voltage recovers and MOSFET Q1 is turned back ON within 130 µs. Note that dual-gate drive topology allows MOSFET Q2 to remain ON during the test and helps in restoring the input power faster. Output voltage remains unperturbed during the entire duration, achieving functional status A.

Figure 10-5 Input Micro-Short - LV124 E10 TC 2 100

µs

Figure 10-5 Input Micro-Short - LV124 E10 TC 2 100

µs Figure 10-6 Input Micro-Short - LV124 E10 TC 2 100 µs with

HGATE

Figure 10-6 Input Micro-Short - LV124 E10 TC 2 100 µs with

HGATE