SNOSD95C April 2020 – December 2020 LM7480-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Applications and Implementation

- 10.1 Application Information

- 10.2 Typical 12-V Reverse Battery Protection Application

- 10.3 200-V Unsuppressed Load Dump Protection Application

- 10.4 Do's and Don'ts

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DRR|12

Thermal pad, mechanical data (Package|Pins)

- DRR|12

Orderable Information

10.2.3.5 Overvoltage Protection and Battery Monitor

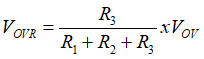

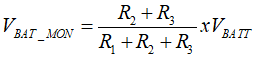

Resistors R1, R2 and R3 connected in series are used to program the overvoltage threshold and battery monitor ratio. The resistor values required for setting the overvoltage threshold VOV to 37.0 V and battery monitor ratio VBATT_MON : VBATT to 1:8 are calculated by solving Equation 3 and Equation 4.

For minimizing the input current drawn from the battery through resistors R1, R2 and R3, it recommended to use higher value of resistance. Using high value resistors will add error in the calculations because the current through the resistors at higher value will become comparable to the leakage current into the OV pin. Maximum leakage current into the OV pin is 1 µA and choosing (R1 + R2 + R3) < 120 kΩ ensures current through resistors is 100 times greater than leakage through OV pin.

Based on the device electrical characteristics, VOVR is 1.23 V and battery monitor ratio (VBATT_MON / VBATT) is designed for a ratio of 1/8. To limit (R1 + R2 + R3) < 120 kΩ, select (R1 + R2) = 100 kΩ. Solving Equation 3 gives R3 = 3.45 kΩ. Solving Equation 4 for R2 using (R1 + R2) = 100 kΩ and R3 = 3.45 kΩ, gives R2 = 9.48 kΩ and R1 = 90.52 kΩ.

Standard 1% resistor values closest to the calculated resistor values are R1 = 90.9 kΩ, R2 = 9.09 kΩ and R3 = 3.48 kΩ.