SNOS738I April 1995 – January 2017 LM9061 , LM9061-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- D|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

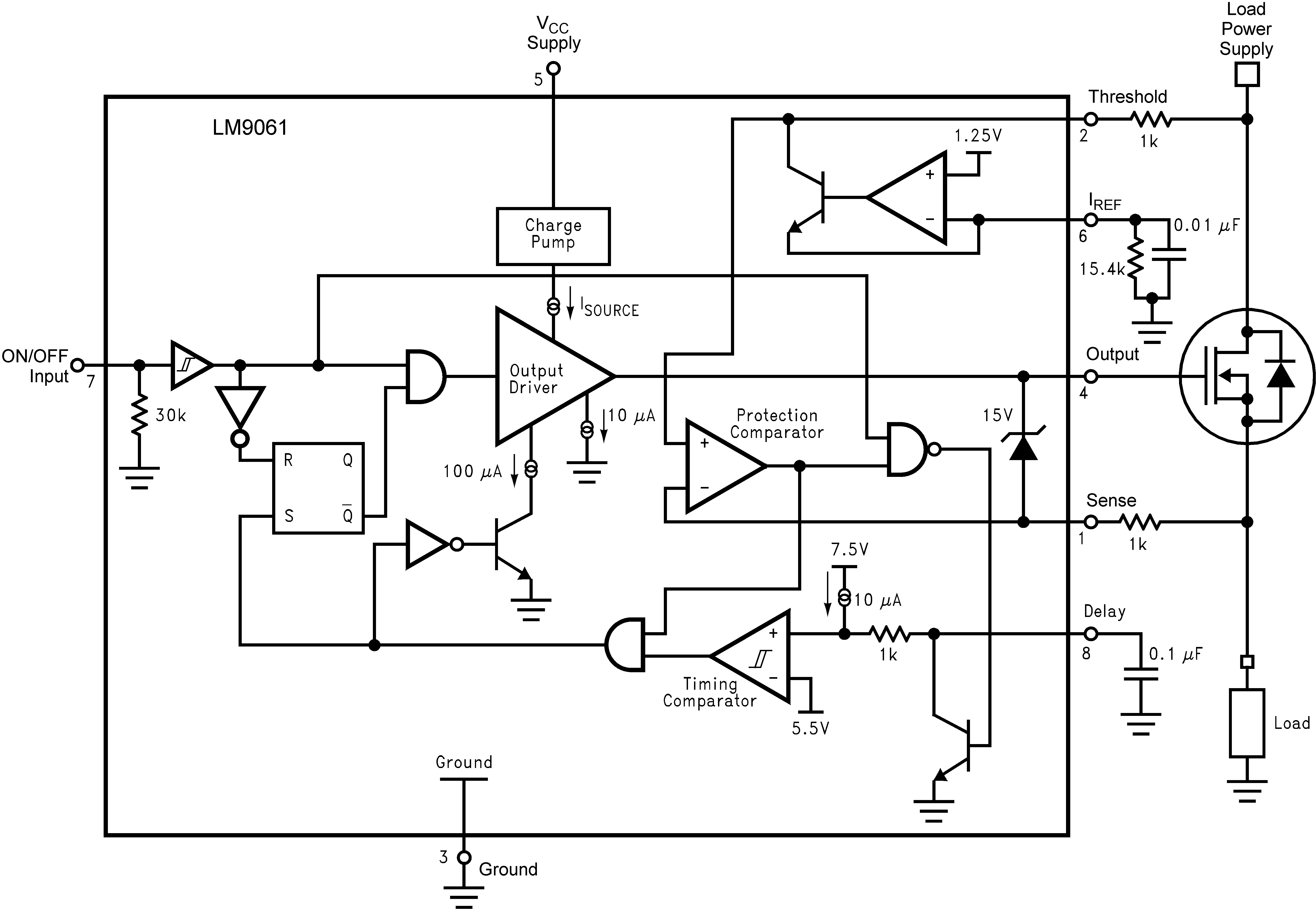

7 Detailed Description

7.1 Overview

The LM9061 is a high-side controller that can protect the load from overcurrent and overvoltage. An internal charge pump circuit generates the gate voltage to drive the high-side MOSFET. The voltage drop, VDS, across the MOSFET is monitored to protect from excessive current. If the VDS voltage, due to excessive load current, exceed the threshold voltage, the output is latched OFF after a programmable delay time interval.

7.2 Functional Block Diagram

7.3 Feature Description

7.3.1 MOSFET Gate Drive

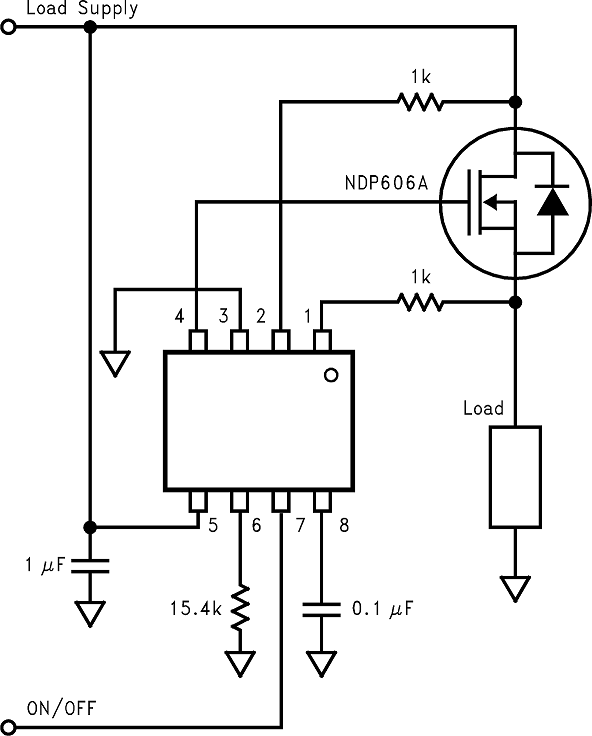

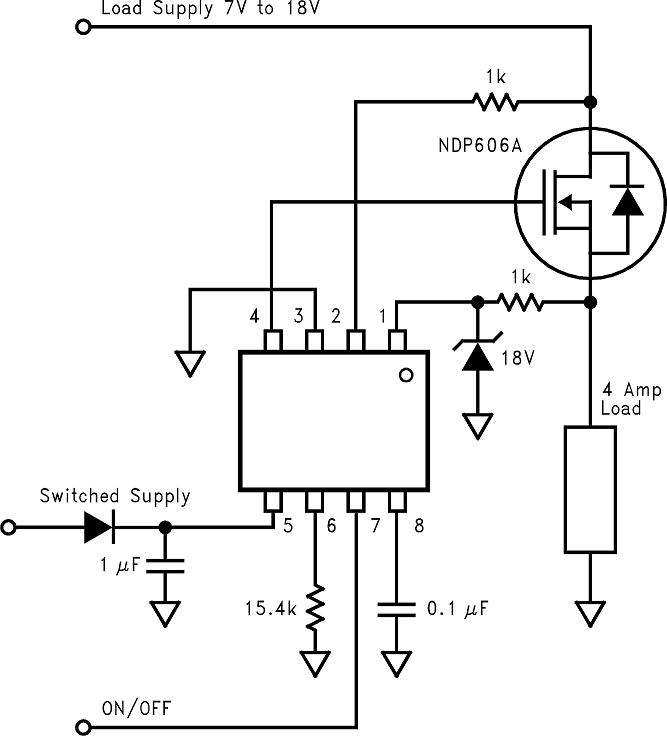

The LM9061 contains a charge pump circuit that generates a voltage in excess of the applied supply voltage to provide the gate drive to high-side MOSFET transistors. Any size of N-channel power MOSFET, including multiple parallel connected MOSFETs for very high current applications, can be used to apply power to a ground referenced load circuit in what is referred to as high-side drive applications. Figure 12 shows the basic application of the LM9061.

Figure 12. Basic Application Circuit

Figure 12. Basic Application Circuit

7.3.2 Basic Operation

When commanded ON by a logic 1 input to pin 7 the gate drive output, pin 4, rises quickly to the VCC supply potential at pin 5. Once the gate voltage exceeds the gate-source threshold voltage of the MOSFET, VGS(ON), (the source is connected to ground through the load) the MOSFET turns ON and connects the supply voltage to the load. With the source at near the supply potential, the charge pump continues to provide a gate voltage greater than the supply to keep the MOSFET turned ON. To protect the gate of the MOSFET, the output voltage of the LM9061 is clamped to limit the maximum VGS to 15 V.

It is important to remember that during the Turnon of the MOSFET the output current to the Gate is drawn from the VCC supply pin. The VCC pin must be bypassed with a capacitor with a value of at least 10 times the Gate capacitance, and no less than 0.1 μF. The output current into the Gate will typically be 30 mA with VCC at 14 V and the Gate at 0 V. As the Gate voltage rises to VCC, the output current decreases. When the Gate voltage reaches VCC, the output current will typically be 1 mA with VCC at 14 V.

A logic 0 on pin 7 turns the MOSFET OFF. When commanded OFF a 110-µA current sink is connected to the output pin. This current discharges the gate capacitances of the MOSFET linearly. When the gate voltage equals the source voltage (which is near the supply voltage) plus the VGS(ON) threshold of the MOSFET, the source voltage starts following the gate voltage and ramps toward ground. Eventually the source voltage equals 0 V and the gate continues to ramp to zero thus turning OFF the power device. This gradual turnoff characteristic, instead of an abrupt removal of the gate drive, can, in some applications, minimize the power dissipation in the MOSFET or reduce the duration of negative transients, as is the case when driving inductive loads. In the event of an overstress condition on the power device, the turnoff characteristic is even more gradual as the output sinking current is only 10 µA (see Lossless Overcurrent Protection).

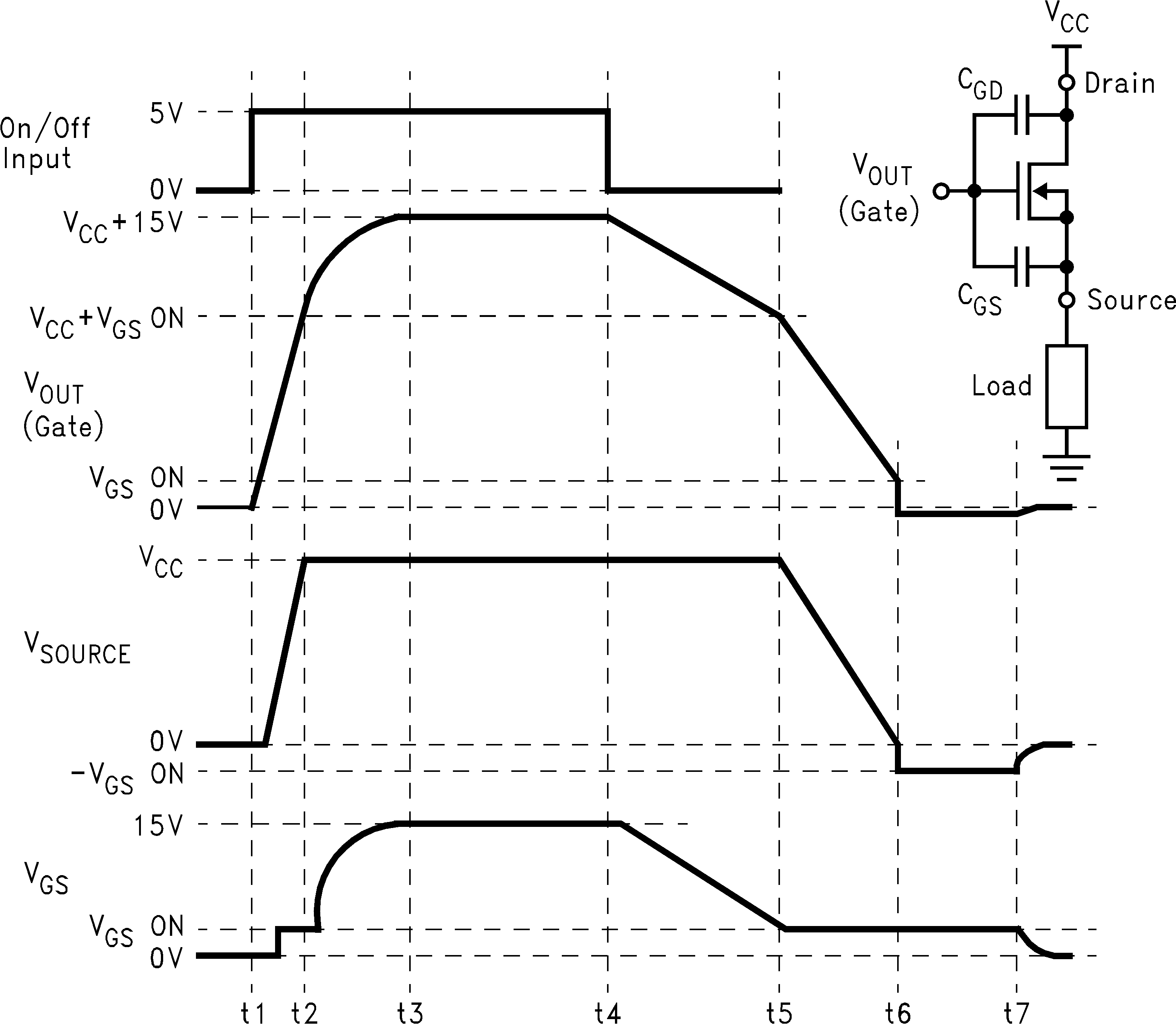

7.3.3 Turn On and Turn Off Characteristics

The actual rate of change of the voltage applied to the gate of the power device is directly dependent on the input capacitances of the MOSFET used. These times are important to know if the power to the load is to be applied repetitively as is the case with pulse width modulation drive. Of concern are the capacitances from gate to drain, CGD, and from gate to source, CGS. Figure 13 details the turnon and turnoff intervals in a typical application. An inductive load is assumed to illustrate the output transient voltage to be expected. At time t1, the ON/OFF input goes high. The output, which drives the gate of the MOSFET, immediately pulls the gate voltage towards the VCC supply of the LM9061. The source current from pin 4 is typically 30 mA which quickly charges CGD and CGS. As soon as the gate reaches the VGS(ON) threshold of the MOSFET, the switch turns ON and the source voltage starts rising towards VCC. VGS remains equal to the threshold voltage until the source reaches VCC. While VGS is constant only CGD is charging. When the source voltage reaches VCC, at time t2, the charge pump takes over the drive of the gate to ensure that the MOSFET remains ON.

The charge pump is basically a small internal capacitor that acquires and transfers charge to the output pin. The clock rate is set internally at typically 300 kHz. In effect the charge pump acts as a switched capacitor resistor (approximately 67k) connected to a voltage that is clamped at 13 V above the Sense input pin of the LM9061 which is equal to the VCC supply in typical applications. The gate voltage rises above VCC in an exponential fashion with a time constant dependent upon the sum of CGD and CGS. At this time however the load is fully energized. At time t3, the charge pump reaches its maximum potential and the switch remains ON.

At time t4, the ON/OFF input goes low to turn off the MOSFET and remove power from the load. At this time the charge pump is disconnected and an internal 110-µA current sink begins to discharge the gate input capacitances to ground. The discharge rate (ΔV/ΔT) is equal to 110 µA/ (CGD + CGS).

The load is still fully energized until time t5 when the gate voltage has reached a potential of the source voltage (VCC) plus the VGS(ON) threshold voltage of the MOSFET. Between time t5 and t6, the VGS voltage remains constant and the source voltage follows the gate voltage. With the voltage on CGD held constant the discharge rate now becomes 110 µA/CGD.

At time t6 the source voltage reaches 0 V. As the gate moves below the VGS(ON) threshold the MOSFET tries to turn off. With an inductive load, if the current in the load has not collapsed to zero by time t6, the action of the MOSFET turning off creates a negative voltage transient (flyback) across the load. The negative transient will be clamped to −VGS(ON) because the MOSFET must turn itself back on to continue conducting the load current until the energy in the inductance has been dissipated (at time t7).

7.3.4 Lossless Overcurrent Protection

A unique feature of the LM9061 is the ability to sense excessive power dissipation in the MOSFET and latch it OFF to prevent permanent failure. Instead of sensing the actual current flowing through the MOSFET to the load, which typically requires a small valued power resistor in series with the load, the LM9061 monitors the voltage drop from drain to source, VDS, across the MOSFET. This lossless technique allows all of the energy available from the supply to be conducted to the load as required. The only power loss is that of the MOSFET itself and proper selection of a particular power device for an application minimizes this concern. Another benefit of this technique is that all applications use only standard inexpensive ¼W or less resistors.

To use this lossless protection technique requires knowledge of key characteristics of the power MOSFET used. In any application the emphasis for protection can be placed on either the power MOSFET or on the amount of current delivered to the load, with the assumption that the selected MOSFET can safely handle the maximum load current.

Figure 13. Turnon and Turnoff Waveforms

Figure 13. Turnon and Turnoff Waveforms

To protect the MOSFET from exceeding its maximum junction temperature rating, the power dissipation must be limited. The maximum power dissipation allowed (derated for temperature) and the maximum drain to source ON resistance, RDS(ON), with both at the maximum operating ambient temperature, must be determined. When switched ON the power dissipation in the MOSFET is calculated by Equation 1:

The VDS voltage to limit the maximum power dissipation is therefore calculated by Equation 2:

With this restriction, the actual load current and power dissipation obtained is a direct function of the actual RDS(ON) of the MOSFET at any particular ambient temperature but the junction temperature of the power device never exceeds its rated maximum.

To limit the maximum load current requires an estimate of the minimum RDS(ON) of the MOSFET (the minimum RDS(ON) of discrete MOSFETs is rarely specified) over the required operating temperature range.

The maximum current to the load is calculated by Equation 3:

The maximum junction temperature of the MOSFET or the maximum current to the load can be limited by monitoring and setting a maximum operational value for the drain to source voltage drop, VDS. In addition, in the event that the load is inadvertently shorted to ground, the power device is automatically be turned off.

In all cases, if the MOSFET be switched OFF by the built in protection comparator, the output sink current is switched to only 10 µA to gradually turn off the power device.

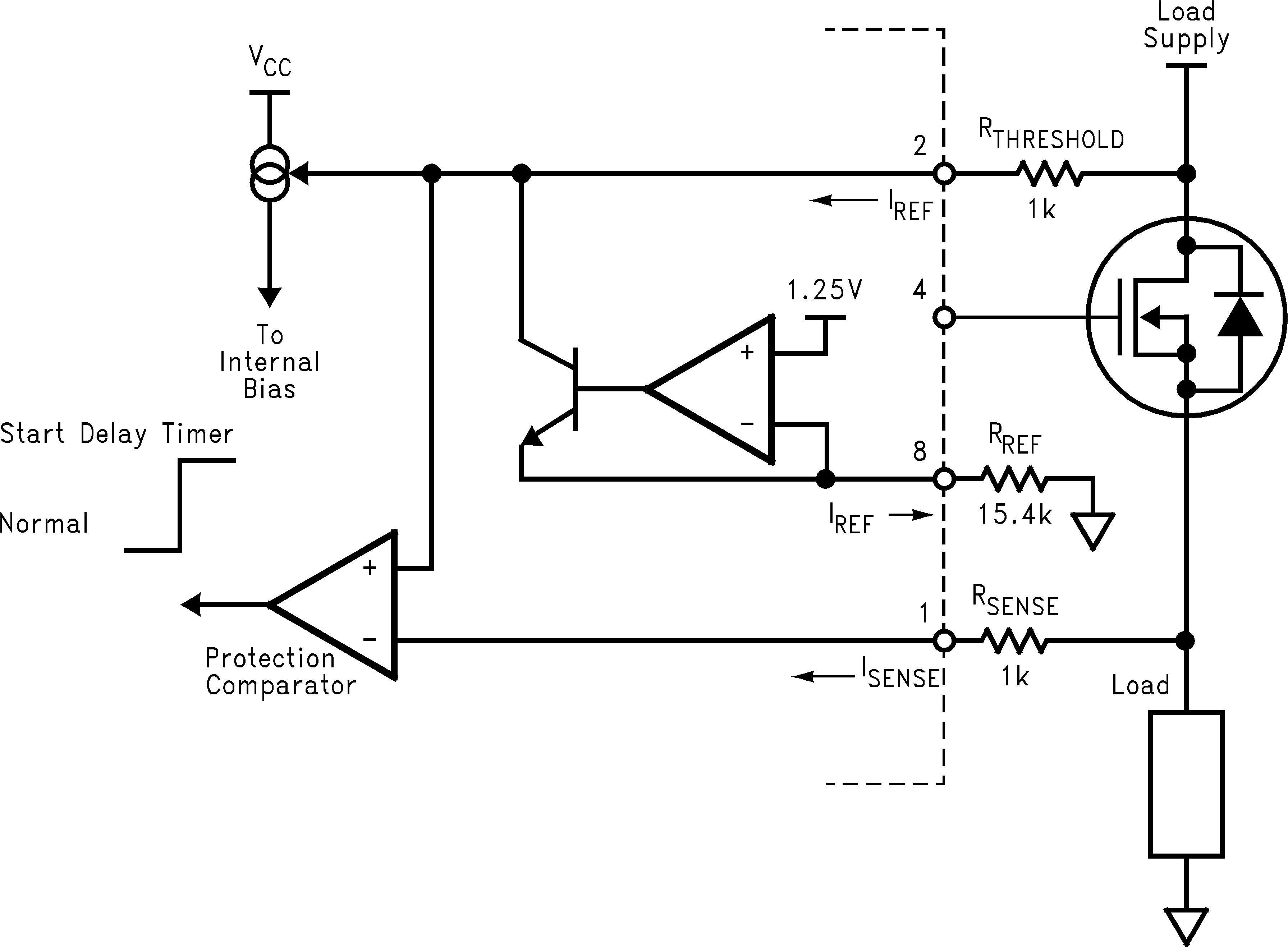

Figure 14 illustrates how the threshold voltage for the internal protection comparator is established.

Two resistors connect the drain and source of the MOSFET to the LM9061. The Sense input, pin 1, monitors the source voltage while the Threshold input, pin 2, is connected to the drain, which is also connected to the constant load power supply. Both of these inputs are the two inputs to the protection comparator. If the voltage at the sense input ever drop below the voltage at the threshold input, the protection comparator output goes high and initiates an automatic latch-OFF function to protect the power device. Therefore the switching threshold voltage of the comparator directly controls the maximum VDS allowed across the MOSFET while conducting load current.

The threshold voltage is set by the voltage drop across resistor RTHRESHOLD. A reference current is fixed by a resistor to ground at IREF, pin 6. To precisely regulate the reference current over temperature, a stable band gap reference voltage is provided to bias a constant current sink. The reference current is set by Equation 4:

The reference current sink output is internally connected to the threshold pin. IREF then flows from the load supply through RTHRESHOLD. The fixed voltage drop across RTHRESHOLD is approximately equal to the maximum value of VDS across the MOSFET before the protection comparator trips.

It is important to note that the programmed reference current serves a multiple purpose as it is used internally for biasing and also has a direct effect on the internal charge pump switching frequency. The design of the LM9061 is optimized for a reference current of approximately 80 µA, set with a 15.4 kΩ ±1% resistor for RREF. To obtain the ensured performance characteristics, TI recommends using a 15.4-kΩ resistor for RREF.

The protection comparator is configured such that during normal operation, when the output of the comparator is low, the differential input stage of the comparator is switched in a manner that there is virtually no current flowing into the noninverting input of the comparator. Therefore, only IREF flows through resistor RTHRESHOLD. All of the input bias current, 20 µA maximum, for the comparator input stage (twice the ISENSE specification of 10 µA maximum, defined for equal potentials on each of the comparator inputs) however flows into the inverting input through resistor RSENSE. At the comparator threshold, the current through RSENSE is no more than the ISENSE specification of 10 µA.

Figure 14. Protection Comparator Biasing

Figure 14. Protection Comparator Biasing

To tailor the VDS (MAX) threshold for any particular application, the resistor RTHRESHOLD can be selected per Equation 5:

where

- RREF = 15.4 kΩ.

- ISENSE is the input bias current to the protection comparator.

- RSENSE is the resistor connected to pin 1.

- VOS is the offset voltage of the protection comparator (typically in the range of ±10 mV).

The resistor RSENSE is optional, but TI strongly recommends proving transient protection for the Sense pin, especially when driving inductive type loads. A minimum value of 1 kΩ protects the pin from transients ranging from −25 V to +60 V. This resistor must be equal to, or less than, the resistor used for RTHRESHOLD. Never set RSENSE to a value larger than RTHRESHOLD. When the protection comparator output goes high, the total bias current for the input stage transfers from the Sense pin to the Threshold pin, thereby changing the voltages present at the inputs to the comparator. For consistent switching of the comparator right at the desired threshold point, the voltage drop that occurs at the noninverting input (Threshold) must equal, or exceed, the rise in voltage at the inverting input (Sense).

A bypass capacitor across RREF is optional and is used to help keep the reference voltage constant in applications where the VCC supply is subject to high levels of transient noise. This bypass capacitor must be no larger than 0.1 µF, and is not needed for most applications.

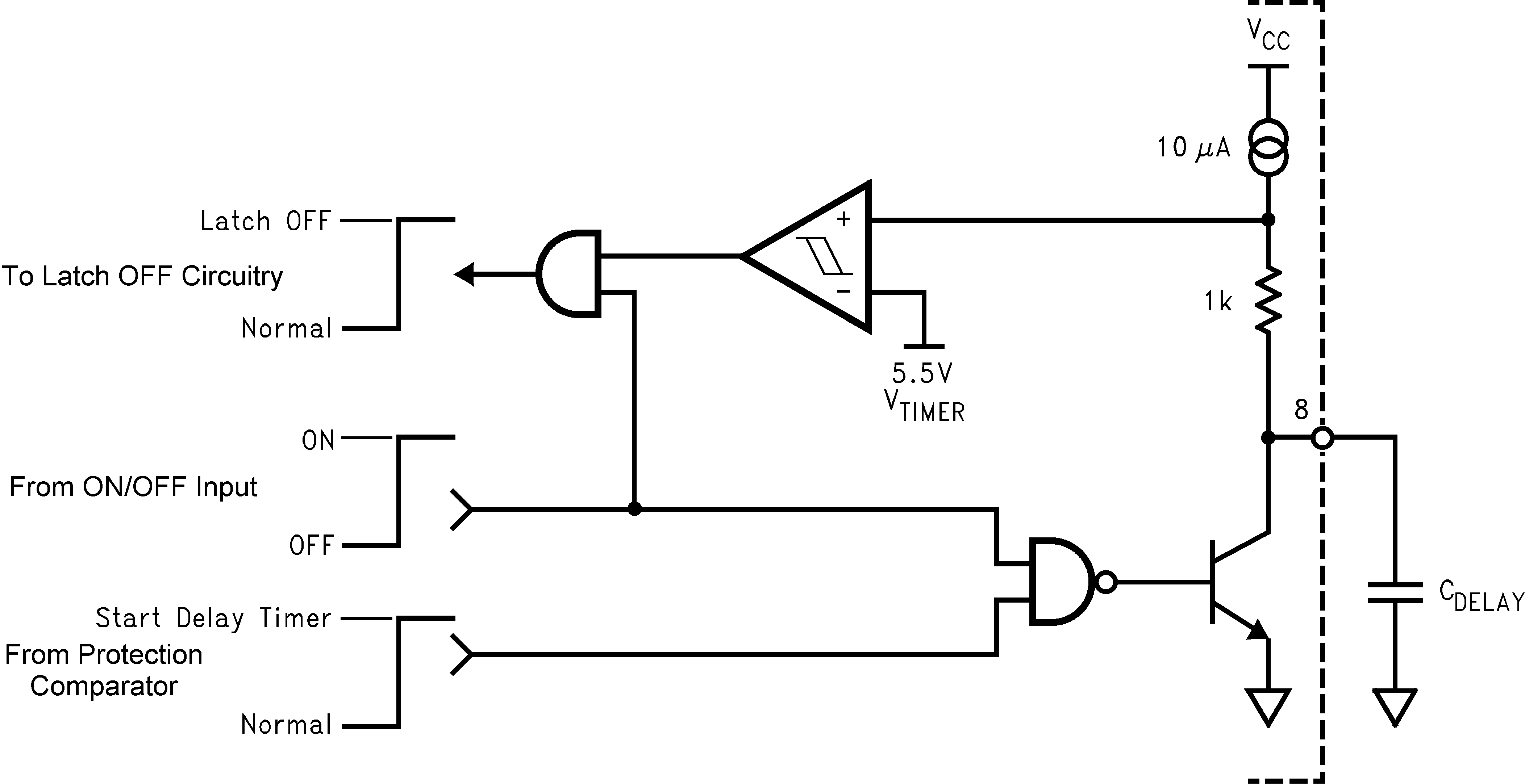

7.3.5 Delay Timer

To allow the MOSFET to conduct currents beyond the protection threshold for a brief period of time, a delay timer function is provided. This timer delays the actual latching OFF of the MOSFET for a programmable interval. This feature is important to drive loads which require a surge of current in excess of the normal ON current upon start-up, or at any point in time, such as lamps and motors. Figure 15 details the delay timer circuitry. A capacitor connected from the Delay pin 8, to ground sets the delay time interval. With the MOSFET turned ON and all conditions normal, the output of the protection comparator is low and this keeps the discharge transistor ON. This transistor keeps the delay capacitor discharged. If a surge of load current trips the protection comparator high, the discharge transistor turns off and an internal 10-µA current source begins linearly charging the delay capacitor.

If the surge current, with excessive VDS voltage, lasts long enough for the capacitor to charge to the timing comparator threshold of typically 5.5 V, the output of the comparator goes high to set a flip-flop and immediately latch the MOSFET OFF. It does not restart until the ON/OFF Input is toggled low then high.

The delay time interval is set by the selection of CDELAY and can be found in Equation 6:

where

- Typically, VTIMER = 5.5 V.

- IDELAY = 10 µA.

Charging of the delay capacitor is clamped at approximately 7.5 V which is the internal bias voltage for the 10-µA current source.

Figure 15. Delay Timer

Figure 15. Delay Timer

7.3.5.1 Minimum Delay Time

A minimum delay time interval is required in all applications due to the nature of the protection circuitry. At the instant the MOSFET is commanded ON, the voltage across the MOSFET, VDS, is equal to the full load supply voltage because the source is held at ground by the load. This condition immediately trips the protection comparator. Without a minimum delay time set, the timing comparator trips and forces the MOSFET to latch-OFF thereby never allowing the load to be energized.

To prevent this situation a delay capacitor is required at pin 8. The selection of a minimum capacitor value to ensure proper start-up depends primarily on the load characteristics and how much time is required for the MOSFET to raise the load voltage to the point where the Sense input is more positive than the Threshold input (TSTART-UP). Some experimentation is required if a specific minimum delay time characteristic is desired (see Equation 7).

In the absence of a specific delay time requirement, TI recommends a value for CDELAY of 0.1 µF.

7.3.6 Overvoltage Protection

The LM9061 remains operational with up to +26 V on VCC. If VCC increases to more than typically +30 V the LM9061 will turn off the MOSFET to protect the load from excessive voltage. When VCC has returned to the normal operating range the device will return to normal operation without requiring toggling the ON/OFF input. This feature allows MOSFET operation to continue in applications that are subject to periodic voltage transients, such as automotive applications.

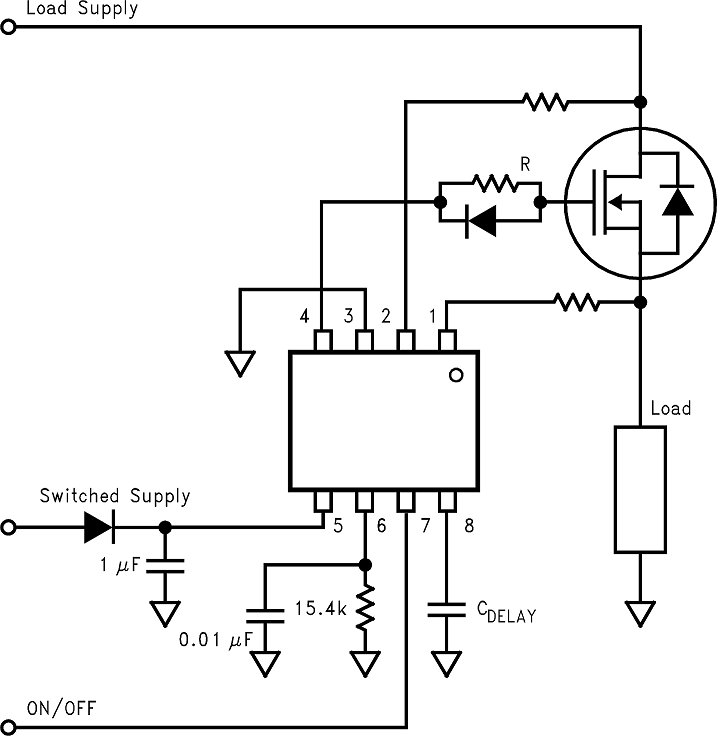

For circuits where the load is sensitive to high voltages, the circuit shown in Figure 16 can be used. The addition of a Zener on the Sense input (pin 1) provides a maximum voltage reference for the Protection Comparator. The Sense resistor is required in this application to limit the Zener current. When the device is ON, and the load supply attempts to rise higher than (VZENER + VTHRESHOLD), the Protection comparator trips, and the Delay Timer starts. If the high supply voltage condition lasts long enough for the Delay Timer to time out, the MOSFET is latched off. The ON/OFF input must be toggled to restart the MOSFET.

Figure 16. Adding Overvoltage Protection

Figure 16. Adding Overvoltage Protection

7.3.7 Reverse Battery

If the VCC supply must be taken negative with respect to ground, the current from the VCC pin must be limited to 20 mA. The addition of a diode in series with the VCC input is recommended. This diode drop does not subtract significantly from the charge pump gate overdrive output voltage.

7.3.8 Low Battery

An additional feature of the LM9061 is an Undervoltage Shutoff function (UVSO). The typical UVSO threshold is 6.2 V, and does not have hysteresis. When VCC is between the ensured minimum operating voltage of 7 V, and the UVSO threshold, the operation of the MOSFET gate drive, the delay timer, and the protection circuitry is not ensured. Operation in this region must be avoided. When VCC falls below the UVSO threshold, the charge pump is disabled and the gate is discharged at the normal OFF current sink rate, typically 110 μA.

Figure 17 shows the LM9061 used as an electronic circuit breaker. This circuit provides low voltage shutdown, overvoltage latch-OFF, and overcurrent latch-OFF.

The low voltage shutdown uses the ON and OFF voltage thresholds, and the typical 1.2 V of hysteresis, to disable the LM9061 if VCC falls near, or below, the 7 V minimum operating voltage. The low voltage shutdown is accomplished with a voltage divider biased off VCC. The voltage divider is formed by R1 (30 kΩ), R2 (82 kΩ), and the internal pulldown resistor of the ON/OFF pin (30 kΩ typical). In normal operation, VCC is above the minimum operating voltage of 7 V, and the ON/OFF pin is biased above the OFF threshold of 1.5-V maximum (1.8-V typical). When VCC falls to 7 V the ON/OFF pin voltage falls below the OFF threshold voltage and the LM9061 is turned off.

In the event of a latch-OFF shutdown, the circuit can be reset by shutting the main supply off, then back on. An optional, normally open, switch (Clear) from the ON/OFF pin to ground, allows a push button clear of the circuit after latching OFF.

Figure 17. Electronic Circuit Breaker

Figure 17. Electronic Circuit Breaker

This voltage divider arrangement requires a mechanism to raise the ON/OFF pin above the ON threshold of 3.5-V minimum (3.1-V typical) when VCC is less than typically 16 V. This can be accomplished with a second, normally open, switch from the ON/OFF pin across R2 (Set), so that closing the switch shorts R2 and the voltage at the ON/OFF pin is typically one-half of VCC. When VCC is at the minimum operating voltage of 7 V this biases the ON/OFF pin to about 3.5 V, causing the LM9061 to turn on. When VCC is above typically 16.5 V, the resistor divider has the ON/OFF pin biased above 3.5 V and shorting of the resistor R2 is not be needed.

While the scaling of the external resistor values between VCC and the ON/OFF input pin, against the internal

30-kΩ resistor, can be used to increase the start-up voltage, it is important that the resistor ratio always has the ON/OFF pin biased below the OFF threshold (1.5 V) when VCC falls below the minimum operating voltage of 7 V.

The accuracy of this voltage divider arrangement is affected by normal manufacturing variations of the ON and OFF voltage thresholds and the value of internal resistor at the ON/OFF pin. If any application needs to detect with greater precision when VCC is near to 7 V, an external voltage monitor must be used to drive the ON/OFF pin. The external voltage monitor would also eliminate both the need for the switch to short R2 to start the LM9061, as well as R2.

7.3.9 Increasing MOSFET Turnon Time

The ability of the LM9061 to quickly turn on the MOSFET is an important factor in the management of the MOSFET power dissipation. Exercise caution when trying to increase the MOSFET turnon time by limiting the Gate drive current. The MOSFET average dissipation, and the LM9061 Delay time, must be recalculated with the extended switching transition time.

Figure 18 shows a method of increasing the MOSFET turnon time, without affecting the turnoff time. In this method the Gate is charged at an exponential rate set by the added external Gate resistor and the MOSFET Gate capacitances.

Figure 18. Increasing MOSFET Turnon Time

Figure 18. Increasing MOSFET Turnon Time

7.4 Device Functional Modes

7.4.1 Operation With VCC > 30 V

If VCC increases to more than typically 30 V, the LM9061 turns off the MOSFET to protect the load from excessive voltage. When VCC has returned to the normal operating range, the device returns to normal operation without requiring toggling the ON/OFF input. This feature allows MOSFET operation to continue in applications that are subject to periodic voltage transients, such as automotive applications.

7.4.2 Operation With VCC < 6.2 V

When VCC falls below the UVSO threshold of 6.2 V, the charge pump is disabled and the gate is discharged at the normal OFF current sink rate, typically 110 μA.

7.4.3 Operation With ON/OFF Control

In the ON state, the charge pump voltage, which is well above the available VCC supply, is directly applied to the gate of the MOSFET. When commanded OFF a 110-µA current sink discharges the gate capacitances of the MOSFET for a gradual turnoff characteristic to minimize the duration of inductive load transient voltages and further protect the power MOSFET.

7.4.4 MOSFET Latch-OFF

In the event of excessive power dissipation in the MOSFET as detected by the LM9061 sense and threshold pins, the MOSFET is latched OFF to prevent permanent failure. It does not restart until the ON/OFF Input is toggled low then high.