SNOS674J October 1997 – September 2024 LMC6482 , LMC6484

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|8

- P|8

- DGK|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6.3.2 Input Common-Mode Voltage Range

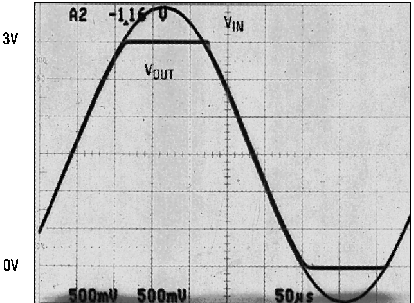

Unlike Bi-FET amplifier designs, the LMC648x do not exhibit phase inversion when an input voltage exceeds the negative supply voltage. Figure 6-2 shows an input voltage exceeding both supplies with no resulting phase inversion on the output.

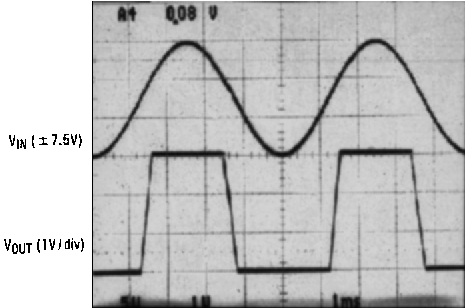

The absolute maximum input voltage is 300mV beyond either supply rail at room temperature. Voltages greatly exceeding this absolute maximum rating, as in Figure 6-3, can cause excessive current to flow in or out of the input pins possibly affecting reliability.

| An input voltage signal exceeds the LMC6482 power supply voltages with no output phase inversion. | ||

| A ±7.5‑V input signal greatly exceeds the 3‑V supply in Figure 6-4 causing no phase inversion due to Ri. | ||

Applications that exceed this rating must externally limit the maximum input current to ±5mA with an input resistor (Ri) as shown in Figure 6-4.