SNOS674J October 1997 – September 2024 LMC6482 , LMC6484

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|14

- N|14

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7.2.1.2.1 Capacitive Load Compensation

The LMC648x provides a robust output stage for directly driving capacitive loads. Capacitive loads interact with the output impedance of the amplifier to create a pole that can cause instability. When driving capacitive loads, consider the closed-loop bandwidth and output impedance of the amplifier. The LMC648x open-loop output impedance is shown in Figure 7-7.

Figure 7-7 Open-Loop Output

Impedance

Figure 7-7 Open-Loop Output

ImpedanceIn some applications, driving large capacitive loads is required and additional compensation is necessary. Capacitive load compensation can be accomplished using resistive isolation as shown in Figure 7-8. This simple technique is useful for isolating the capacitive inputs of multiplexers and analog-to-digital converters (ADCs).

Figure 7-8 Resistive Isolation of a

330pF Capacitive Load

Figure 7-8 Resistive Isolation of a

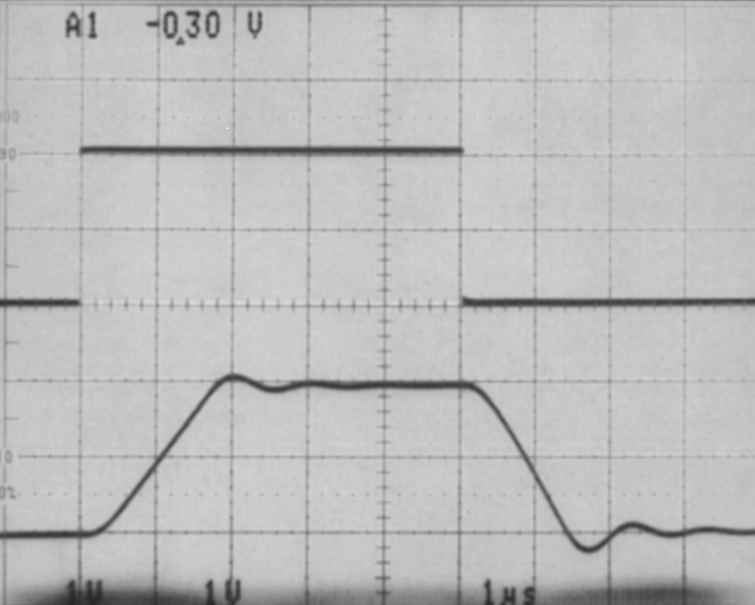

330pF Capacitive Load Figure 7-9 Pulse Response of the

LMC6482 Circuit in Figure 7-8

Figure 7-9 Pulse Response of the

LMC6482 Circuit in Figure 7-8