SNLS568D March 2017 – May 2020 LMH1228

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 4-Level Input Pins and Thresholds

- 7.3.2 OUT0_SEL and SDI_OUT2_SEL Control

- 7.3.3 Input Signal Detect

- 7.3.4 Continuous Time Linear Equalizer (CTLE)

- 7.3.5 Clock and Data (CDR) Recovery

- 7.3.6 Internal Eye Opening Monitor (EOM)

- 7.3.7 Output Function Control

- 7.3.8 Output Driver Control

- 7.3.9 Status Indicators and Interrupts

- 7.4 Device Functional Modes

- 7.5 Register Maps

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RTV|32

Thermal pad, mechanical data (Package|Pins)

- RTV|32

Orderable Information

7.3.6 Internal Eye Opening Monitor (EOM)

The LMH1228 has an on-chip eye opening monitor (EOM) that can be used to analyze, monitor, and diagnose the post-equalized waveform, just prior to the CDR reclocker. The EOM is operational for 2.97 Gbps and higher data rates.

The EOM monitors the post-equalized waveform in a time window that spans one unit interval and a configurable voltage range that spans up to ±400 mV. The time window and voltage range are divided into 64 steps, so the result of the eye capture is a 64 × 64 matrix of hits, where each point represents a specific voltage and phase offset relative to the main data sampler. The number of hits registered at each point needs to be taken in context with the total number of bits observed at that voltage and phase offset to determine the corresponding probability for that point.

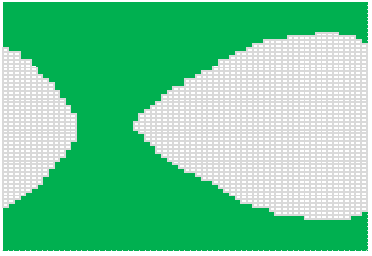

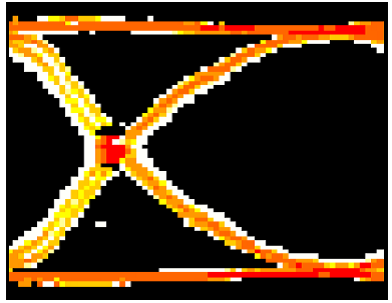

The resulting 64 × 64 matrix produced by the EOM can be processed by software and visualized in a number of ways. Two common ways to visualize this data are shown in Figure 10 and Figure 11. These diagrams depict examples of eye monitor plots implemented by software. The first plot is an example using the EOM data to plot a basic eye using ASCII characters, which can be useful for diagnostic software. The second plot shows the first derivative of the EOM data, revealing the density of hits and the actual waveforms and crossings that comprise the eye.

Figure 10. Internal Input Eye Monitor Plot

Figure 10. Internal Input Eye Monitor Plot  Figure 11. Internal Eye Monitor Hit Density Plot

Figure 11. Internal Eye Monitor Hit Density Plot A common measurement performed by the EOM is the horizontal and vertical eye opening. The horizontal eye opening (HEO) represents the width of the post-equalized eye at 0-V differential amplitude, measured in unit intervals or picoseconds (ps). The vertical eye opening (VEO) represents the height of the post-equalized eye, measured midway between the mean zero crossing of the eye. This position in time approximates the CDR sampling phase. HEO and VEO measurements can be read back through register control.