SNAS579G March 2012 – December 2014 LMK00105

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Diagrams

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- RTW|24

Thermal pad, mechanical data (Package|Pins)

Orderable Information

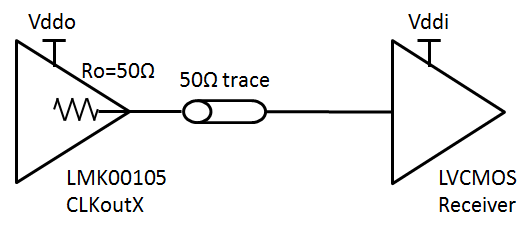

8.1.2 Clock Outputs

The LMK00105 LVCMOS driver output impedance (Ro) is nominally 50 ohms and well-matched to drive a 50 ohm transmission line (Zo), as shown as below. If driving a transmission line with higher characteristic impedance than 50 ohms, a series resistor (Rs) should be placed near the driver to provide source termination, where Rs = Zo – Ro.

The LMK00105 has two output banks, Bank A and Bank B, which are separately powered by independent Vddo supply pins. The Vddo supply pins for Bank A and Bank B are not connected together internally, and may be supplied with different voltages. This allows the LMK00105 outputs to easily interface to multiple receivers with different input threshold or input supply voltage (Vddi) requirements without the need for additional voltage divider networks.

Figure 9. LMK00105 Output Termination

Figure 9. LMK00105 Output Termination