SNAS841 October 2023 LMK04714-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 Register Map for Device Programming

- 8.6.2

Device Register Descriptions

- 8.6.2.1 System Functions

- 8.6.2.2

(0x100 to 0x137) Device Clock and SYSREF Clock Output

Controls

- 8.6.2.2.1 DCLKX_Y_DIV

- 8.6.2.2.2 DCLKX_Y_DDLY

- 8.6.2.2.3 CLKoutX_Y_PD, CLKoutX_Y_ODL, CLKoutX_Y_IDL, DCLKX_Y_DDLY_PD, DCLKX_Y_DDLY[9:8], DCLKX_Y_DIV[9:8]

- 8.6.2.2.4 CLKoutX_SRC_MUX, DCLKX_Y_PD, DCLKX_Y_BYP, DCLKX_Y_DCC, DCLKX_Y_POL, DCLKX_Y_HS

- 8.6.2.2.5 CLKoutY_SRC_MUX, SCLKX_Y_PD, SCLKX_Y_DIS_MODE, SCLKX_Y_POL, SCLKX_Y_HS

- 8.6.2.2.6 SCLKX_Y_ADLY_EN, SCLKX_Y_ADLY

- 8.6.2.2.7 SCLKX_Y_DDLY

- 8.6.2.2.8 CLKoutY_FMT, CLKoutX_FMT

- 8.6.2.3

SYSREF, SYNC, and Device Config

- 8.6.2.3.1 VCO_MUX, OSCout_MUX, OSCout_FMT

- 8.6.2.3.2 SYSREF_REQ_EN, SYNC_BYPASS, SYSREF_MUX

- 8.6.2.3.3 SYSREF_DIV

- 8.6.2.3.4 SYSREF_DDLY

- 8.6.2.3.5 SYSREF_PULSE_CNT

- 8.6.2.3.6 PLL2_RCLK_MUX, PLL2_NCLK_MUX, PLL1_NCLK_MUX, FB_MUX, FB_MUX_EN

- 8.6.2.3.7 PLL1_PD, VCO_LDO_PD, VCO_PD, OSCin_PD, SYSREF_GBL_PD, SYSREF_PD, SYSREF_DDLY_PD, SYSREF_PLSR_PD

- 8.6.2.3.8 DDLYdSYSREF_EN, DDLYdX_EN

- 8.6.2.3.9 DDLYd_STEP_CNT

- 8.6.2.3.10 SYSREF_CLR, SYNC_1SHOT_EN, SYNC_POL, SYNC_EN, SYNC_PLL2_DLD, SYNC_PLL1_DLD, SYNC_MODE

- 8.6.2.3.11 SYNC_DISSYSREF, SYNC_DISX

- 8.6.2.3.12 PLL1R_SYNC_EN, PLL1R_SYNC_SRC, PLL2R_SYNC_EN, FIN0_DIV2_EN, FIN0_INPUT_TYPE

- 8.6.2.4

(0x146 - 0x149) CLKIN Control

- 8.6.2.4.1 CLKin_SEL_PIN_EN, CLKin_SEL_PIN_POL, CLKin2_EN, CLKin1_EN, CLKin0_EN, CLKin2_TYPE, CLKin1_TYPE, CLKin0_TYPE

- 8.6.2.4.2 CLKin_SEL_AUTO_REVERT_EN, CLKin_SEL_AUTO_EN, CLKin_SEL_MANUAL, CLKin1_DEMUX, CLKin0_DEMUX

- 8.6.2.4.3 CLKin_SEL0_MUX, CLKin_SEL0_TYPE

- 8.6.2.4.4 SDIO_RDBK_TYPE, CLKin_SEL1_MUX, CLKin_SEL1_TYPE

- 8.6.2.5 RESET_MUX, RESET_TYPE

- 8.6.2.6

(0x14B - 0x152) Holdover

- 8.6.2.6.1 LOS_TIMEOUT, LOS_EN, TRACK_EN, HOLDOVER_FORCE, MAN_DAC_EN, MAN_DAC[9:8]

- 8.6.2.6.2 MAN_DAC

- 8.6.2.6.3 DAC_TRIP_LOW

- 8.6.2.6.4 DAC_CLK_MULT, DAC_TRIP_HIGH

- 8.6.2.6.5 DAC_CLK_CNTR

- 8.6.2.6.6 CLKin_OVERRIDE, HOLDOVER_EXIT_MODE, HOLDOVER_PLL1_DET, LOS_EXTERNAL_INPUT, HOLDOVER_VTUNE_DET, CLKin_SWITCH_CP_TRI, HOLDOVER_EN

- 8.6.2.6.7 HOLDOVER_DLD_CNT

- 8.6.2.7 (0x153 - 0x15F) PLL1 Configuration

- 8.6.2.8 (0x160 - 0x16E) PLL2 Configuration

- 8.6.2.9 (0x16F - 0x555) Misc Registers

-

9 Application and Implementation

- 9.1 Application Information

- 9.2 Typical Application

- 9.3 System Examples

- 9.4 Power Supply Recommendations

- 9.5 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PAP|64

Thermal pad, mechanical data (Package|Pins)

- PAP|64

Orderable Information

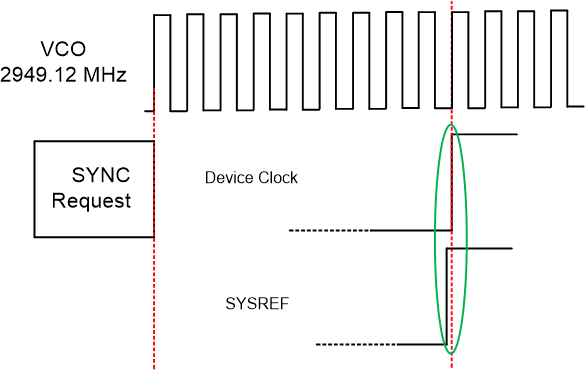

8.3.5 SYSREF to Device Clock Alignment

To ensure proper JESD204B/C operation, the timing relationship between the SYSREF and the Device clock must be adjusted for optimum setup and hold time as shown in Figure 8-6. The global SYSREF digital delay (SYSREF_DDLY), local SYSREF digital delay (SCLKX_Y_DDLY), local SYSREF half step (SCLKX_Y_HS), and local SYSREF analog delay (SCLKX_Y_ADLY, SCLK2_3_ADLY_EN) can be adjusted to provide the required setup and hold time between SYSREF and Device Clock. It is also possible to adjust the device clock digital delay (DCLKX_Y_DDLY) and half step (DCLK0_1_HS, DCLK0_1_DCC) to adjust phase with respect to SYSREF.

Figure 8-6 SYSREF to Device Clock Timing

Alignment

Figure 8-6 SYSREF to Device Clock Timing

AlignmentThe delay between clock and SYSREF is the difference between the delays for these paths.

| VARIABLE/FIELD | COMMENTS | EXAMPLE (fVCO = 2.5 GHz, DIVIDE = 6) |

|---|---|---|

|

ClockFixed Delay (DCLKX_Y_DDLY) |

ClockFixedDelay = 6000 ps (DCLK0_1_DDLY = 15) |

|

|

ClockFixedDelayCorrection |

Correction value when divide is less than 8.

|

ClockFixedDelayCorrection = –400 ps (–1 VCO Cycle) |

| ClockDutyCycleCorrect (DCLKX_Y_DCC) |

Adds one VCO cycle if enabled |

ClockDutyCycleCorrect = 400 (DCLKX_Y_DCC = 1) |

|

ClockDynamicDelay (dDLY_STEP_CNT) |

ClockDynamicDelay is the cumulative effect of programming dDLY_STEP_CNT. It is zero if the dynamic delay is disabled for the channel | ClockDynamicDigitalDelay = 0 (DDLYd0_EN = 0) |

| ClockHalfStep (DCLKX_Y_HS) |

This would be ½ of a VCO Cycle if enabled |

ClockHalfStep = 200 (DCLKX_Y_DCC = 1) |

| SysrefGlobalDelay (SYSREF_DDLY) |

SYSREF_DDLY≥8 for proper operation |

SysRefGlobalDelay = 4800 ps (SYSREF_DDLY = 12) |

| SysrefFixedDelay (SCLKX_Y_DDLY) |

This is the number of cycles represented by the delay | SysrefFixedDelay = 2 × 400 = 800 ps (SCLK0_1_DDLY = 1) |

|

SysrefHalfStep (SCLKX_Y_HS) |

The half step for the SYSREF is not exactly a half step, but rather about 60 ps less. |

SysrefHalfStep = 200 – 60 = 140 ps (SCLK0_1_HS = 1) |

|

SysrefAnalogDelay (SCLKX_Y_ADLY) |

This is the stated value in ps for the analog delay |

SysrefAnalogDelay = 230 ps (SCLK0_1_ADLY = 5) |

| TotalClockDelay = 6000 + (–400) + 400 – 200 + 0 = 5800 ps | ||

| TotalSysrefDelay = 80 + 400 + 4800 + 800 – 140 + 230 = 6170 ps | ||

| Clock to SYSREF Delay = 6170 – 5800 = 370 ps | ||