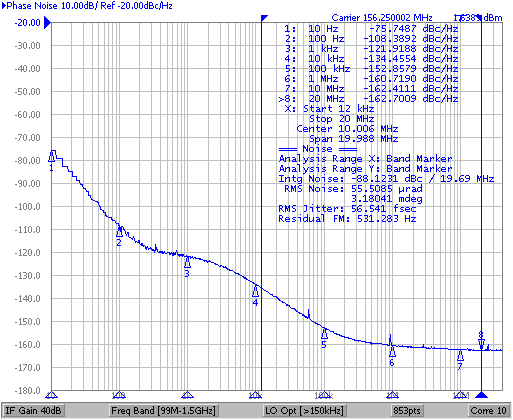

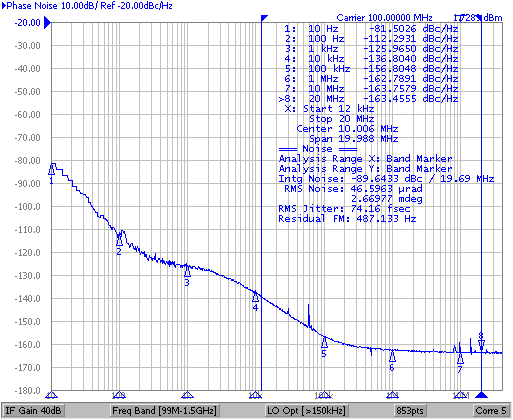

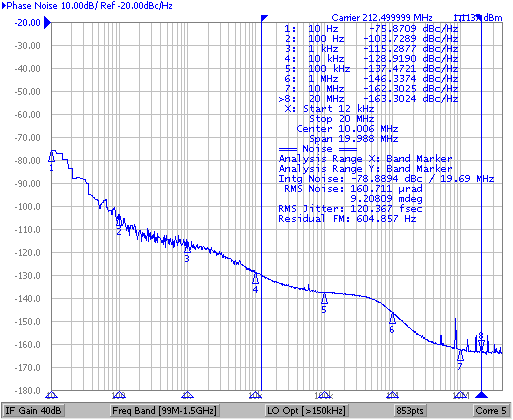

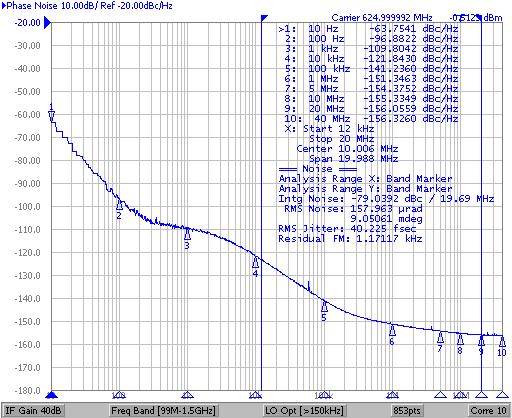

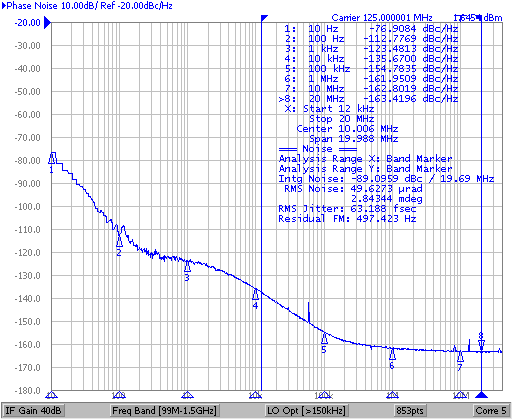

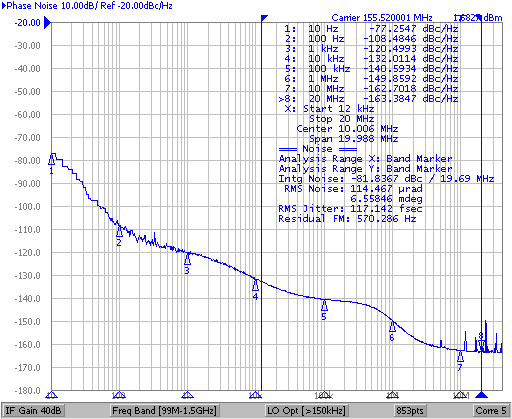

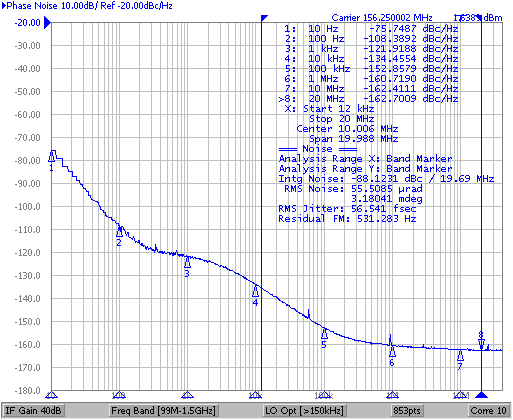

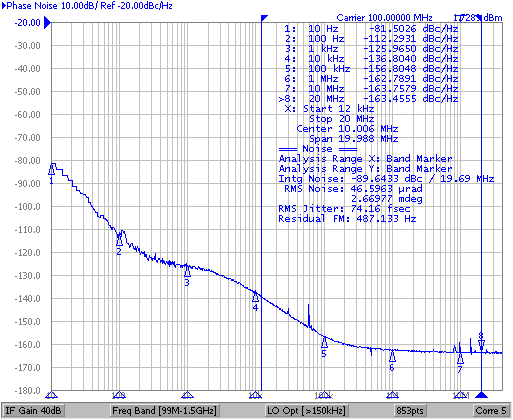

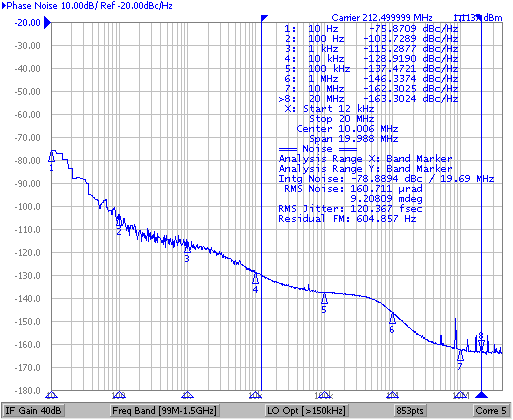

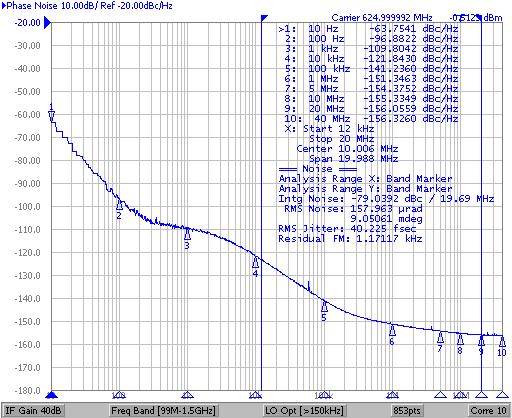

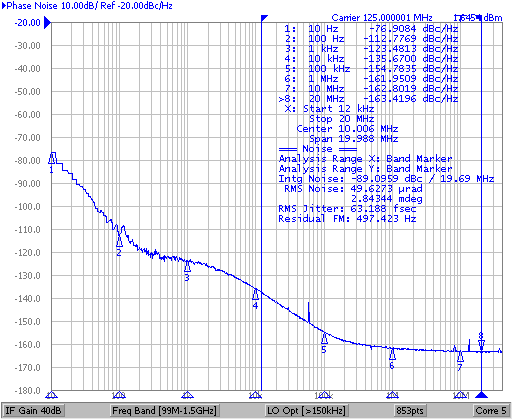

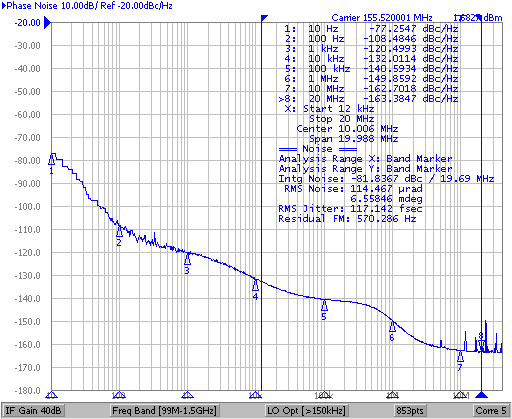

Unless otherwise noted: VDD = 3.3 V, VDDO = 1.8 V, TA = 25 °C, AC-LVPECL output measured. DPLL: fREF = 25 MHz, fTDC = 25 MHz, BWDPLL = 10 Hz, DPLL locked to reference. APLL1: fXO = 48.0048 MHz, fPD1 = 24.0024 MHz (fXO÷2), fVCO1 = 2500 MHz, BWAPLL1 = 2.5 kHz, DPLL mode. APLL2: fPD2 = 138.

8 MHz (fVCO1÷18), BWAPLL2 = 500 kHz, Cascaded APLL2 mode for Figure 7-9 and Figure 7-10.The PLL output clock phase noise at different frequency offsets are determined by different noise contributors, such as external clock input sources (REF IN, OCXO, XO) and internal noise sources (PLL, VCO), as well as the configured PLL loop bandwidths (BWREF-DPLL, BWTCXO-DPLL, BWAPLL). The phase noise profile shown for each external clock source (fSOURCE) was normalized to the PLL output frequency (fOUT) by adding 20×LOG10(fOUT / fSOURCE) to the measured phase noise of the source.

| Jitter = 40 fs RMS (12 kHz to 20 MHz) |

| DPLL Mode (APLL2 Disabled) |

| Jitter = 63 fs RMS (12 kHz to 20 MHz) |

| DPLL Mode (APLL2 Disabled) |

| Jitter = 117 fs RMS (12 kHz to 20 MHz) |

| DPLL Mode With Cascaded APLL2 |

| fVCO2 = 5598.72 MHz |

| 50-mVpp noise injected onto supplies (VDD = 3.3 V, VDDO = 3.3 V) |

Figure 7-13 Output Swing vs Frequency

Figure 7-13 Output Swing vs Frequency

| Jitter = 56 fs RMS (12 kHz to 20 MHz) |

| DPLL Mode (APLL2 Disabled) |

| Jitter = 74 fs RMS (12 kHz to 20 MHz) |

| DPLL Mode (APLL2 Disabled) |

| Jitter = 120 fs RMS (12 kHz to 20 MHz) |

| DPLL Mode With Cascaded APLL2 |

| fVCO2 = 5737.5 MHz |

| 25-mVpp noise injected onto supplies (VDD = 3.3 V, VDDO = 1.8 V) |

Figure 7-13 Output Swing vs Frequency

Figure 7-13 Output Swing vs Frequency