SLUSF64A August 2024 – November 2024 LMR51635

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Device Comparison Table

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DDC|6

Thermal pad, mechanical data (Package|Pins)

Orderable Information

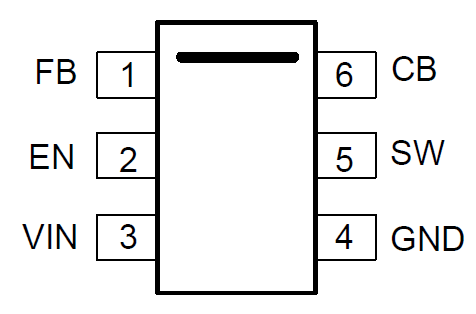

5 Pin Configuration and Functions

Figure 5-1 6-Pin

SOT-23-THN,DDC Package(Top View)

Figure 5-1 6-Pin

SOT-23-THN,DDC Package(Top View)Table 5-1 Pin Functions

| PIN | TYPE(1) | DESCRIPTION | |

|---|---|---|---|

| NAME | NO | ||

| FB | 1 | A | Feedback input to the converter. Connect a resistor divider to set the output voltage. Never short this terminal to ground during operation. |

| EN | 2 | A | Precision enable input to the converter. Do not float. High = On, low = Off. Can be tied to VIN. Precision enable input allows an adjustable UVLO by an external resistor divider. |

| VIN | 3 | P | Supply input pin to the internal bias LDO and high-side FET. Connect to the input supply and input bypass capacitors CIN. Input bypass capacitors must be directly connected to this pin and GND. |

| GND | 4 | G | Power ground pins. Connected to the source of low-side FET internally. Connect to system ground, ground side of CIN and COUT. The path to CIN must be as short as possible. |

| SW | 5 | P | Switching output of the converter. Internally connected to source of the high-side FET and drain of the low-side FET. Connect to the power inductor. |

| CB | 6 | P | Bootstrap capacitor connection for high-side FET driver. Connect a high quality 100nF capacitor from this pin to the SW pin. |

(1) A = Analog, P = Power, G = Ground