SNIS169F March 2013 – May 2024 LMT86

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Device Comparison

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8.2.2.3 Application Curves

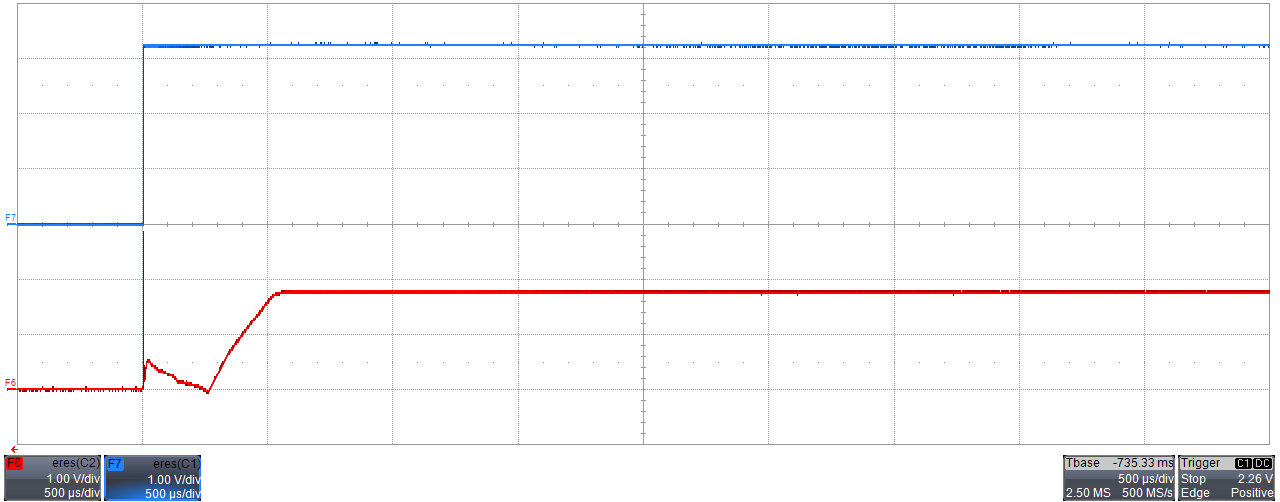

Time:

500 µs/div; Top Trace: VDD 1 V/div; Bottom Trace: OUT 1

V/div

Figure 8-4 Output Turnon Response Time Without a Capacitive Load and VDD =

3.3 V

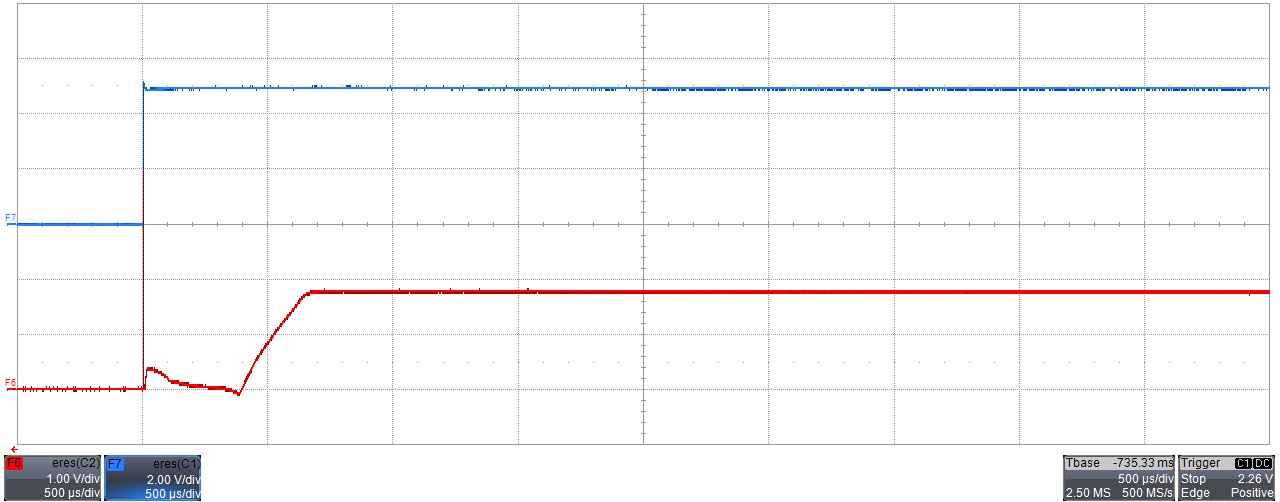

Time:

500 µs/div; Top Trace: VDD 2 V/div; Bottom Trace: OUT 1

V/div

Figure 8-6 Output Turnon Response Time Without a Capacitive Load and VDD =

5 V

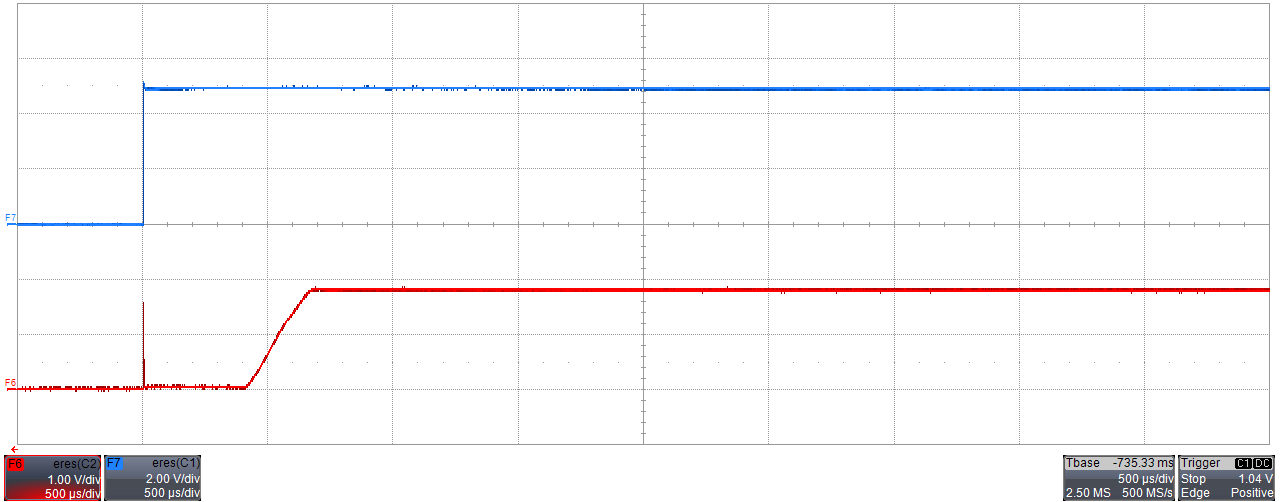

Time:

500 µs/div; Top Trace: VDD 1 V/div; Bottom Trace: OUT 1

V/div

Figure 8-5 Output Turnon Response Time With a 1.1-nF Capacitive Load and

VDD = 3.3 V

Time: 500 µs/div; Top Trace: VDD 2 V/div; Bottom Trace: OUT 1 V/div

Figure 8-7 Output Turnon Response Time With 1.1-nF Capacitive Load and VDD = 5 V