SNAS783C June 2020 – February 2021 LMX2820

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Reference Oscillator Input

- 7.3.2 Input Path

- 7.3.3 PLL Phase Detector and Charge Pump

- 7.3.4 N Divider and Fractional Circuitry

- 7.3.5 LD Pin Lock Detect

- 7.3.6 MUXOUT Pin and Readback

- 7.3.7 Internal VCO

- 7.3.8 Channel Divider

- 7.3.9 Output Frequency Doubler

- 7.3.10 Output Buffer

- 7.3.11 Power-Down Modes

- 7.3.12 Phase Synchronization for Multiple Devices

- 7.3.13 SYSREF

- 7.3.14 Fast VCO Calibration

- 7.3.15 Double Buffering (Shadow Registers)

- 7.3.16 Output Mute Pin and Ping Pong Approaches

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RTC|48

Thermal pad, mechanical data (Package|Pins)

- RTC|48

Orderable Information

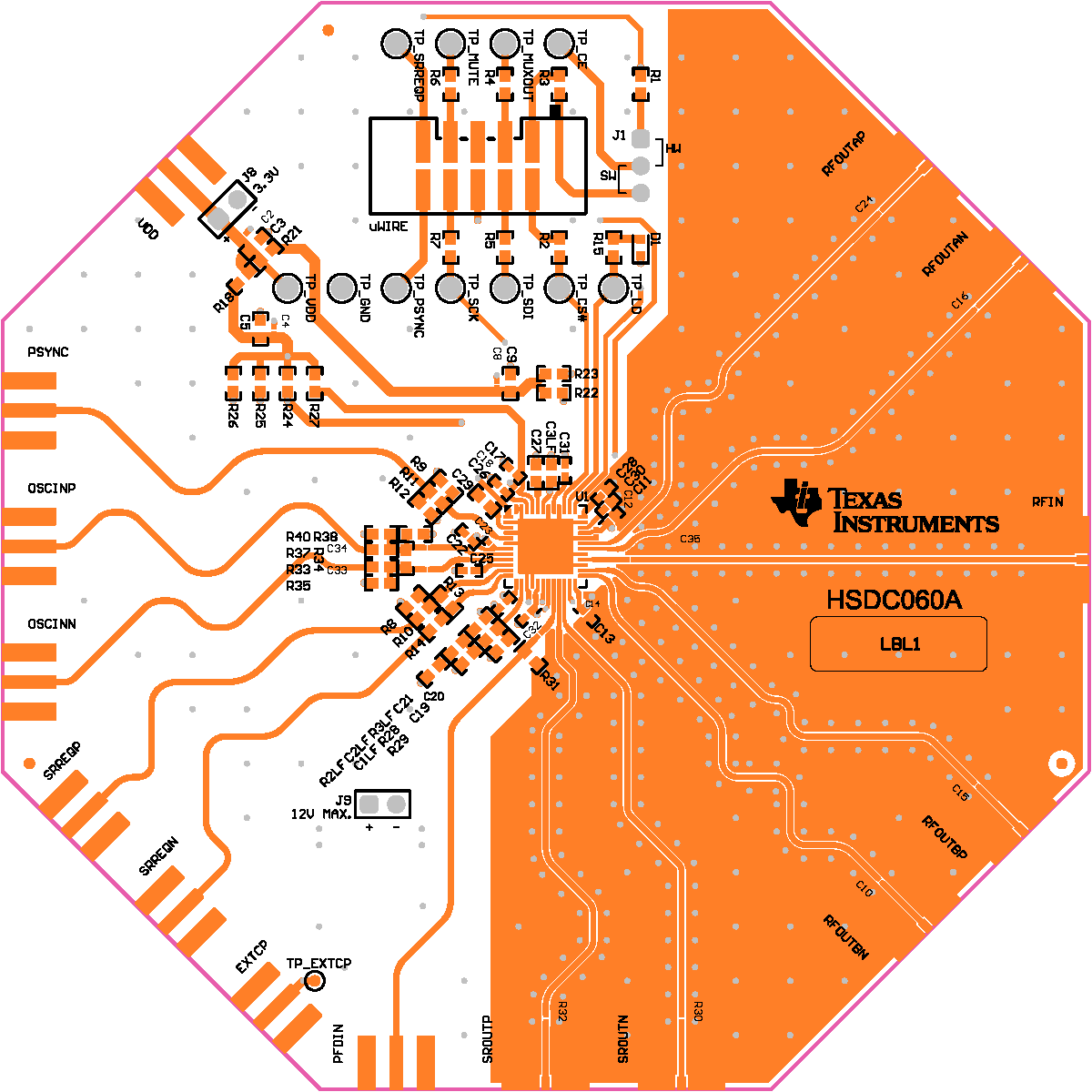

10.2 Layout Example

For this layout, all of the loop filter (C1LF, C2LF, C3LF, R2LF and R3LF) are on the top side of the board. C3LF is located right next to the VTUNE pin. In the event that this C3LF capacitor would be open, TI recommends to move one of loop capacitors in this spot. For instance, if a second order loop filter was used, technically C3LF would be open. However, for this layout example that is designed for a third order loop filter, it would be optimal to make C1LF = open, and C3LF to be whatever C1LF would have been.

Figure 10-1 Layout Example

Figure 10-1 Layout Example