at operating temperature TJ

= 25°C, VIN = VOUT(NOM) + 1.0 V or 2.5 V (whichever is

greater), IOUT = 1 mA, ON/OFF pin tied to

VIN, CIN = 1.0 µF, and COUT = 4.7 µF (unless

otherwise noted)

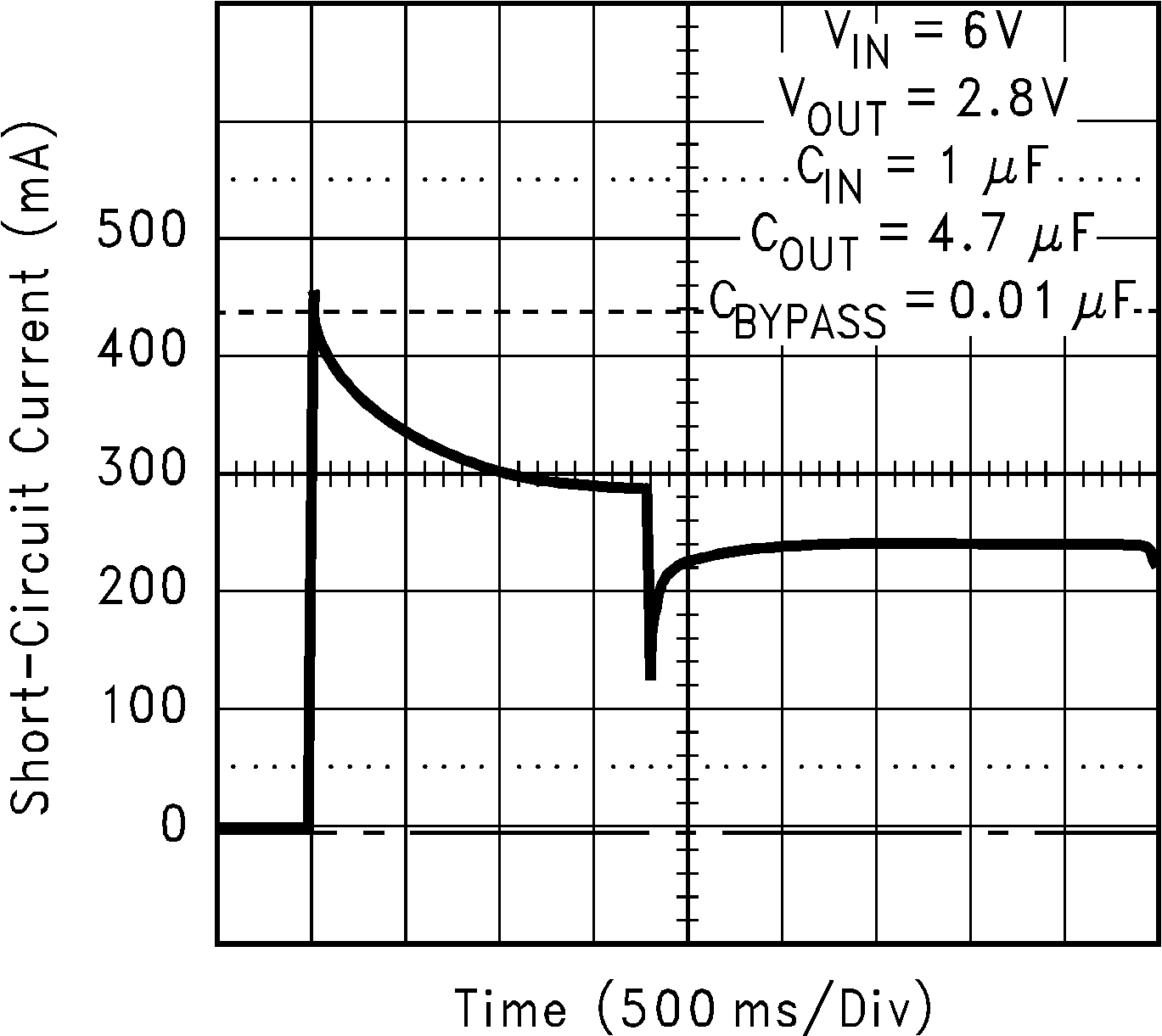

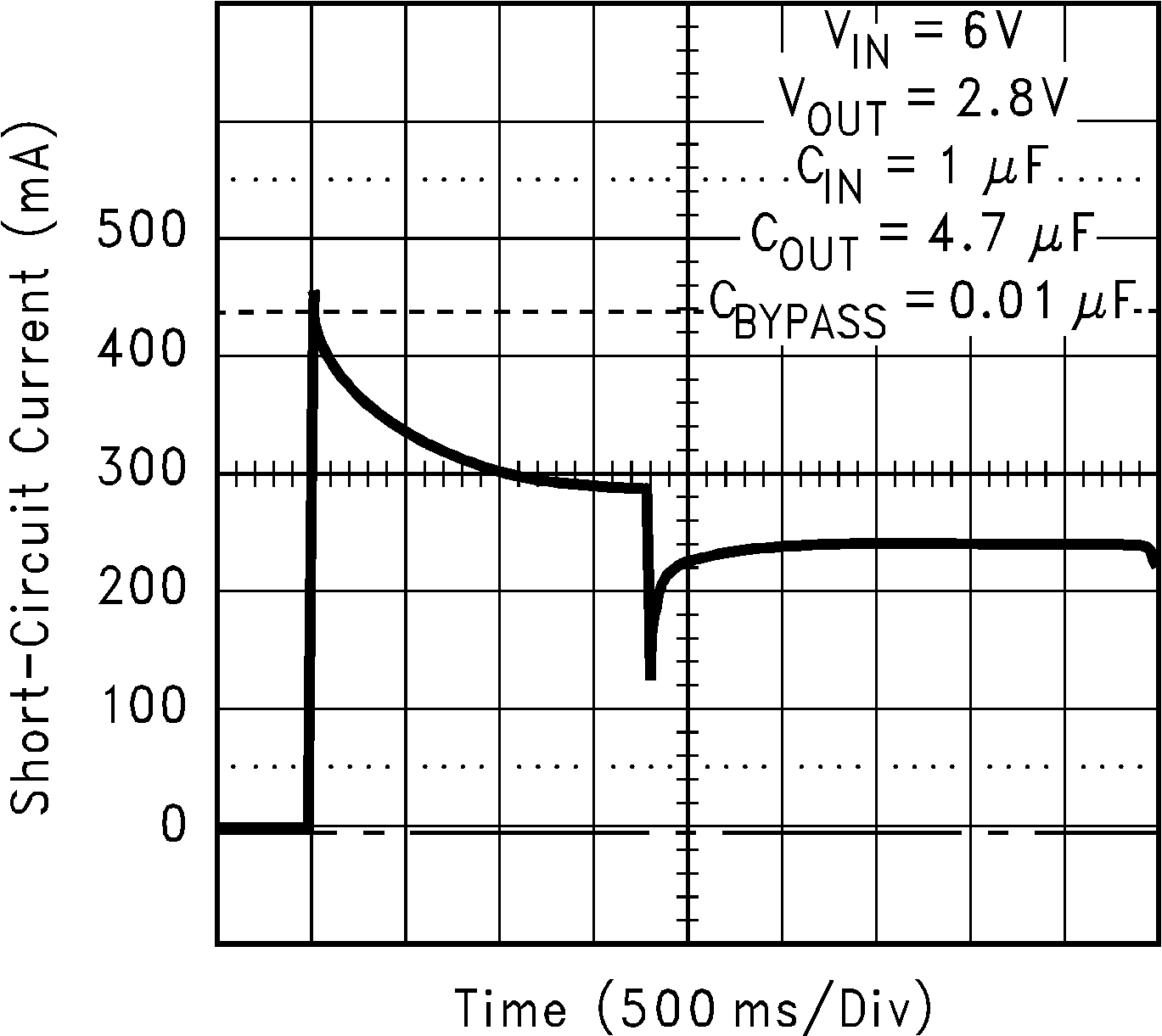

Figure 8-3 Short-Circuit Current for Legacy Chip at VIN = 6 V

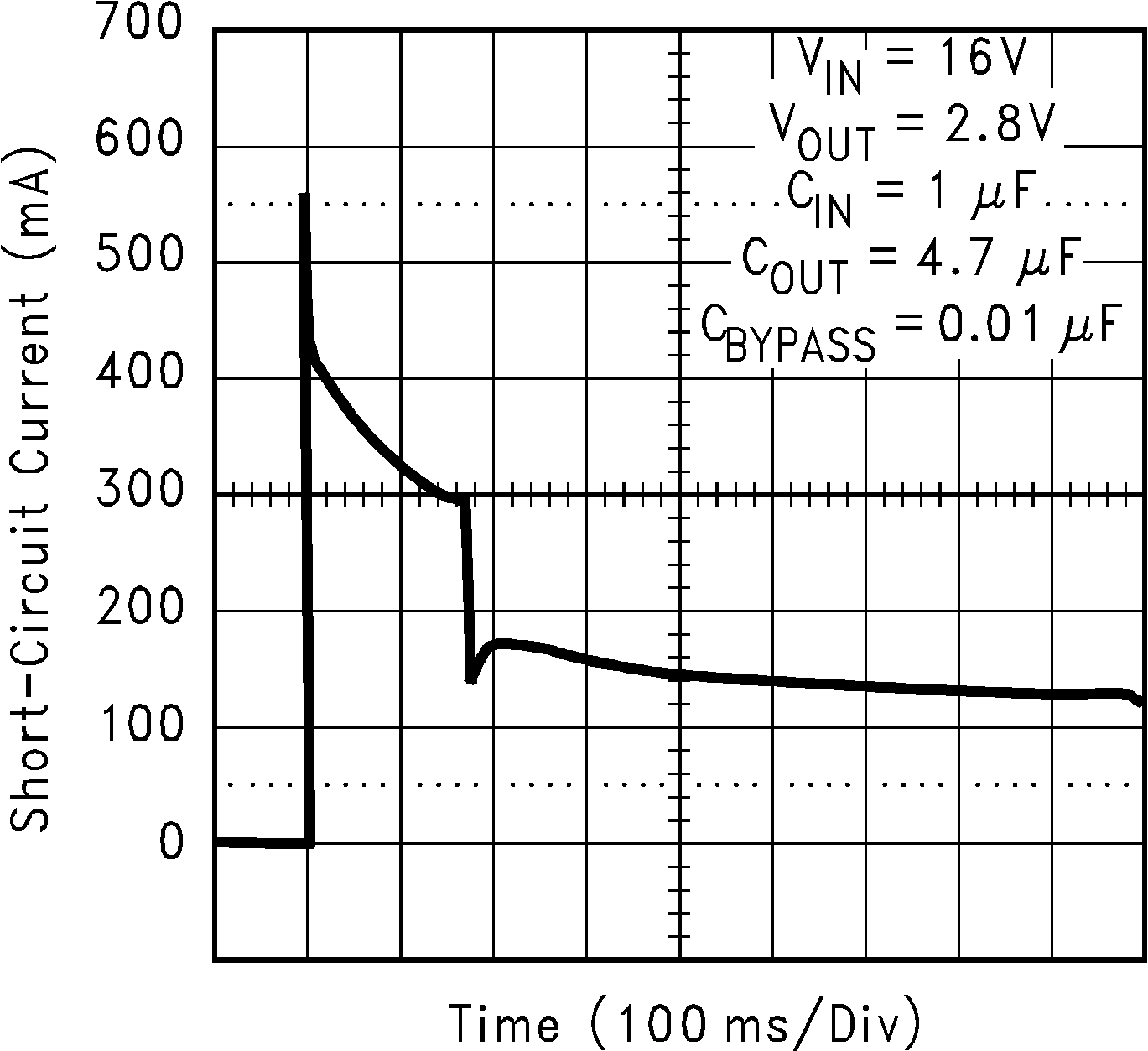

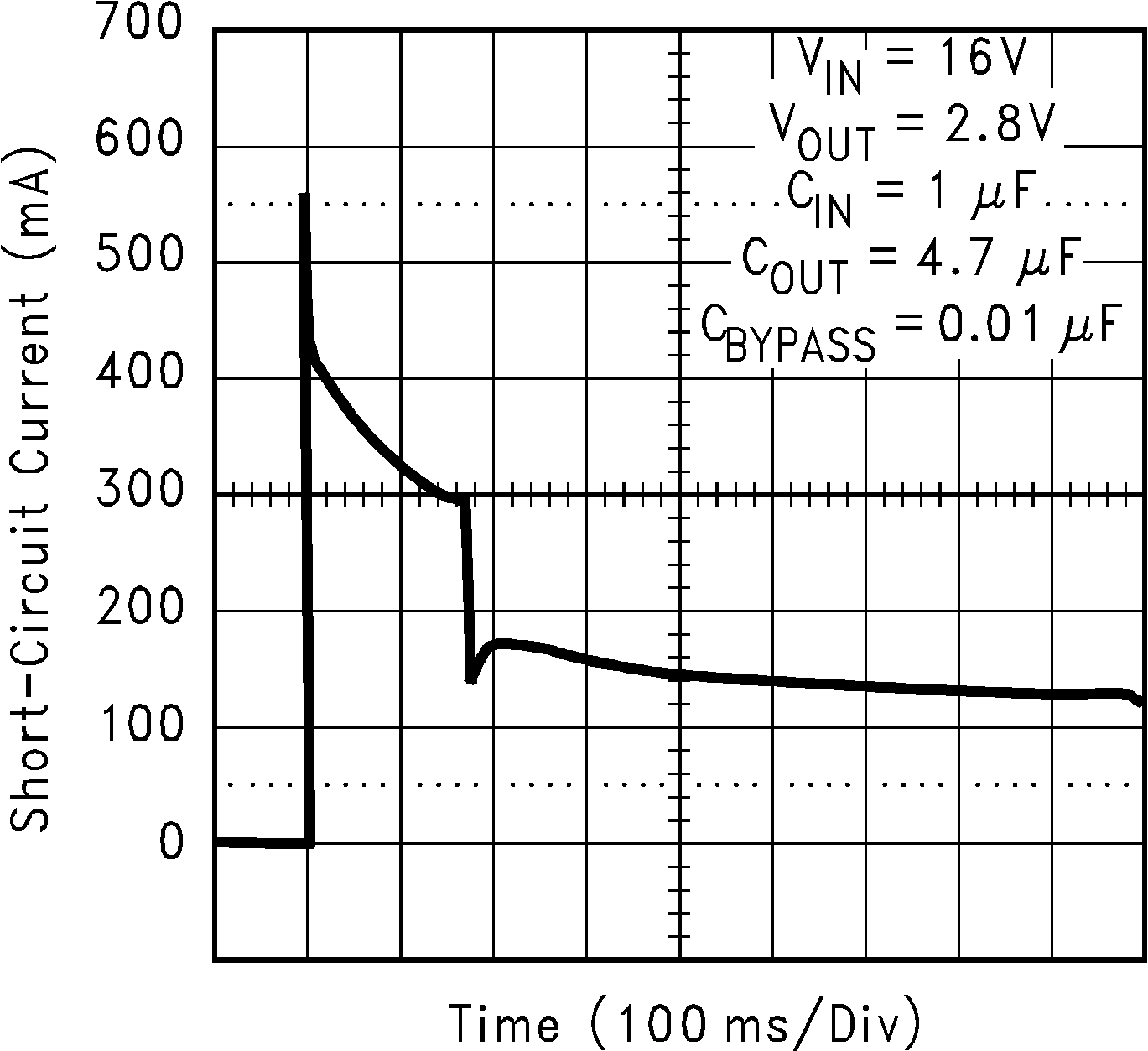

Figure 8-3 Short-Circuit Current for Legacy Chip at VIN = 6 V Figure 8-5 Short-Circuit Current for Legacy Chip at VIN = 16 V

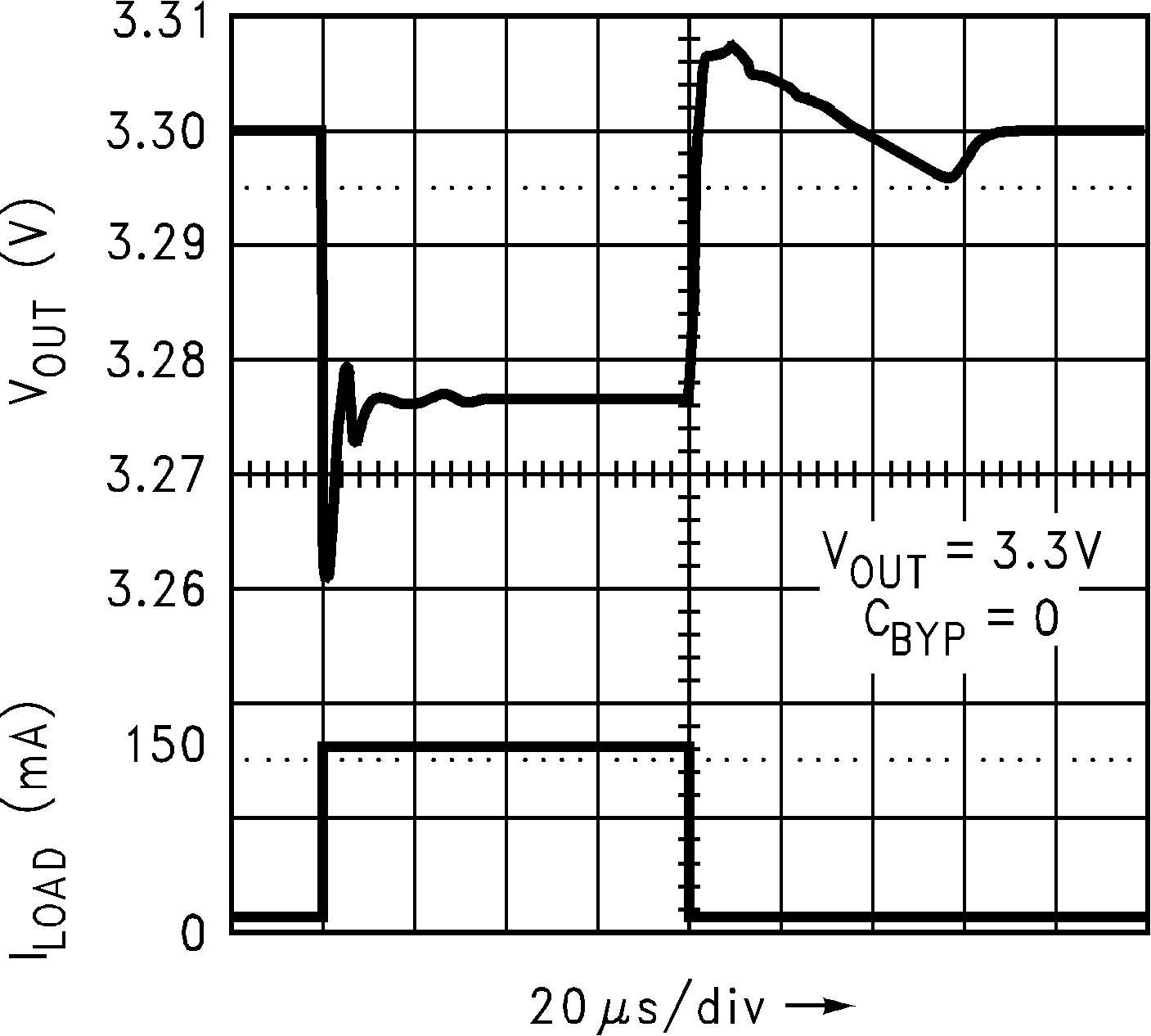

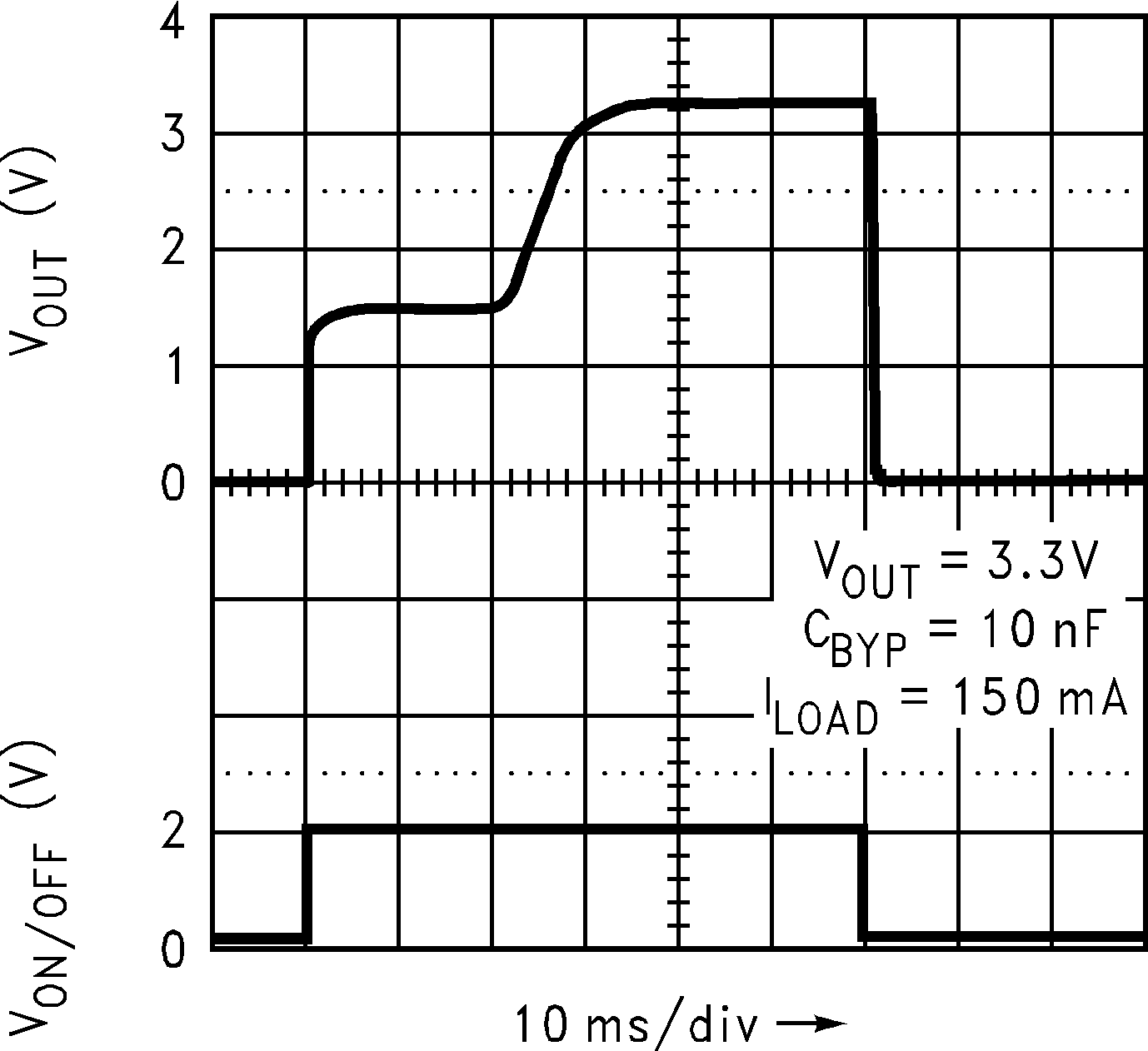

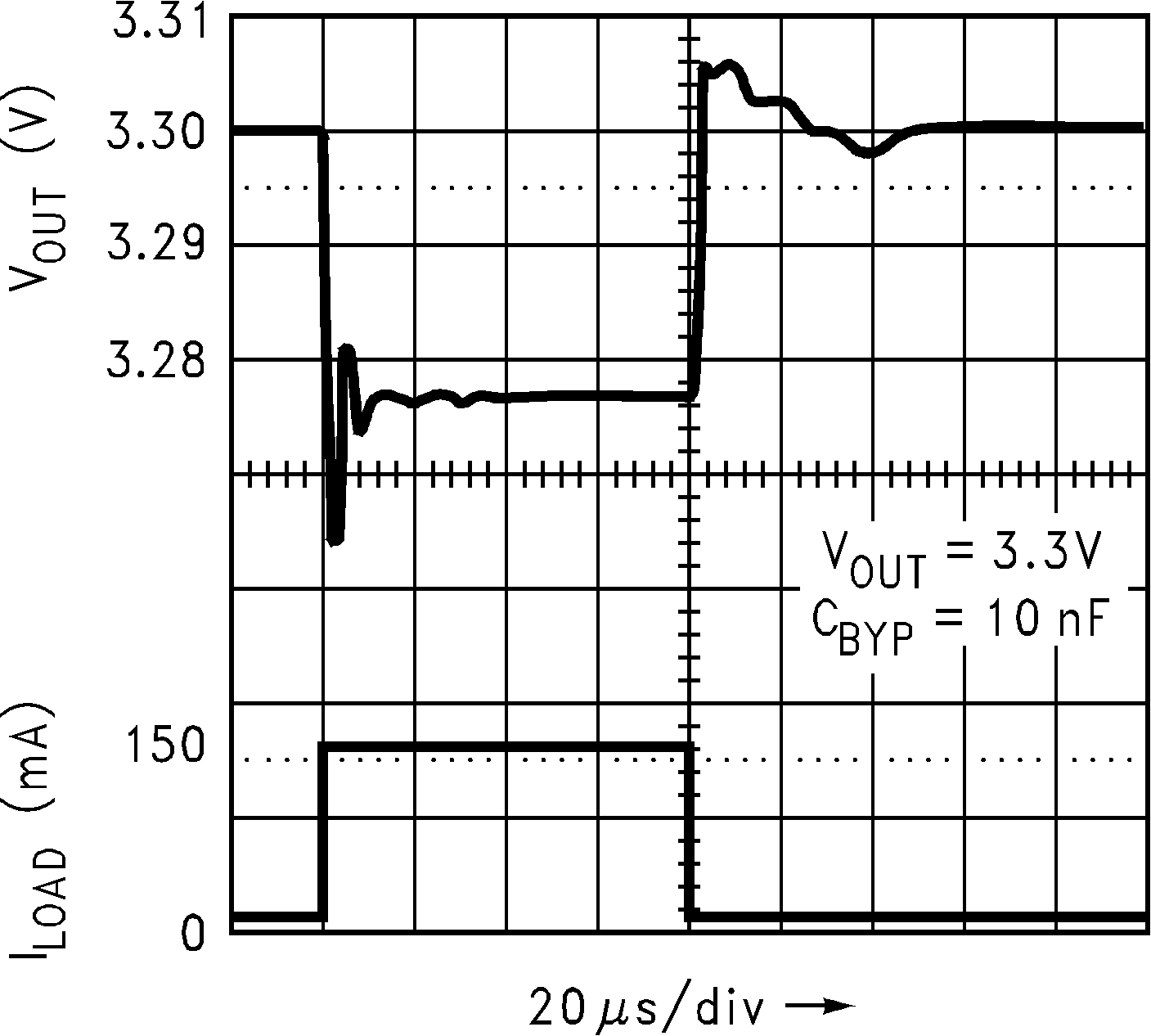

Figure 8-5 Short-Circuit Current for Legacy Chip at VIN = 16 V Figure 8-7 Load

Transient Response for Legacy Chip

Figure 8-7 Load

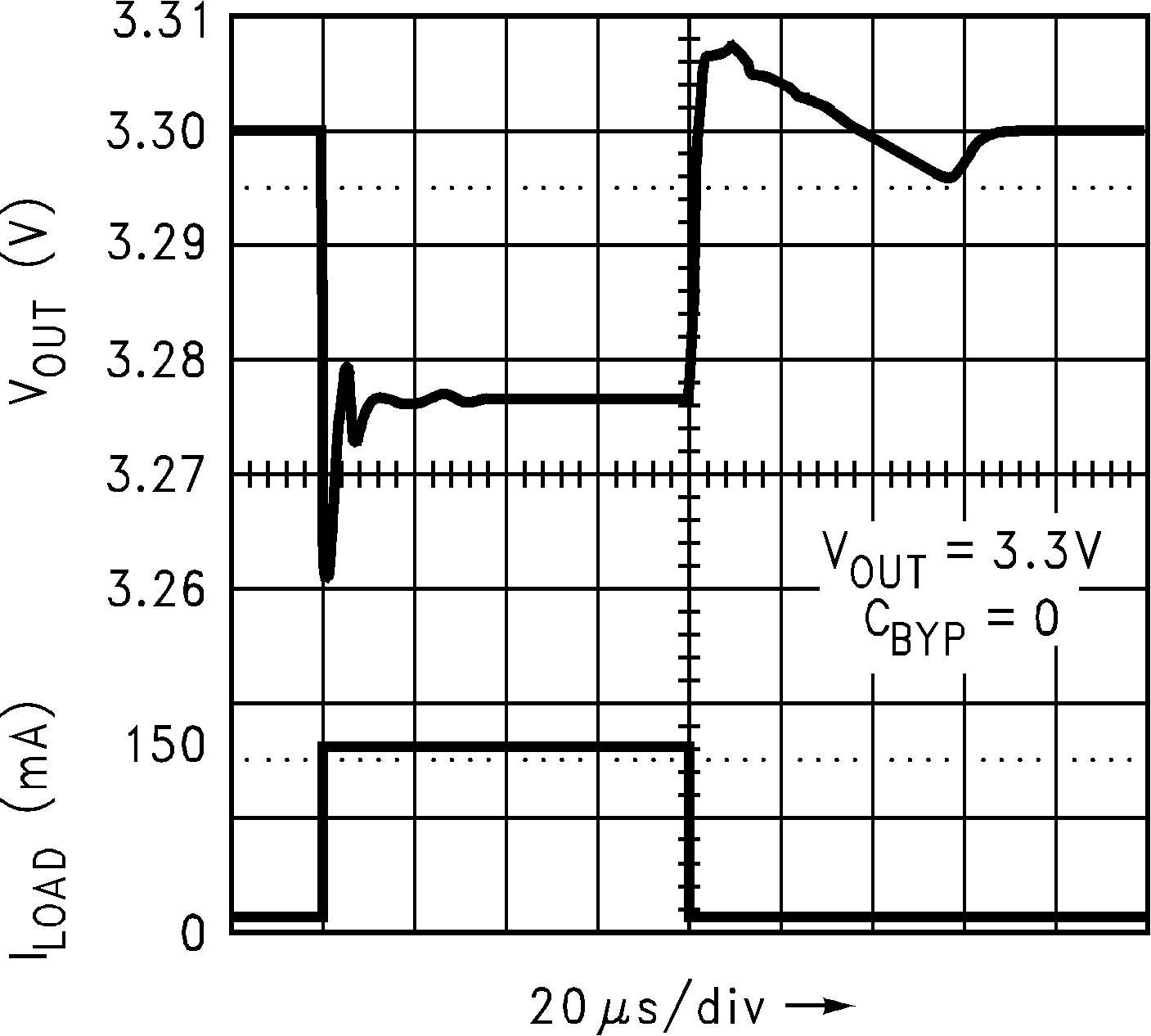

Transient Response for Legacy Chip Figure 8-9 Load

Transient Response for Legacy Chip

Figure 8-9 Load

Transient Response for Legacy Chip Figure 8-11 Load

Transient Response for Legacy Chip

Figure 8-11 Load

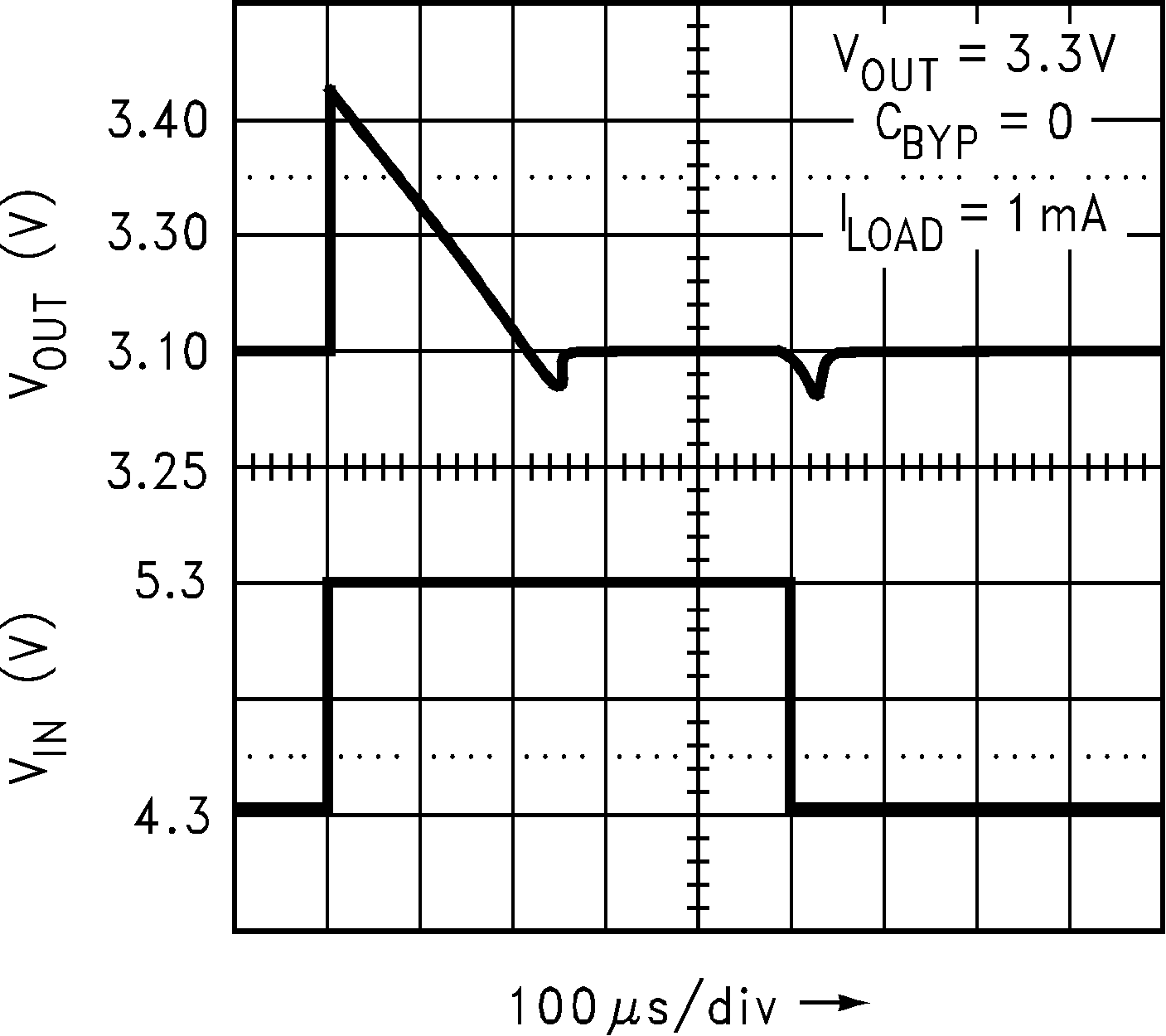

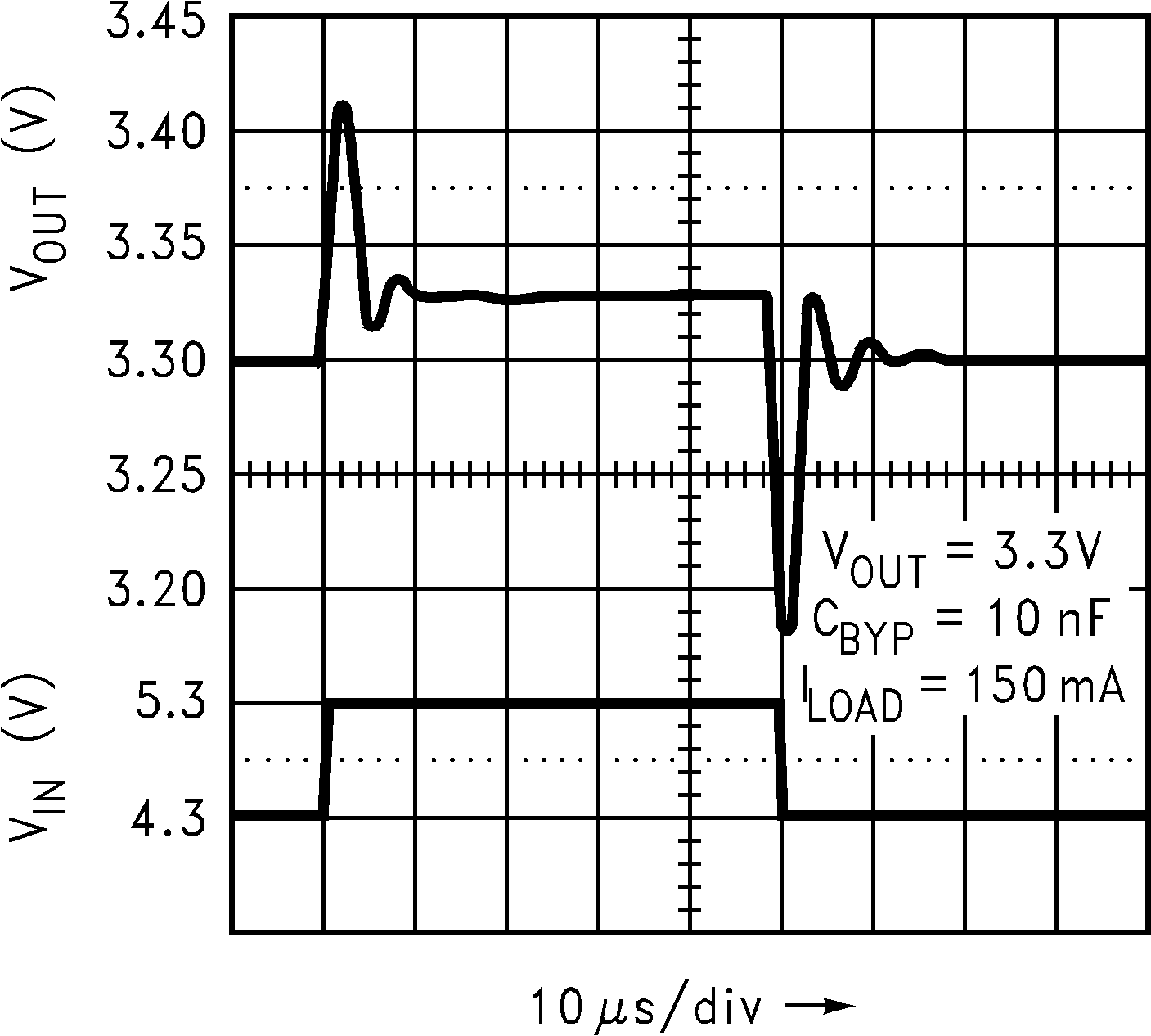

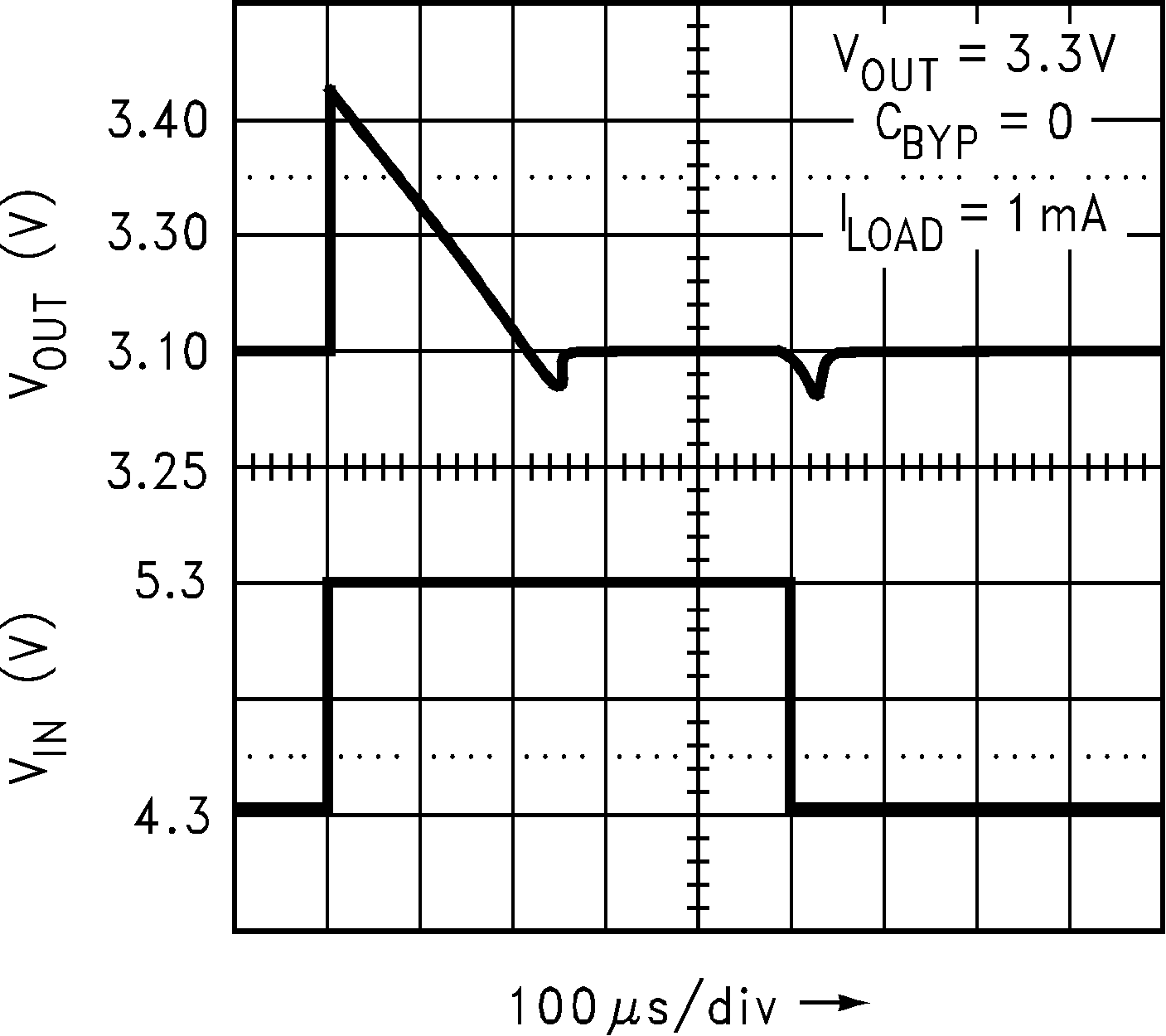

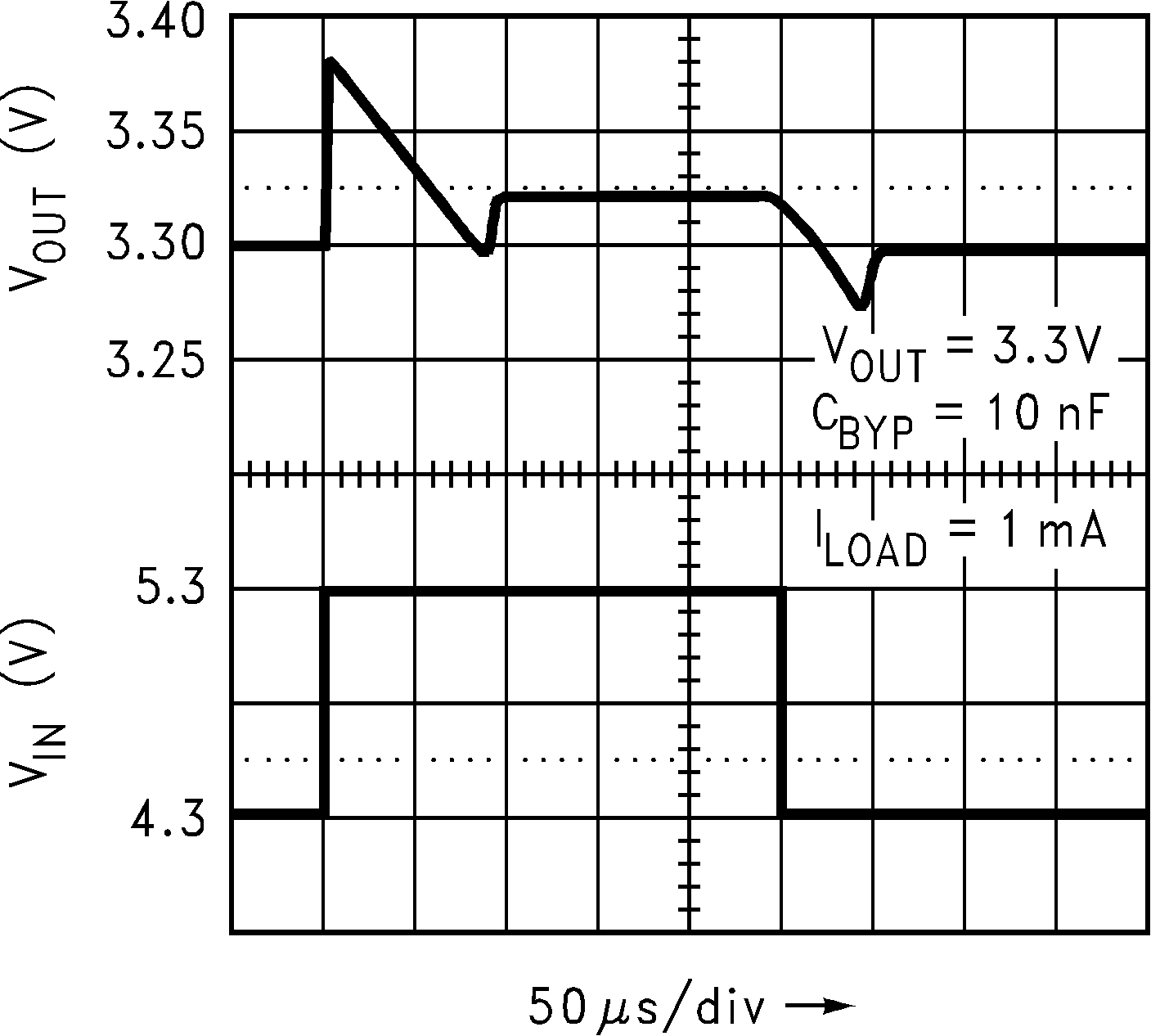

Transient Response for Legacy Chip Figure 8-13 Line

Transient Response for Legacy Chip

Figure 8-13 Line

Transient Response for Legacy Chip Figure 8-15 Line

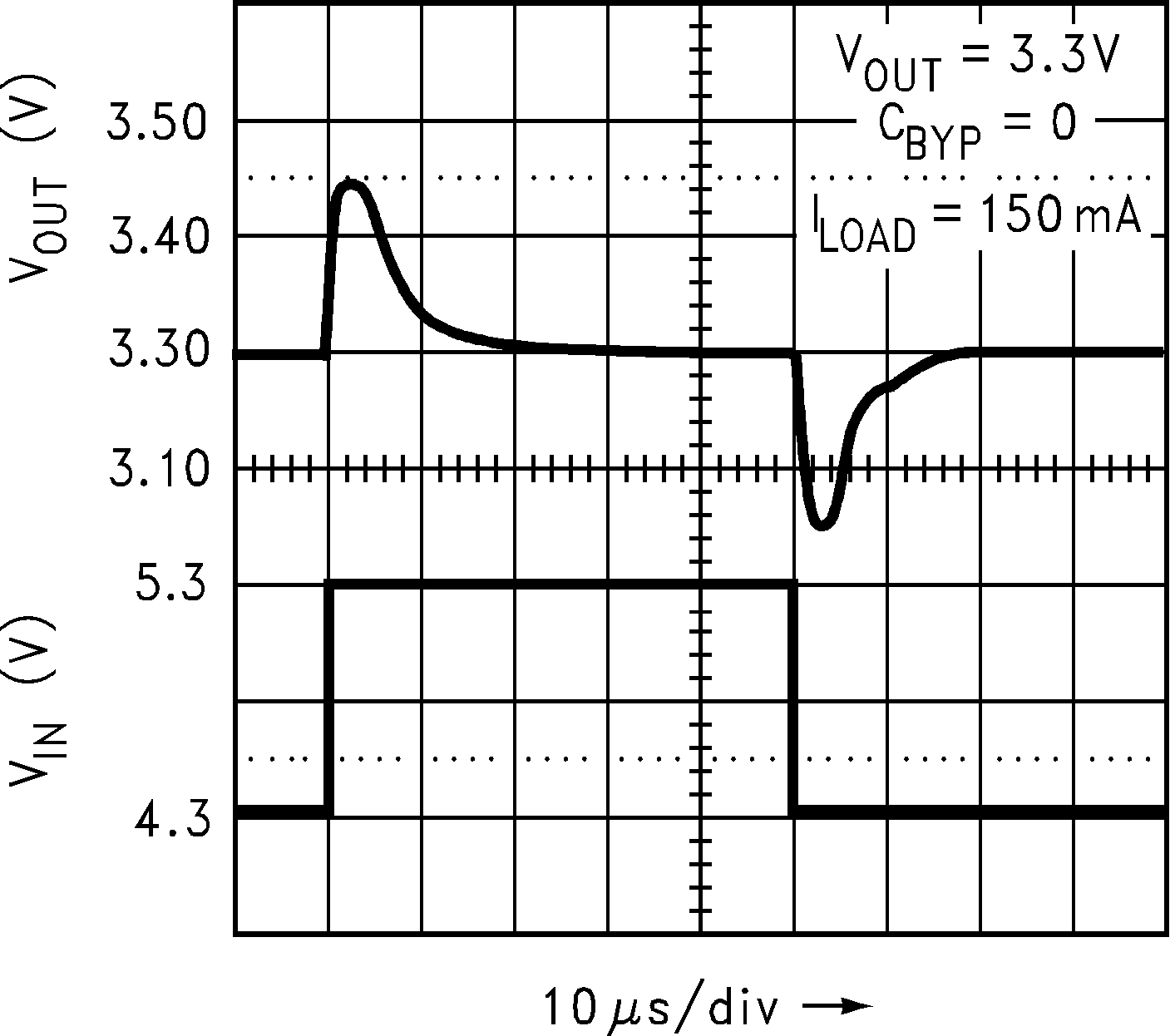

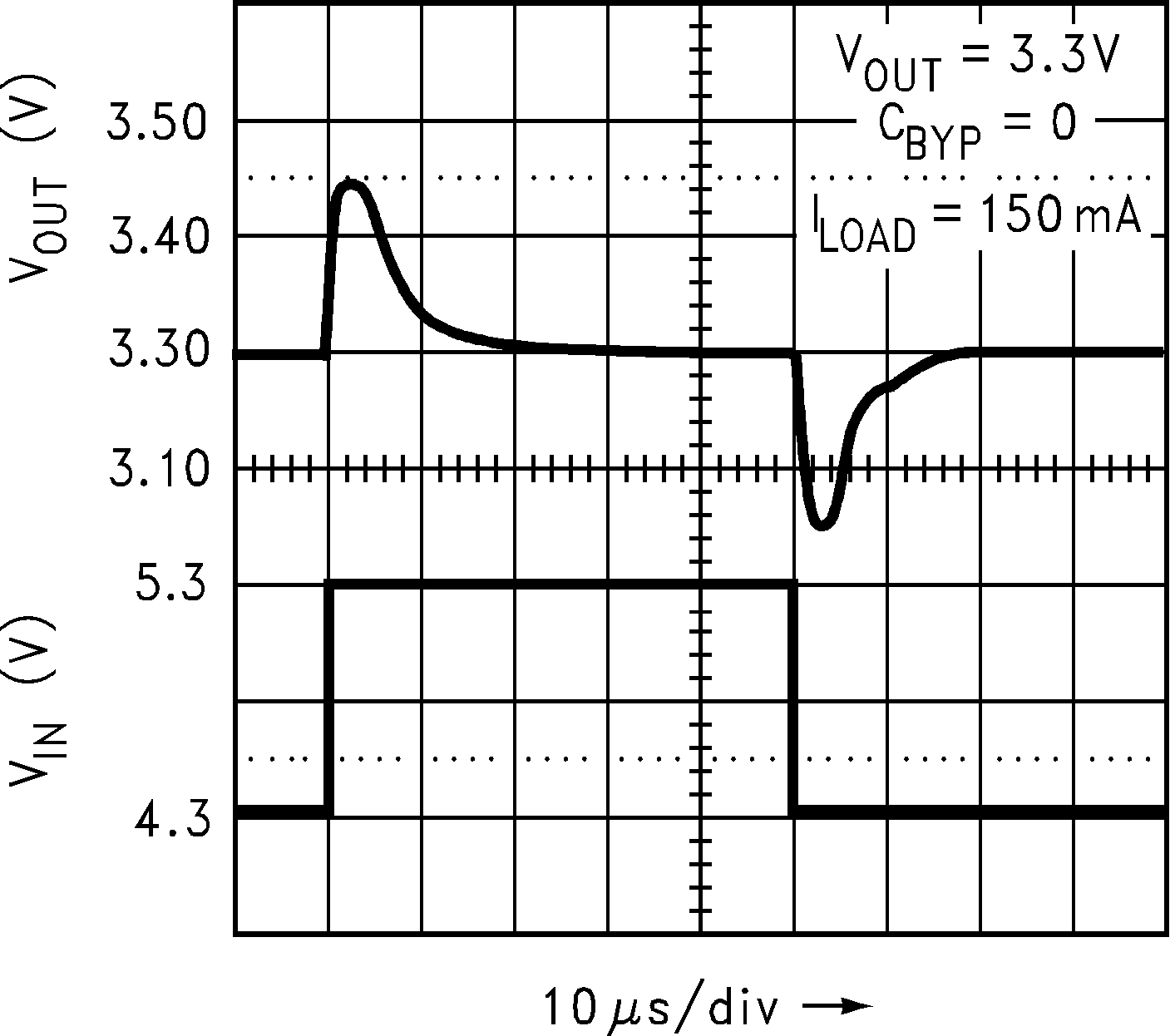

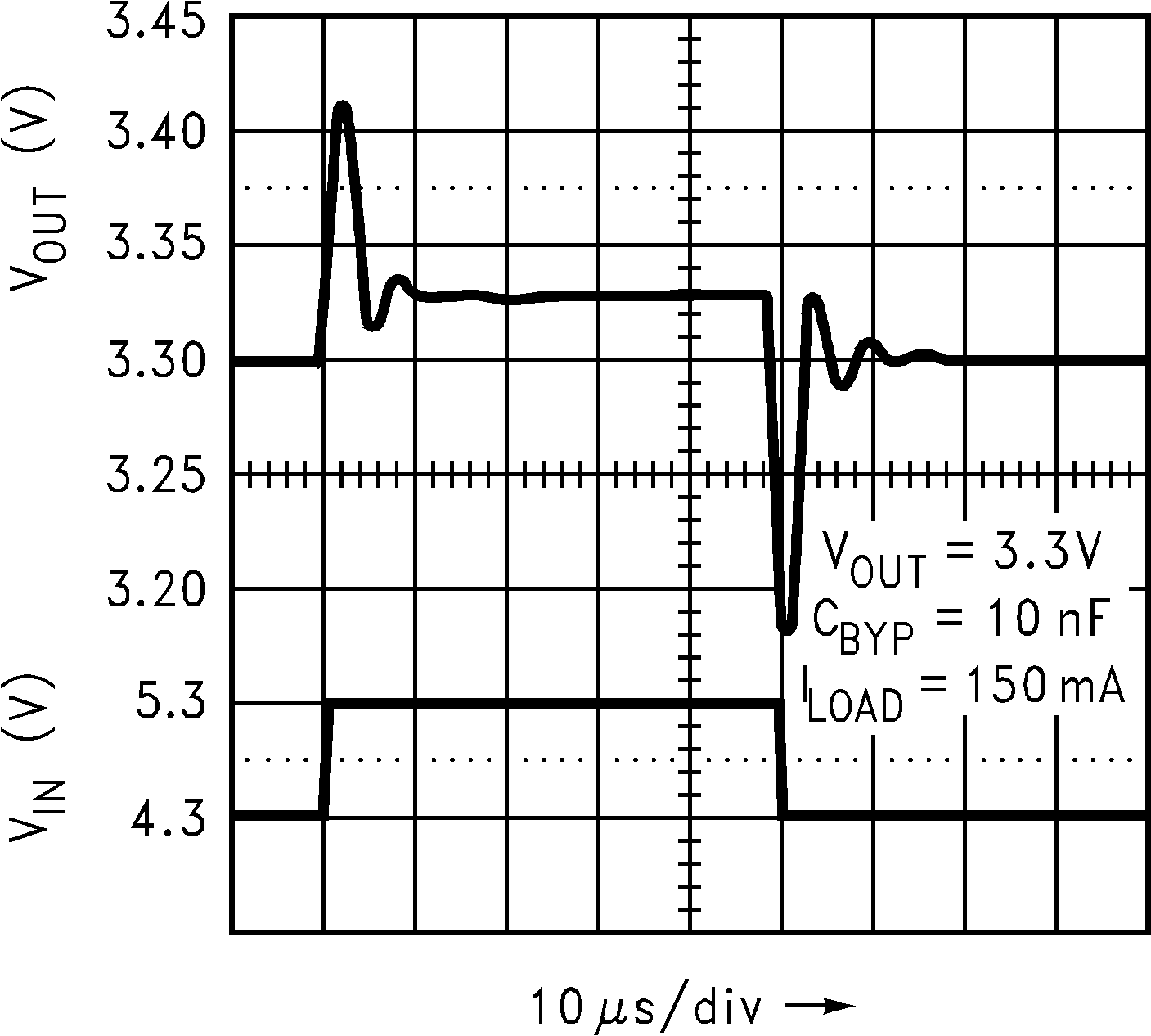

Transient Response for Legacy Chip

Figure 8-15 Line

Transient Response for Legacy Chip Figure 8-17 Line

Transient Response for Legacy Chip

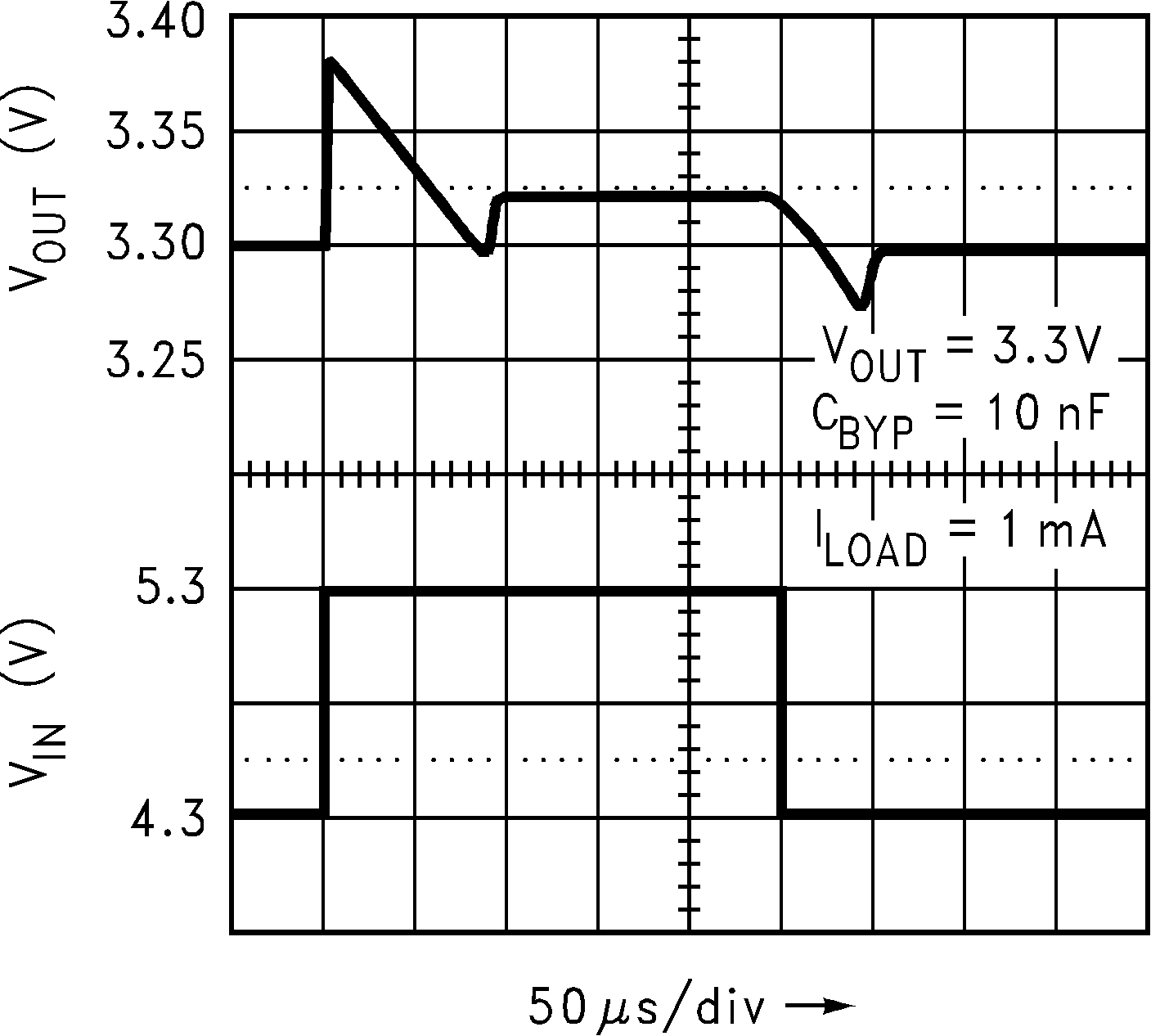

Figure 8-17 Line

Transient Response for Legacy Chip Figure 8-19 Line

Transient Response for Legacy Chip

Figure 8-19 Line

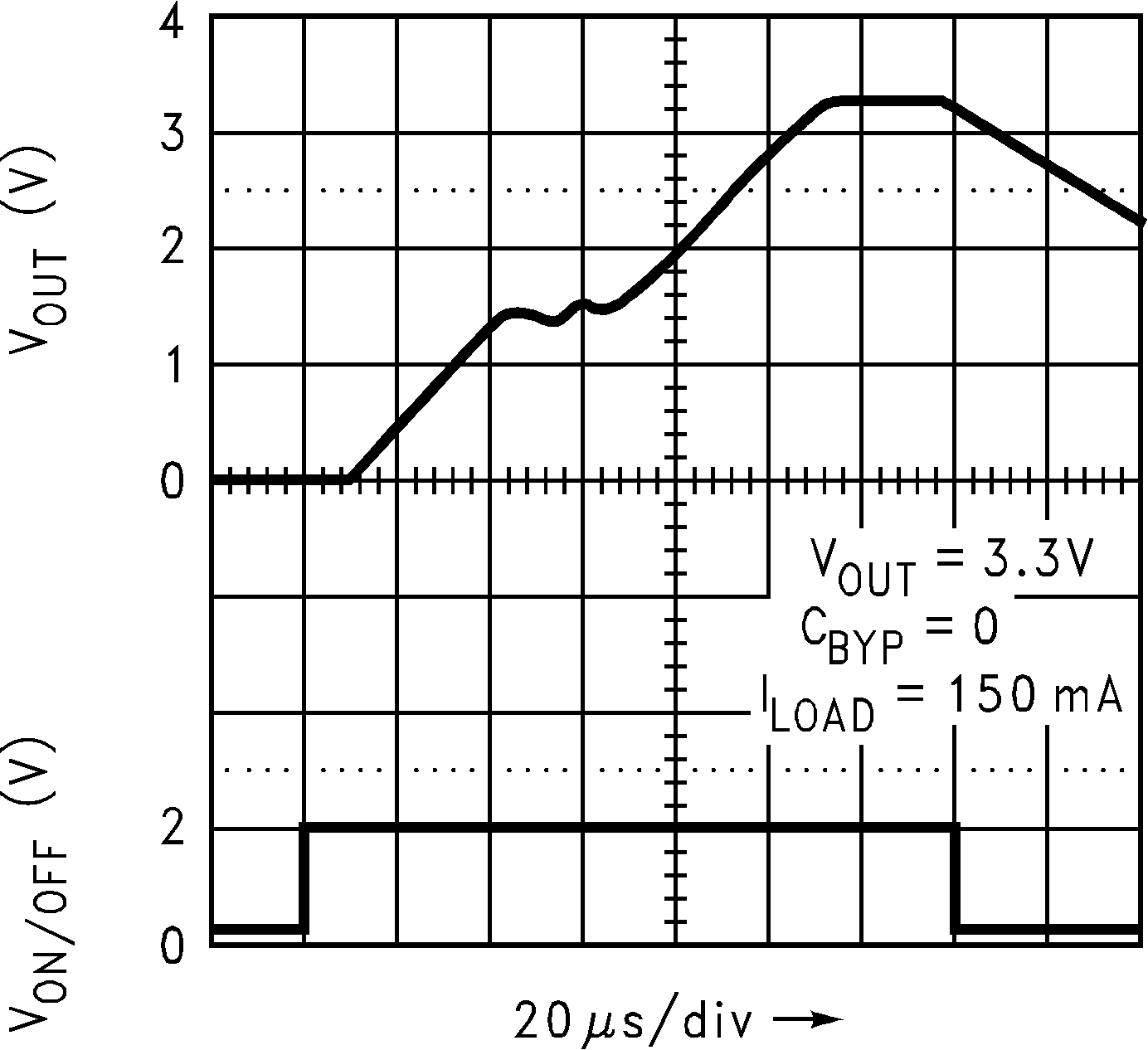

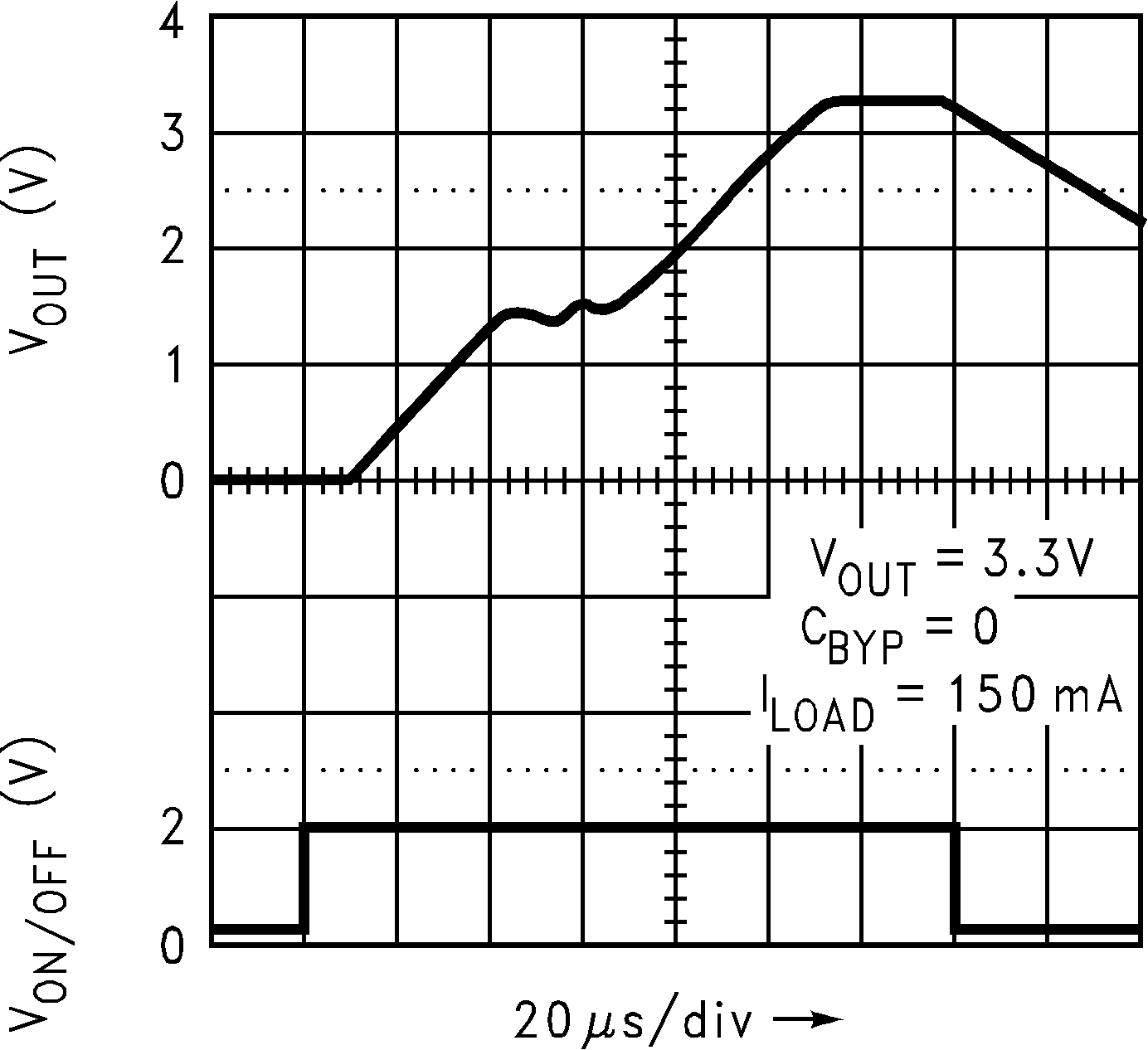

Transient Response for Legacy Chip Figure 8-21 Turn-On Time for Legacy Chip

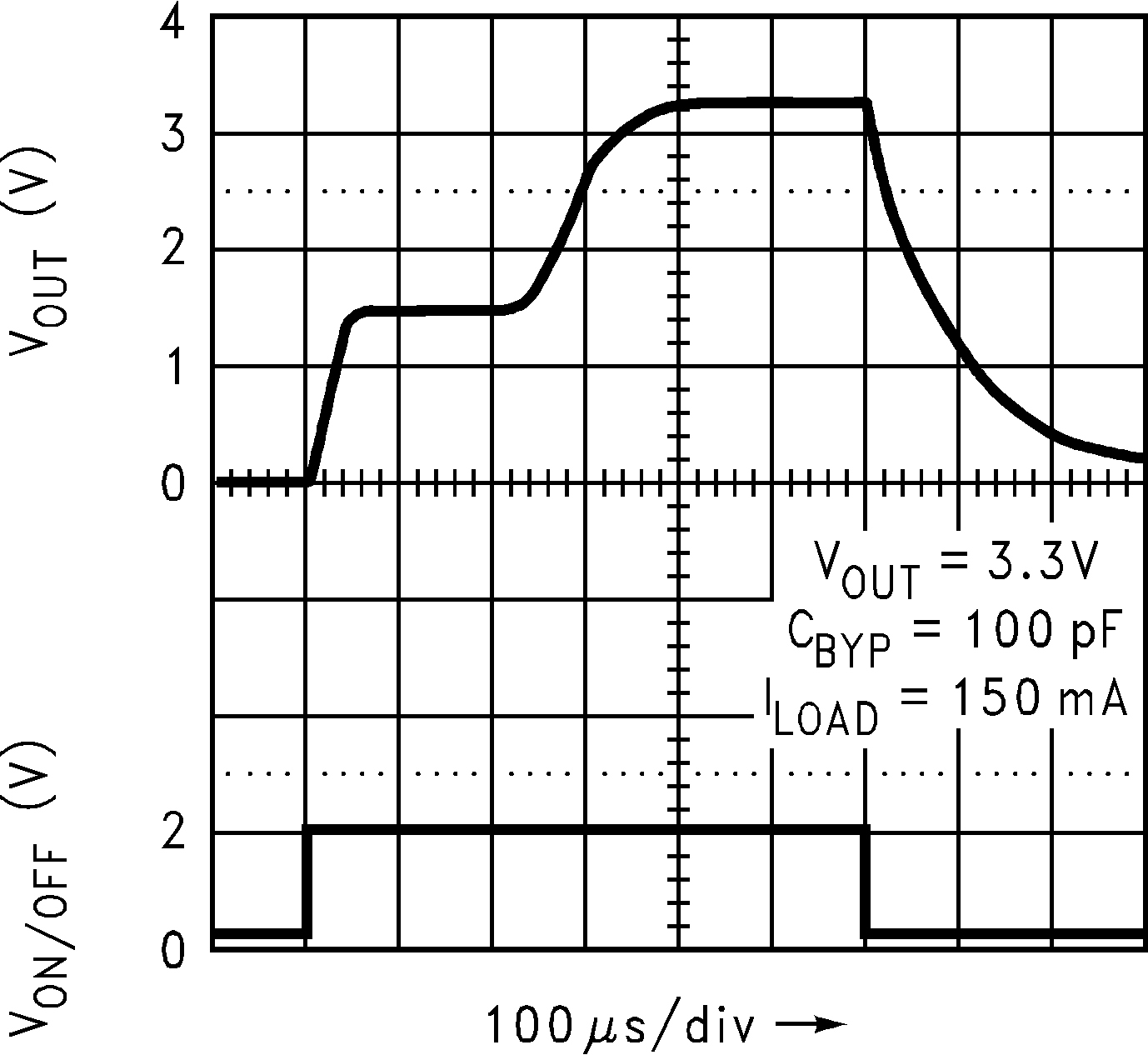

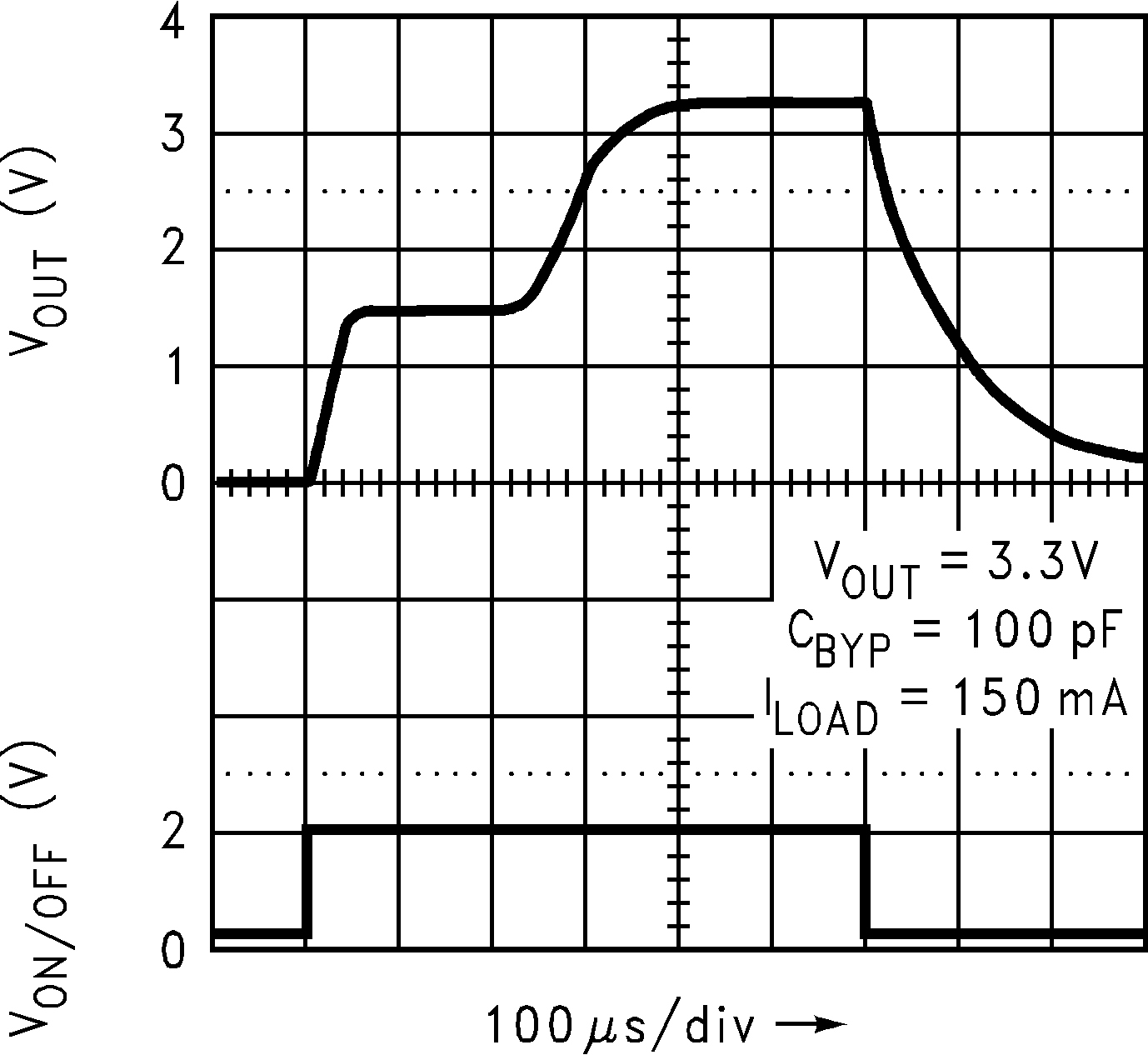

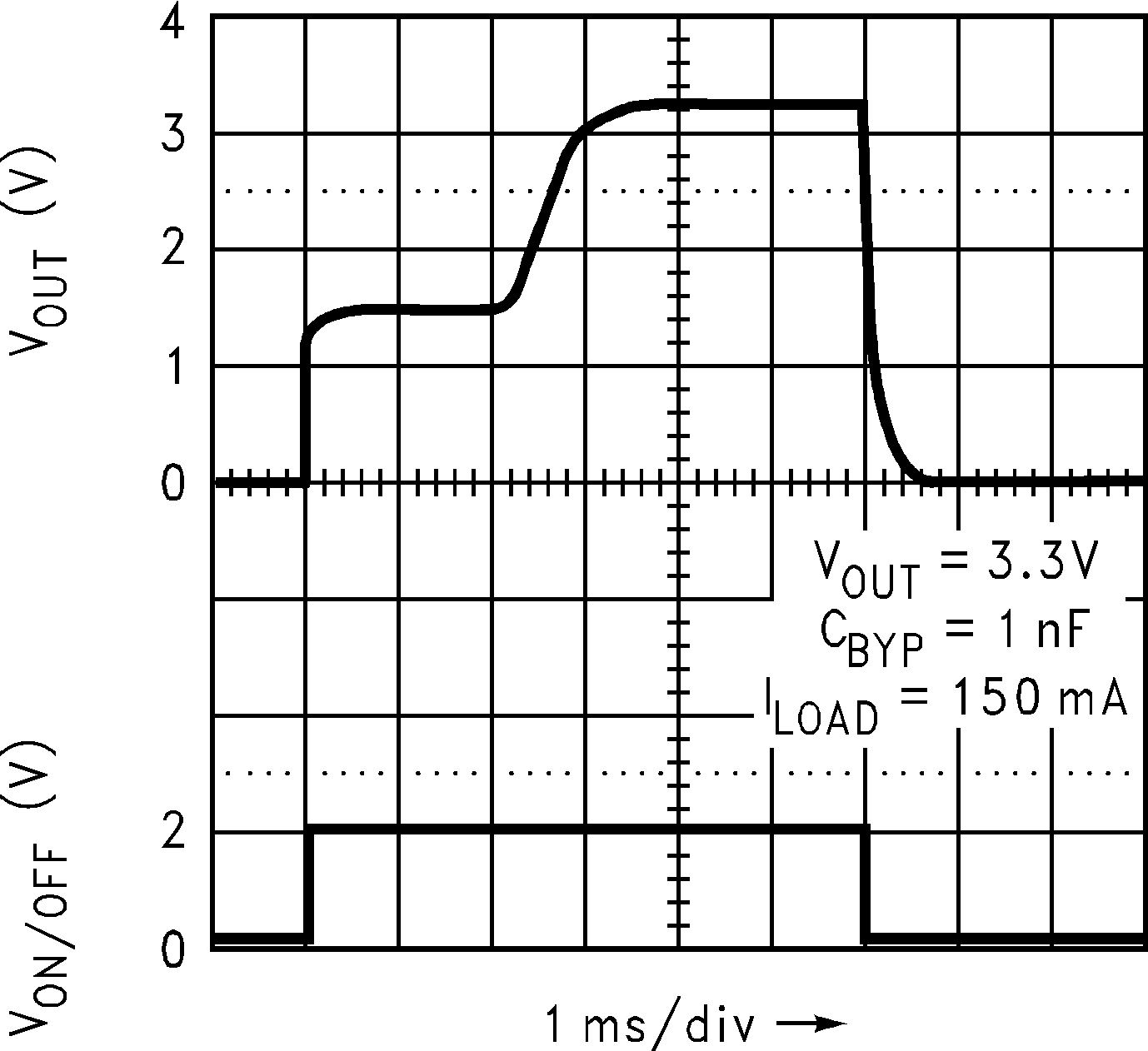

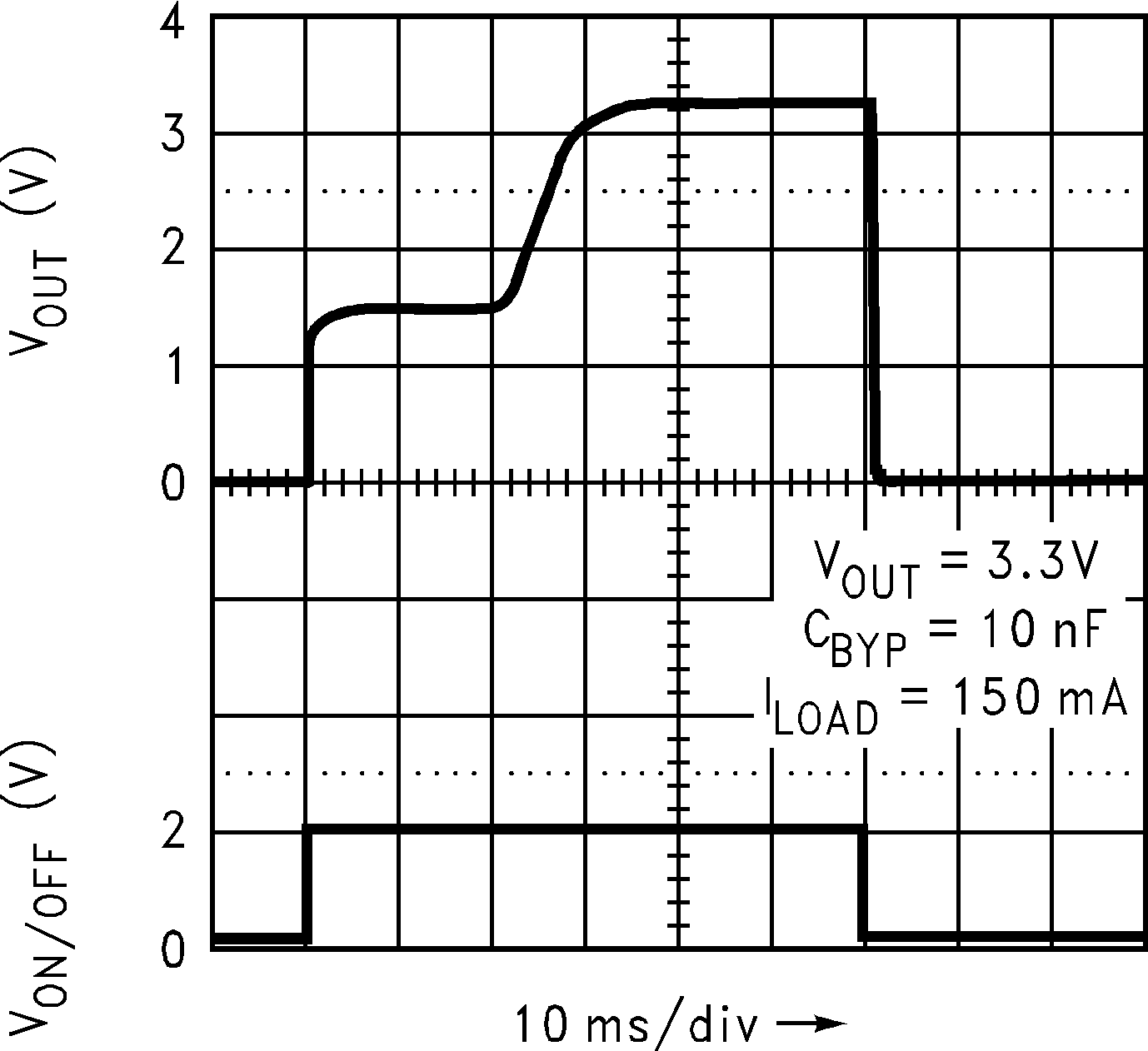

Figure 8-21 Turn-On Time for Legacy Chip Figure 8-23 Turn-On Time for Legacy Chip

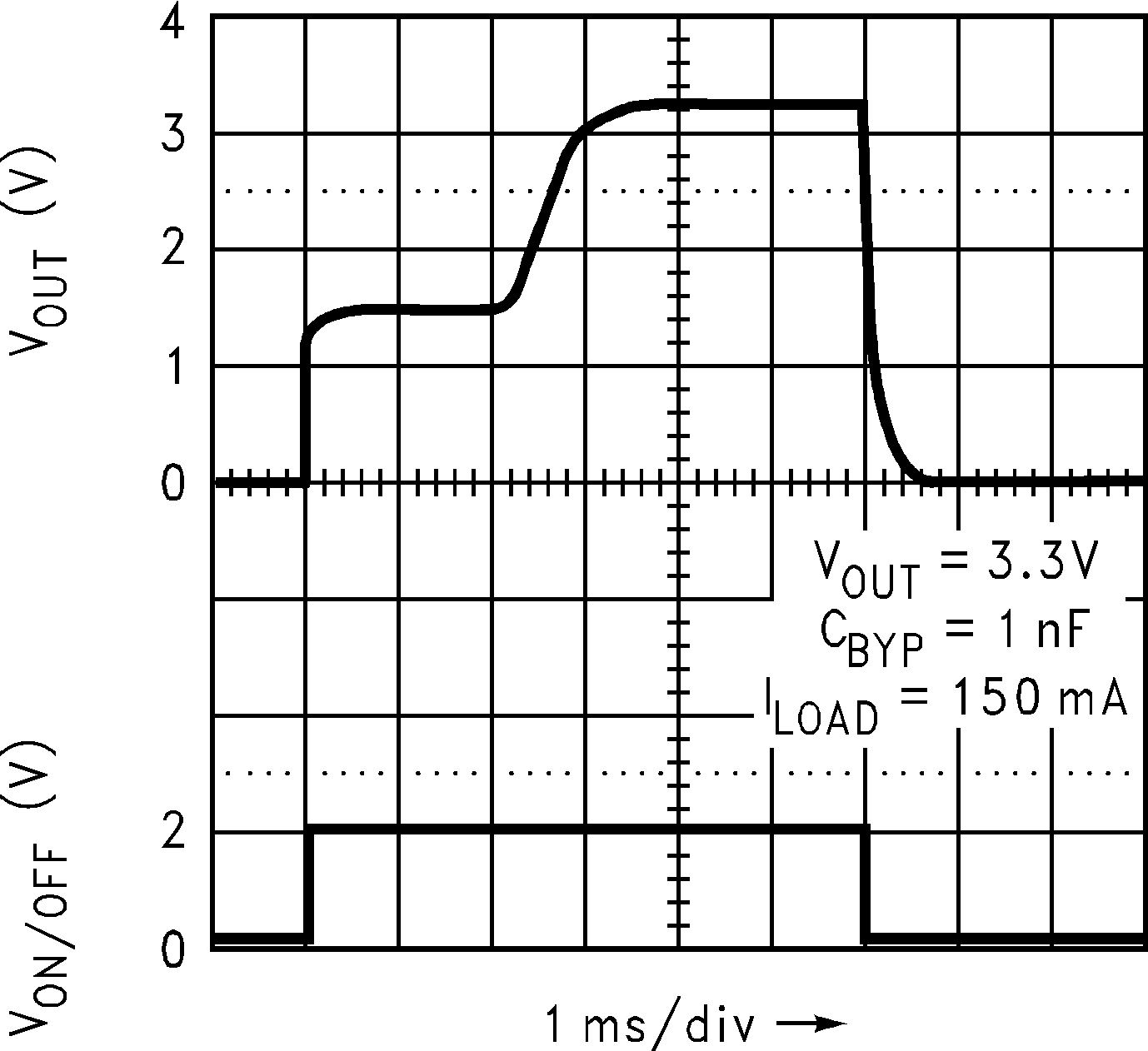

Figure 8-23 Turn-On Time for Legacy Chip Figure 8-25 Turn-On Time for Legacy Chip

Figure 8-25 Turn-On Time for Legacy Chip Figure 8-27 Turn-On Time for Legacy Chip

Figure 8-27 Turn-On Time for Legacy Chip Figure 8-4 Short-Circuit Current for

New Chip at VIN = 6 V

Figure 8-4 Short-Circuit Current for

New Chip at VIN = 6 V Figure 8-6 Short-Circuit Current for

New Chip at VIN = 16 V

Figure 8-6 Short-Circuit Current for

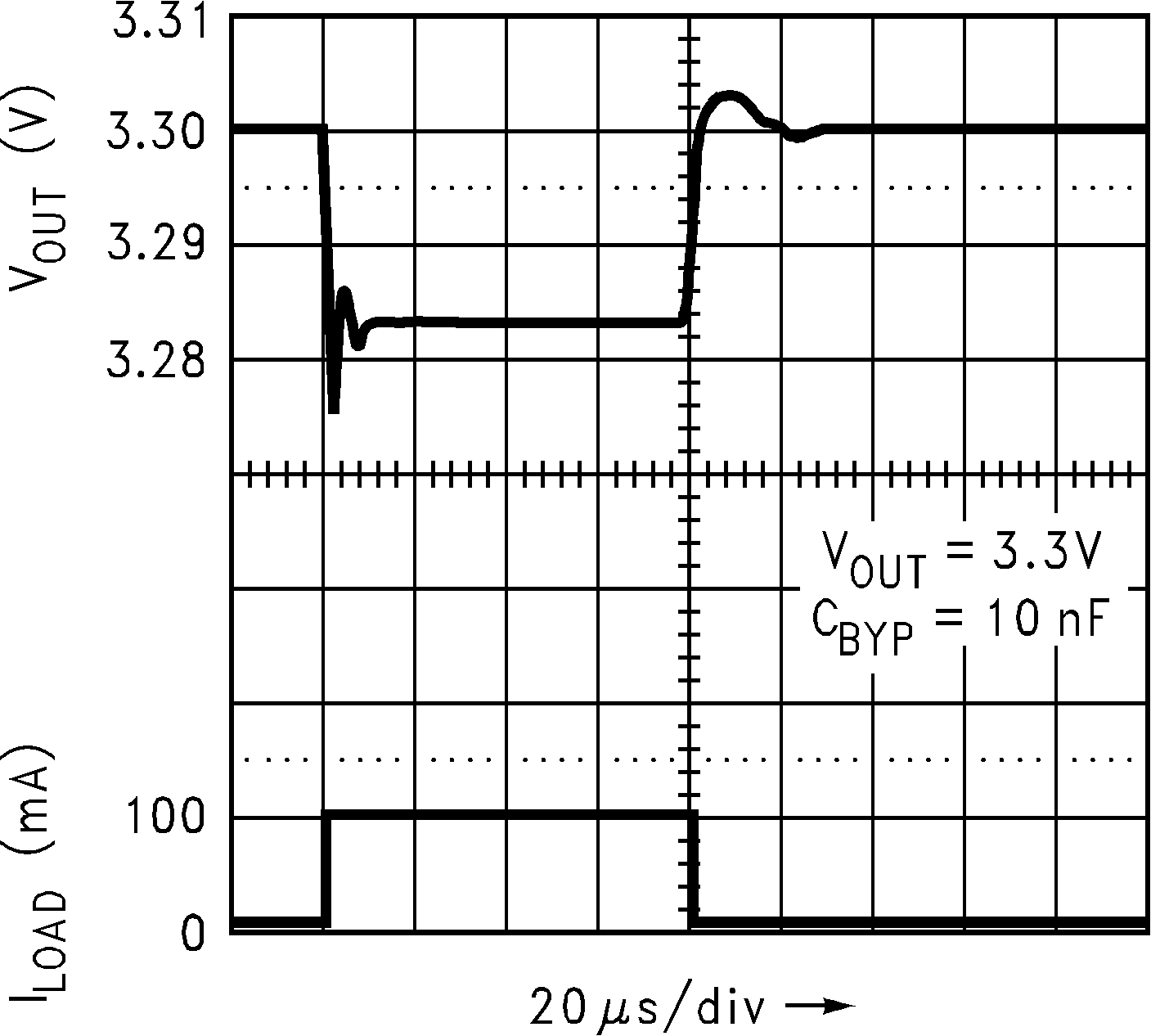

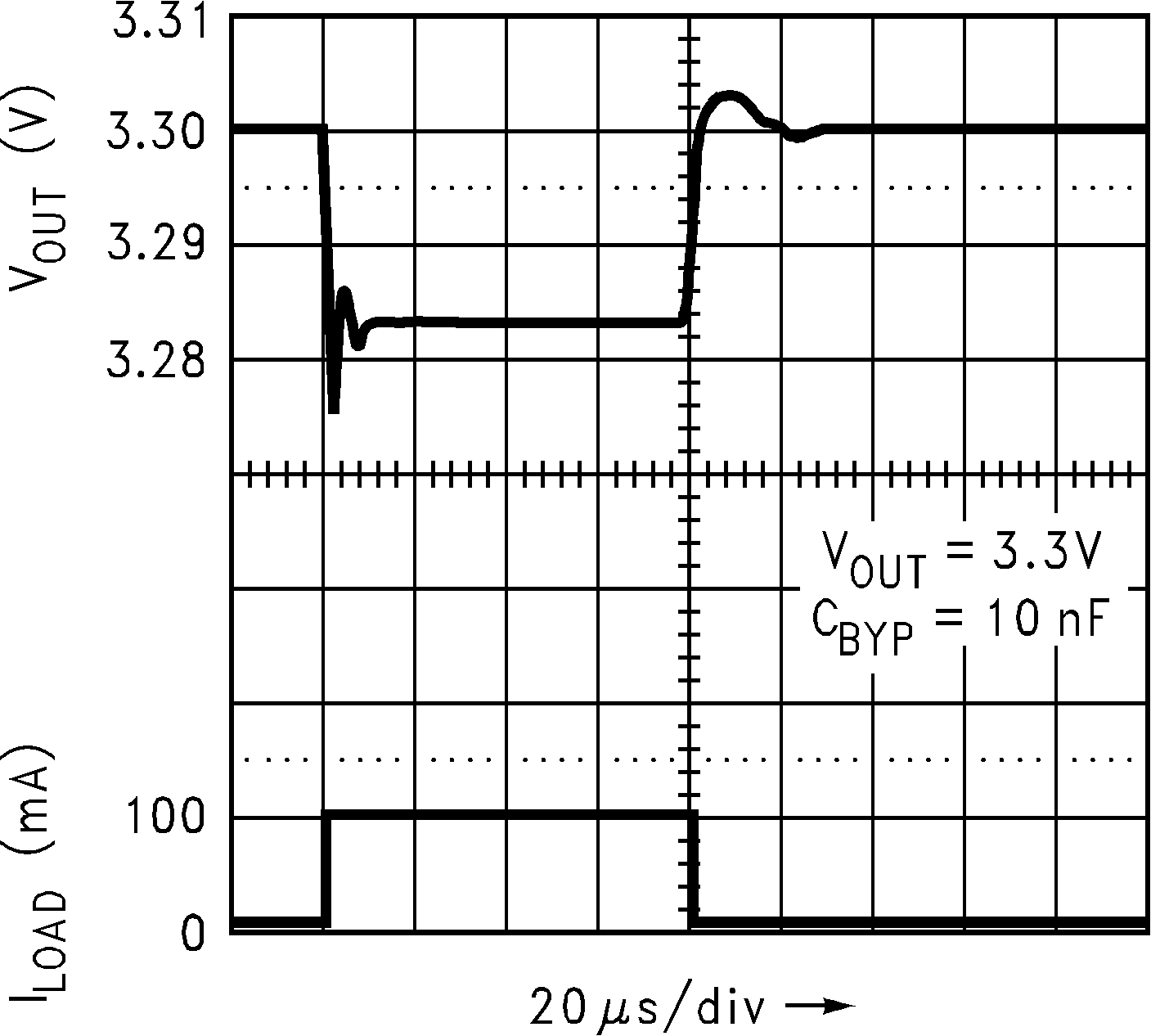

New Chip at VIN = 16 V Figure 8-8 Load Transient Response

for New Chip

Figure 8-8 Load Transient Response

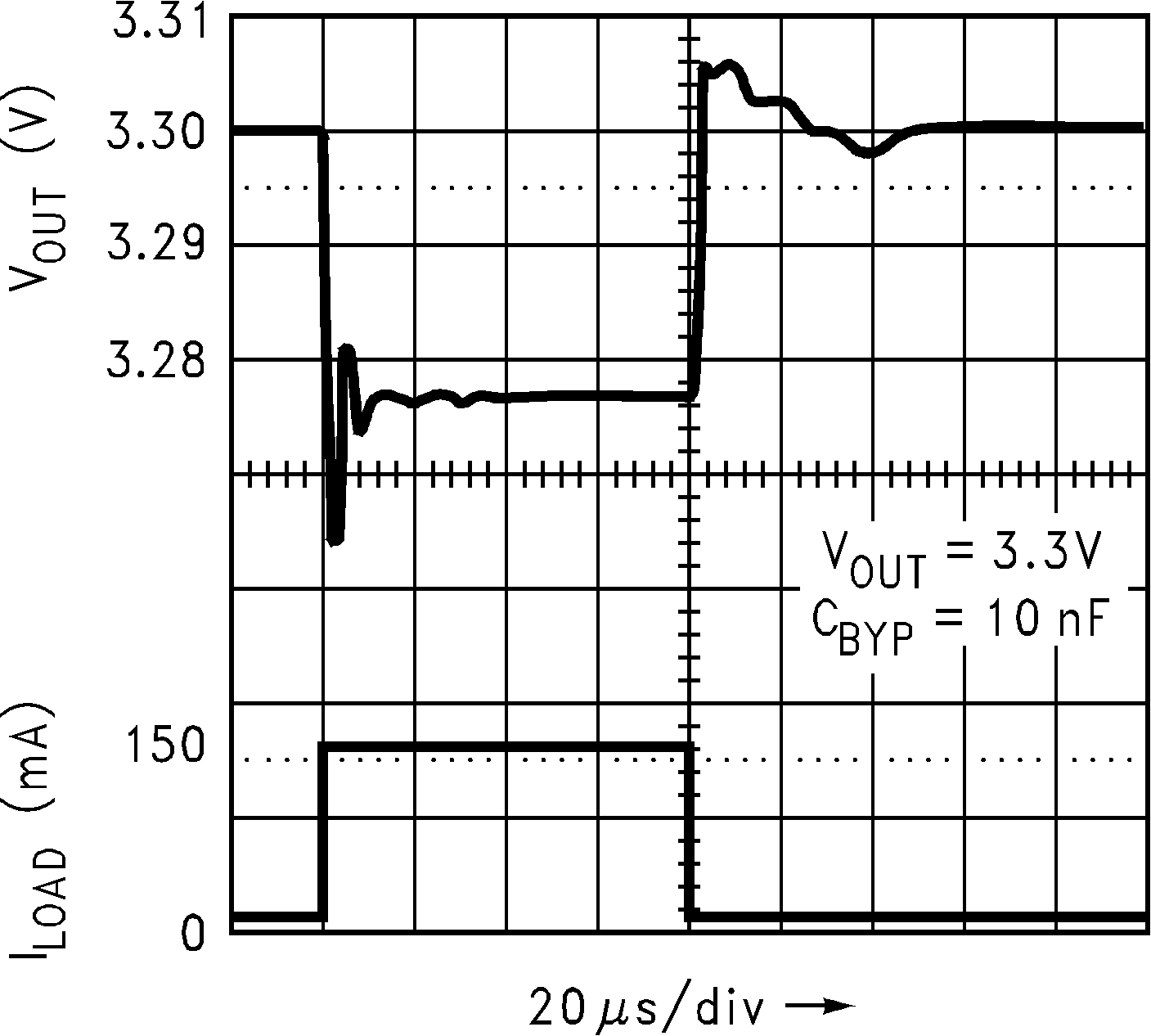

for New Chip Figure 8-10 Load Transient for New

Chip

Figure 8-10 Load Transient for New

Chip Figure 8-12 Load Transient Response

for New Chip

Figure 8-12 Load Transient Response

for New Chip

VOUT = 3.3 V, CBYP = 0 nF,

ΔVIN = 1 V, IOUT = 1 mA,

dV/dt = 1 V/μF |

Figure 8-14 Line Transient Response

for New Chip

VOUT = 3.3 V, CBYP = 0 nF,

ΔVIN = 1 V, IOUT = 150 mA,

dV/dt = 1 V/μF |

Figure 8-16 Line Transient Response

for New Chip

VOUT = 3.3 V, CBYP = 10 nF,

ΔVIN = 1 V, IOUT = 1 mA,

dV/dt = 1 V/μF |

Figure 8-18 Line Transient Response

for New Chip

VOUT = 3.3 V, CBYP = 10 nF,

ΔVIN = 1 V, IOUT = 150 mA,

dV/dt = 1 V/μF |

Figure 8-20 Line Transient Response

for New Chip Figure 8-22 Turn-On Time for New

Chip

Figure 8-22 Turn-On Time for New

Chip Figure 8-24 Turn-On Time for New

Chip

Figure 8-24 Turn-On Time for New

Chip Figure 8-26 Turn-On Time for New

Chip

Figure 8-26 Turn-On Time for New

Chip Figure 8-28 Turn-On Time for New

Chip

Figure 8-28 Turn-On Time for New

Chip