SNVS324K January 2005 – January 2016 LP38691-ADJ , LP38691-ADJ-Q1 , LP38693-ADJ , LP38693-ADJ-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1 Design Requirements

- 8.2.2 Detailed Design Procedure

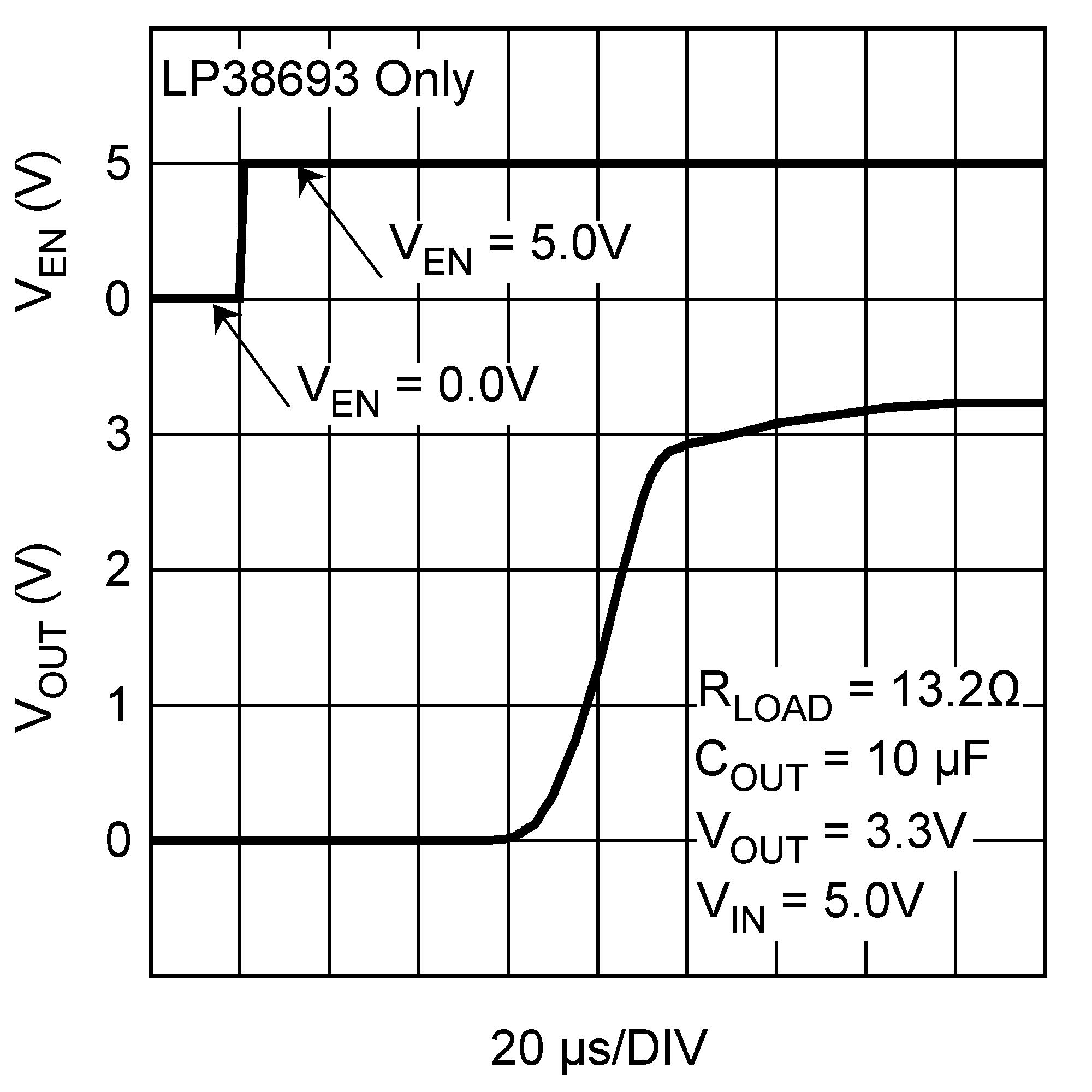

- 8.2.3 Application Curve

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- NGG|6

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| V(MAX) All pins (with respect to GND) | –0.3 | 12 | V | |

| IOUT(4) | Internally limited | V | ||

| Power dissipation(3) | Internally limited | V | ||

| Junction temperature | –40 | 150 | °C | |

| Storage temperature, Tstg | −65 | 150 | ||

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) At elevated temperatures, device power dissipation must be derated based on package thermal resistance and heatsink values (if a heatsink is used). When using the WSON package, refer to Leadless Leadframe Package (LLP) (SNOA401) and the WSON Mounting section in this data sheet. If power dissipation causes the junction temperature to exceed specified limits, the device will go into thermal shutdown.

(4) If used in a dual-supply system where the regulator load is returned to a negative supply, the OUT pin must be diode clamped to ground.

6.2 ESD Ratings: LP38691-ADJ, LP38693-ADJ

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

6.3 ESD Ratings: LP38691-ADJ-Q1, LP38693-ADJ-Q1

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | 2000 | V |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.4 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VIN supply voltage | 2.7 | 10 | V | ||

| Operating junction temperature | −40 | 125 | °C | ||

6.5 Thermal Information

| THERMAL METRIC(1) | LP3869x-ADJ | LP38693-ADJ | UNIT | |

|---|---|---|---|---|

| WSON | SOT-223 | |||

| 6 PINS | 5 PINS | |||

| RθJA(2) | Junction-to-ambient thermal resistance, High-K | 50.6 | 68.5(3) | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 44.4 | 52.2 | |

| RθJB | Junction-to-board thermal resistance | 24.9 | 13.0 | |

| ψJT | Junction-to-top characterization parameter | 0.4 | 5.5 | |

| ψJB | Junction-to-board characterization parameter | 25.1 | 12.8 | |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 5.4 | n/a | |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) Thermal resistance value RθJA is based on the EIA/JEDEC High-K printed circuit board defined by: JESD51-7 - High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages.

(3) The PCB for the WSON (NGN) package RθJA includes thermal vias under the exposed thermal pad per EIA/JEDEC JESD51-5.

6.6 Electrical Characteristics

Unless otherwise specified, limits apply for TJ = 25°C, VIN = VOUT + 1 V, CIN = COUT = 10 µF, ILOAD = 10 mA. Minimum and maximum limits are specified through testing, statistical correlation, or design.| PARAMETER | TEST CONDITIONS | MIN | TYP(1) | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| VADJ | ADJ pin voltage | VIN = 2.7 V | 1.225 | 1.25 | 1.275 | V | |

| 3.2 V ≤ VIN ≤ 10 V, 100 µA < IL < 0.5 A | 1.25 | ||||||

| 3.2 V ≤ VIN ≤ 10 V, 100 µA < IL < 0.5 A Full operating temperature range |

1.2 | 1.3 | |||||

| ΔVOUT/ΔVIN | Output voltage line regulation(2) | VOUT + 0.5 V ≤ VIN ≤ 10 V IL = 25 mA |

0.03 | %/V | |||

| VOUT + 0.5 V ≤ VIN ≤ 10 V IL = 25 mA Full operating temperature range |

0.1 | ||||||

| ΔVOUT/ΔIL | Output voltage load regulation(3) | 1 mA < IL < 0.5 A VIN = VOUT + 1 V |

1.8 | %/A | |||

| 1 mA < IL < 0.5 A VIN = VOUT + 1 V Full operating temperature range |

5 | ||||||

| VDO | Dropout voltage(4) | (VOUT = 2.5 V) | IL = 0.1 A | 80 | mV | ||

| IL = 0.5 A | 430 | ||||||

| (VOUT = 2.5 V) Full operating temperature range |

IL = 0.1 A | 145 | |||||

| IL = 0.5 A | 725 | ||||||

| (VOUT = 3.3 V) | IL = 0.1 A | 65 | |||||

| IL = 0.5 A | 330 | ||||||

| (VOUT = 3.3 V) Full operating temperature range |

IL = 0.1 A | 110 | |||||

| IL = 0.5 A | 550 | ||||||

| (VOUT = 5 V) | IL = 0.1 A | 45 | |||||

| IL = 0.5 A | 250 | ||||||

| (VOUT = 5 V) Full operating temperature range |

IL = 0.1 A | 100 | |||||

| IL = 0.5 A | 450 | ||||||

| IQ | Quiescent current | VIN ≤ 10 V, IL =100 µA – 0.5 A | 55 | µA | |||

| VIN ≤ 10 V, IL =100 µA – 0.5 A Full operating temperature range |

100 | ||||||

| VEN ≤ 0.4 V, (LP38693 Only) | 0.001 | 1 | |||||

| IL(MIN) | Minimum load current | VIN – VOUT ≤ 4 V Full operating temperature range |

100 | ||||

| IFB | Foldback current limit | VIN – VOUT > 5 V | 350 | mA | |||

| VIN – VOUT < 4 V | 850 | ||||||

| PSRR | Ripple rejection | VIN = VOUT + 2 V(DC), with 1 V(p-p) / 120-Hz Ripple | 55 | dB | |||

| TSD | Thermal shutdown activation (junction temp) | 160 | °C | ||||

| TSD (HYST) | Thermal shutdown hysteresis (junction temp) | 10 | |||||

| IADJ | ADJ input leakage current | VADJ = 0 V to 1.5 V, VIN = 10 V | –100 | 0.01 | 100 | nA | |

| en | Output noise | BW = 10 Hz to 10 kHz VOUT = 3.3 V |

0.7 | µV/√Hz | |||

| VOUT (LEAK) | Output leakage current | VOUT = VOUT(NOM) + 1 V at 10 VIN | 0.5 | 2 | µA | ||

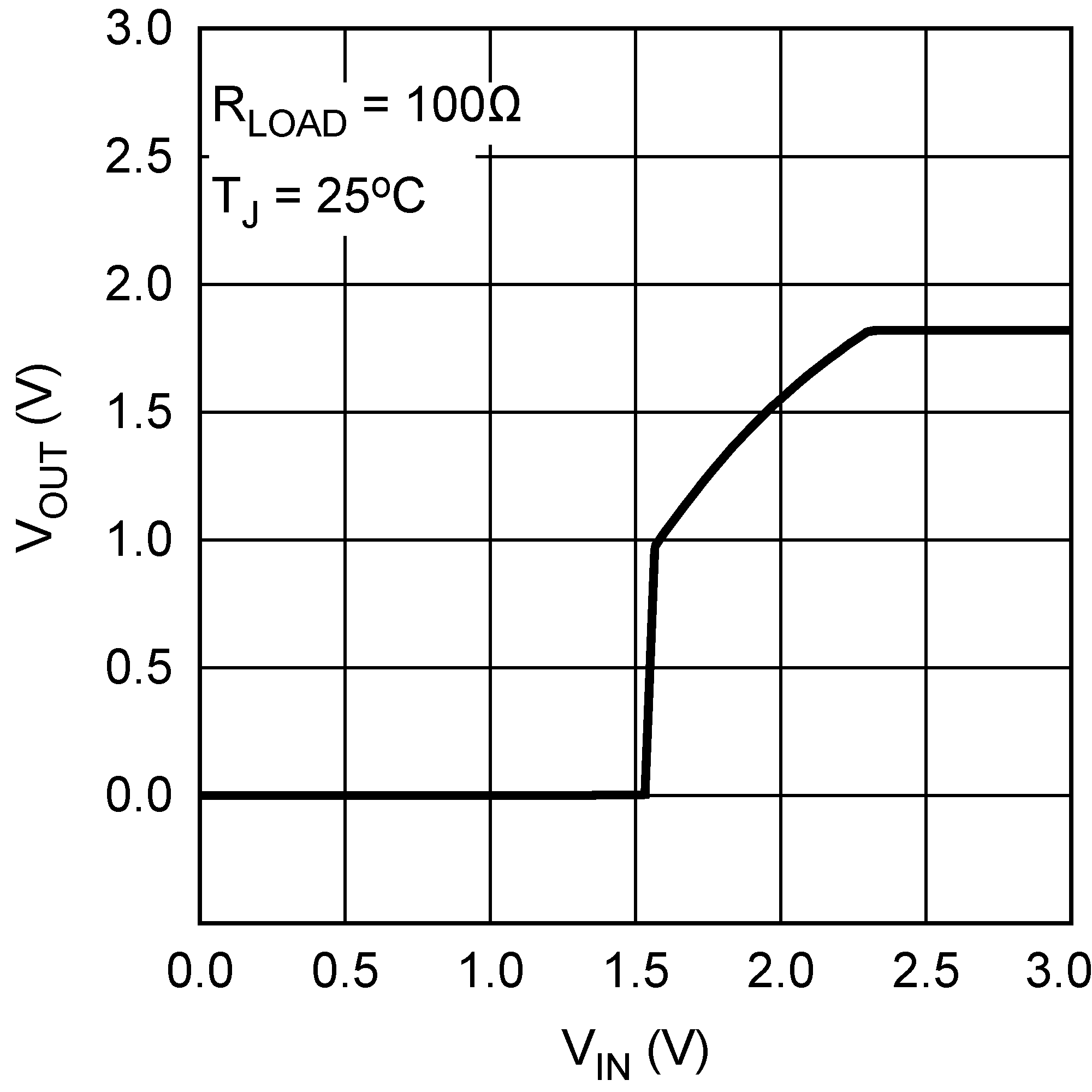

| VEN | Enable voltage (LP38693 Only) | Output = OFF state Full operating temperature range |

0.4 | V | |||

| Output = ON state, VIN = 4 V Full operating temperature range |

1.8 | ||||||

| Output = ON state, VIN = 6 V Full operating temperature range |

3 | ||||||

| Output = ON state, VIN = 10 V Full operating temperature range |

4 | ||||||

| IEN | EN pin leakage (LP38693 only) |

VEN = 0 V or 10 V, VIN = 10 V | –1 | 0.001 | 1 | µA | |

(1) Typical numbers represent the most likely parametric norm for 25°C operation.

(2) Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

(3) Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from 1 mA to full load.

(4) Dropout voltage is defined as the minimum input to output differential required to maintain the output within 100 mV of nominal value.

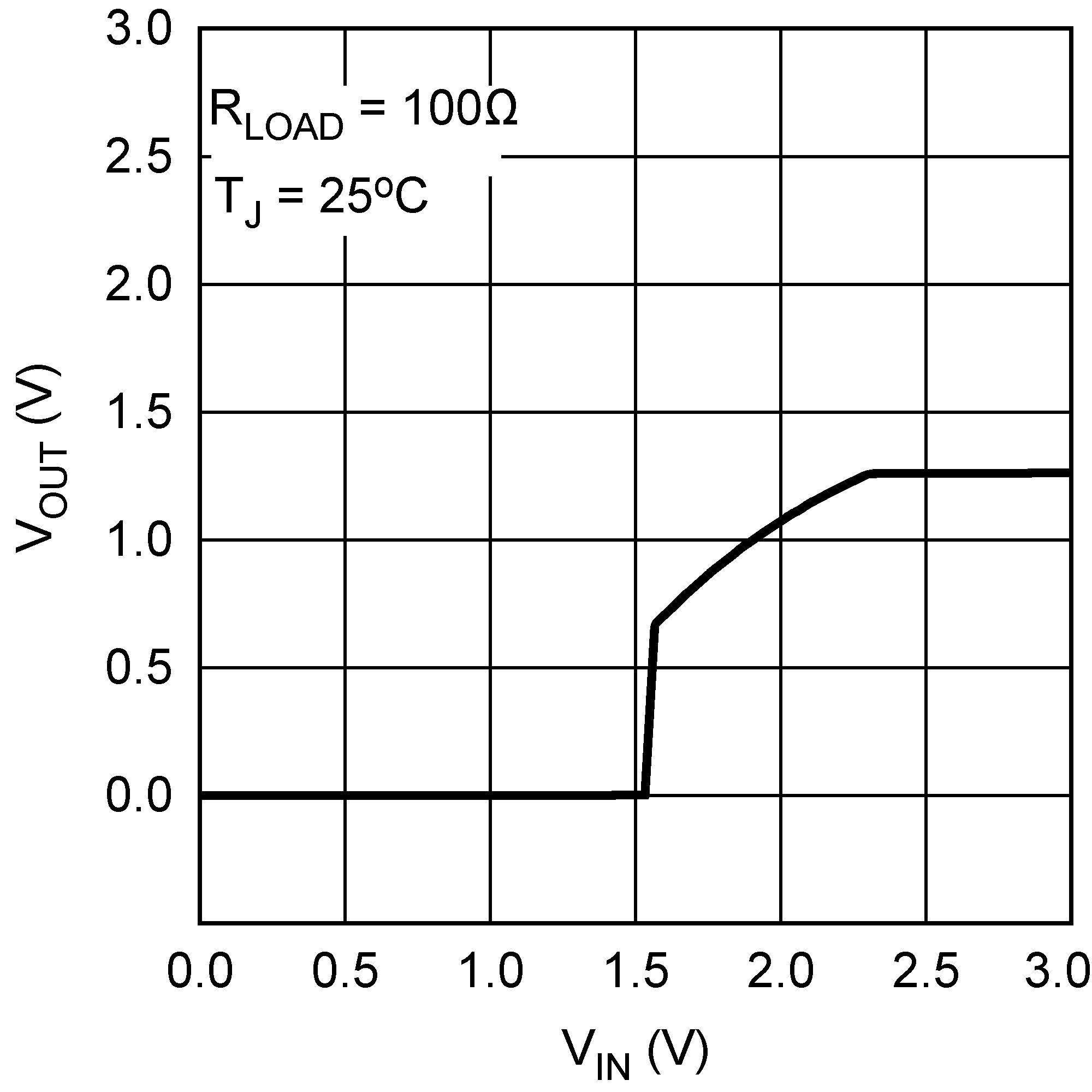

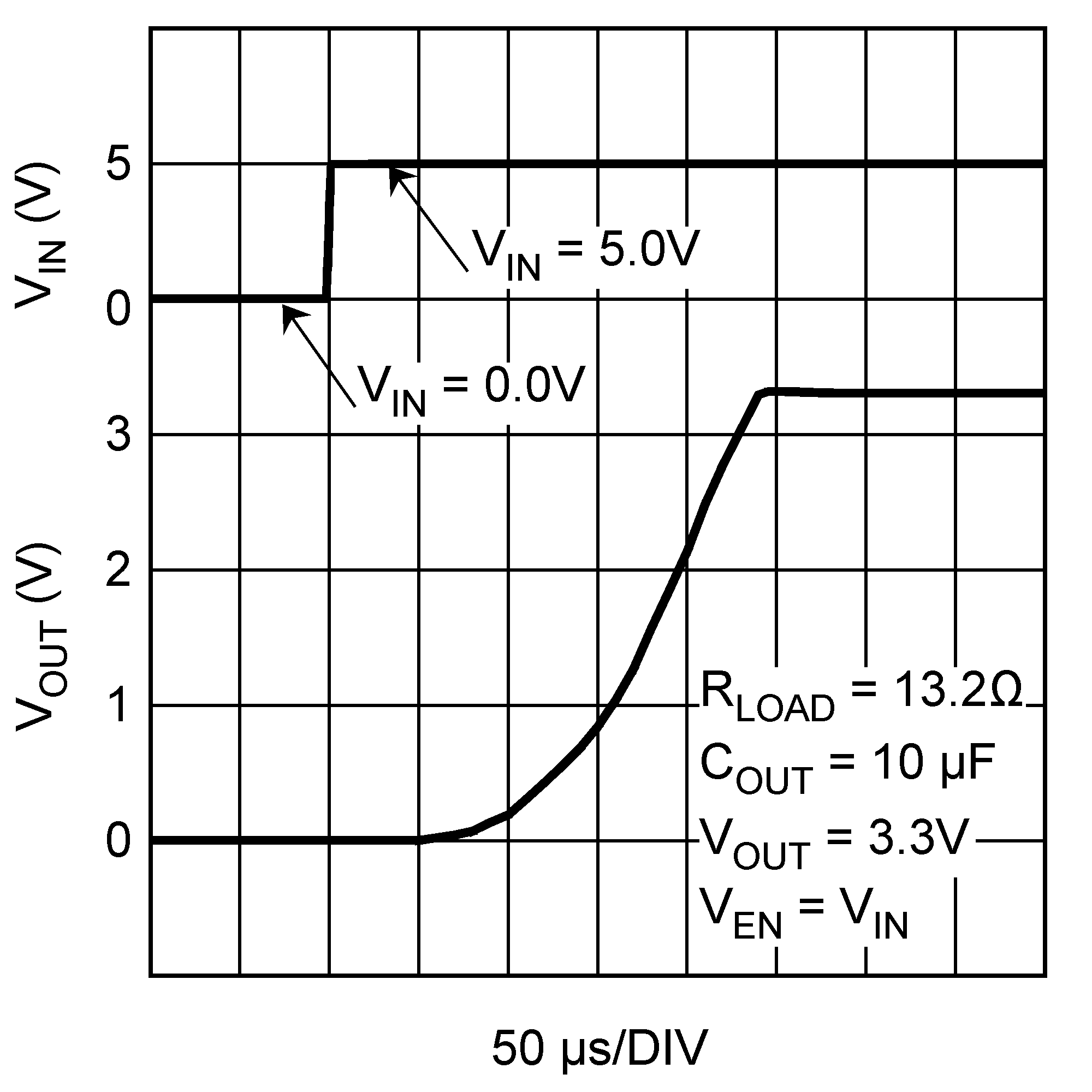

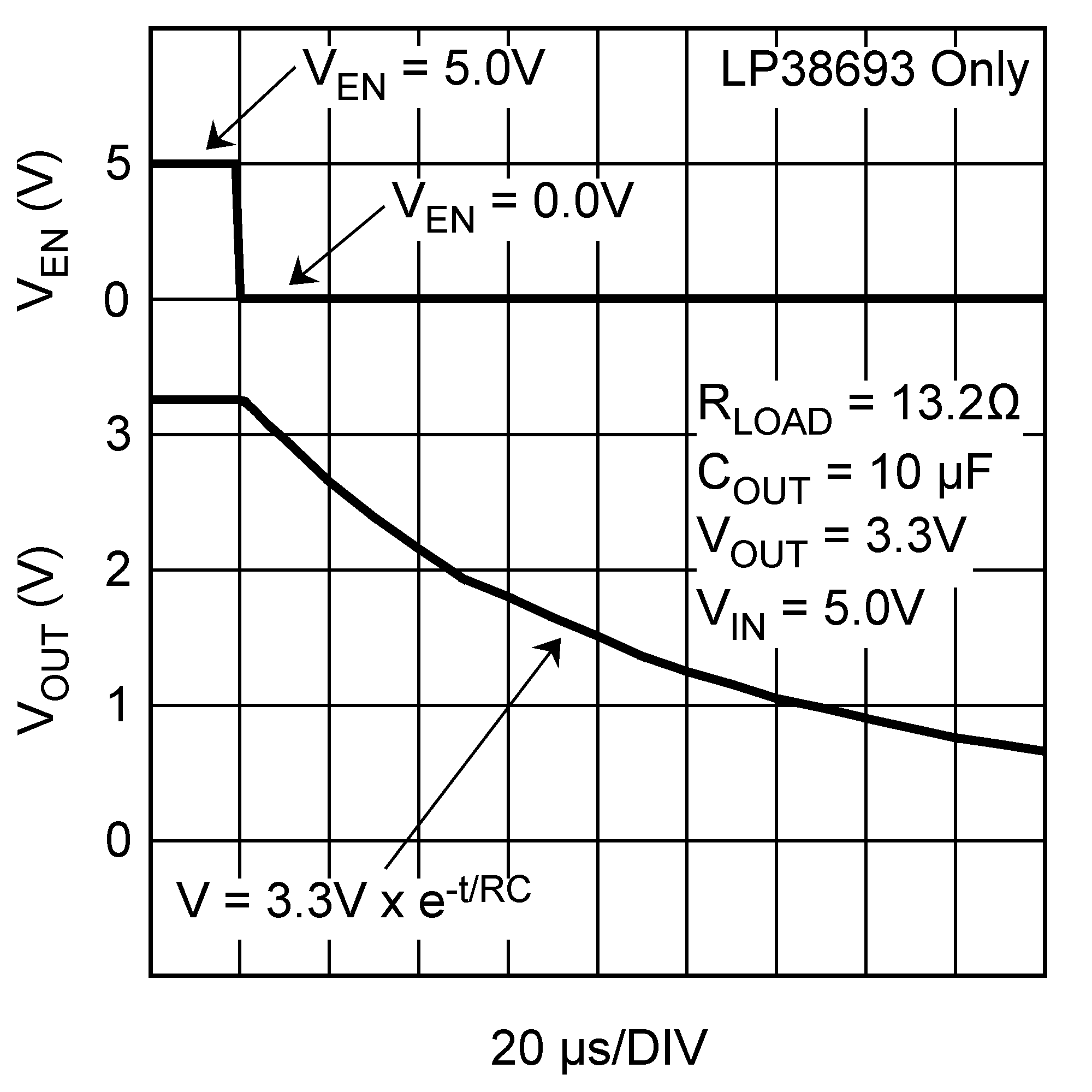

6.7 Typical Characteristics

Unless otherwise specified: TJ = 25°C, CIN = COUT = 10 µF, EN pin is tied to IN (LP38693-ADJ only), VOUT = 1.25 V, VIN = VOUT 1 V, ILOAD = 10 mA.

Figure 3. Noise vs Frequency

Figure 3. Noise vs Frequency

| VOUT = 1.25 V |

| VOUT = 1.8 V |

| VOUT = 1.8 V |