SNVS336F June 2006 – August 2015 LP38856

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- KTT|5

Orderable Information

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The LP38856 can provide 3-A output current with 240-mV dropout voltage (typical). The bias voltage must be in the range of 3 V to 5.5 V to ensure proper operation of the device. The input voltage must be at least VOUT + VDO, and no higher than whatever value is used for VBIAS. Minimal input and output capacitor are 10 µF. The capacitor on the bias pin must be at least 1 μF.

8.2 Typical Application

Figure 23. LP38856 Typical Application

Figure 23. LP38856 Typical Application

8.2.1 Design Requirements

For LP38856 typical applications, use the parameters listed in Table 1 as the input parameters.

Table 1. Design Parameters

| DESIGN PARAMETERS | VALUE |

|---|---|

| Bias voltage | 3 V to 5.5 V |

| Input voltage | VOUT+0.3 V to VBIAS |

| Output voltage | 0.8 V or 1.2 V |

| Output current | 3 A (maximum) |

| Bias capacitor | 1 µF (minimum) |

| Input capacitor | 10 µF (minimum) |

| Output capacitor | 10 uF (minimum) |

8.2.2 Detailed Design Procedure

8.2.2.1 External Capacitors

To assure regulator stability, capacitors are required on the IN, OUT, and BIAS pins as shown in Figure 23.

8.2.2.1.1 Output Capacitor

A minimum output capacitance of 10 µF, ceramic, is required for stability. The amount of output capacitance can be increased without limit. The output capacitor must be located less than 1 cm from the output pin of the device and returned to the device ground pin with a clean analog ground.

Only high quality ceramic types such as X5R or X7R should be used, as the Z5U and Y5F types do not provide sufficient capacitance over temperature.

Tantalum capacitors will also provide stable operation across the entire operating temperature range. However, the effects of ESR may provide variations in the output voltage during fast load transients. Using the minimum recommended 10 µF ceramic capacitor at the output will allow unlimited capacitance, tantalum and/or aluminum, to be added in parallel.

8.2.2.1.2 Input Capacitor

The input capacitor must be at least 10 µF, but can be increased without limit. Its purpose is to provide a low source impedance for the regulator input. A ceramic capacitor, X5R or X7R, is recommended.

Tantalum capacitors may also be used at the input pin. There is no specific ESR limitation on the input capacitor (the lower, the better).

Aluminum electrolytic capacitors can be used, but are not recommended as their ESR increases very quickly at cold temperatures. They are not recommended for any application where the ambient temperature falls below 0°C.

8.2.2.1.3 Bias Capacitor

The capacitor on the bias pin must be at least 1 µF. It can be any good quality capacitor (ceramic is recommended).

8.2.2.2 Power Dissipation and Heatsinking

A heat-sink may be required depending on the maximum power dissipation and maximum ambient temperature of the application. Under all possible conditions, the junction temperature must be within the range specified under operating conditions.

The total power dissipation of the device is the sum of three different points of dissipation in the device.

The first part is the power that is dissipated in the NMOS pass element, and can be determined with the formula:

The second part is the power that is dissipated in the bias and control circuitry, and can be determined with the formula:

where

- IGND(BIAS) is the portion of the operating ground current of the device that is related to VBIAS.

The third part is the power that is dissipated in portions of the output stage circuitry, and can be determined with the formula:

where

- IGND(IN) is the portion of the operating ground current of the device that is related to VIN.

The total power dissipation is then:

The maximum allowable junction temperature rise (ΔTJ) depends on the maximum anticipated ambient temperature (TA(MAX)) for the application, and the maximum allowable operating junction temperature (TJ(MAX)):

The maximum allowable value for junction to ambient thermal resistance, RθJA, can be calculated using the formula:

The LP38856 is available in TO-220 and DDPAK/TO-263 packages. The thermal resistance in the application depends on amount of copper area or heat-sink, and on air flow. If the maximum allowable value of R θJA calculated above is ≥ 32°C/W for TO-220 package and ≥ 41°C/W for DDPAK/TO-263 package no heat-sink is needed because the package alone can dissipate enough heat to satisfy these requirements. If the value needed for allowable RθJA falls below these limits, a heat-sink is required.

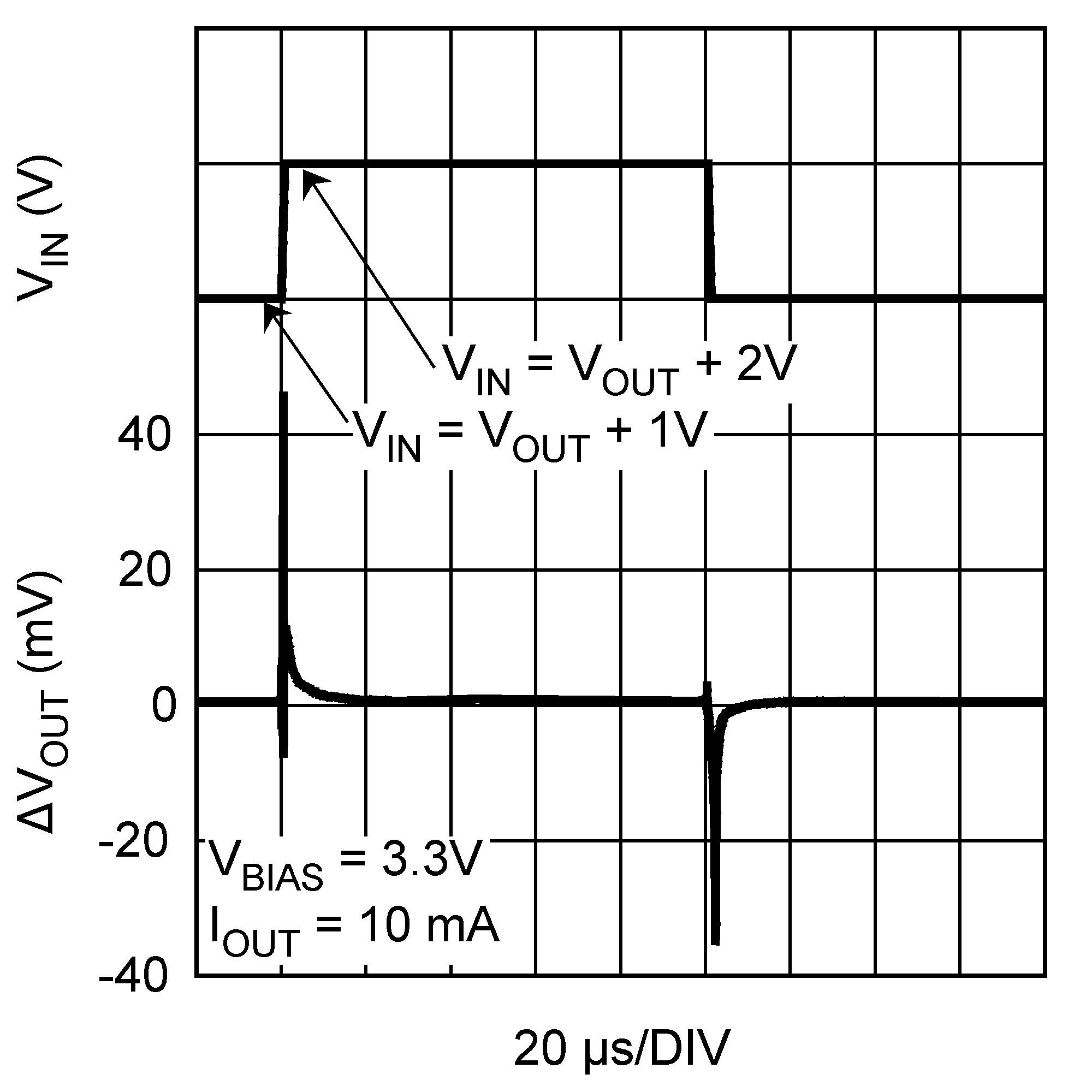

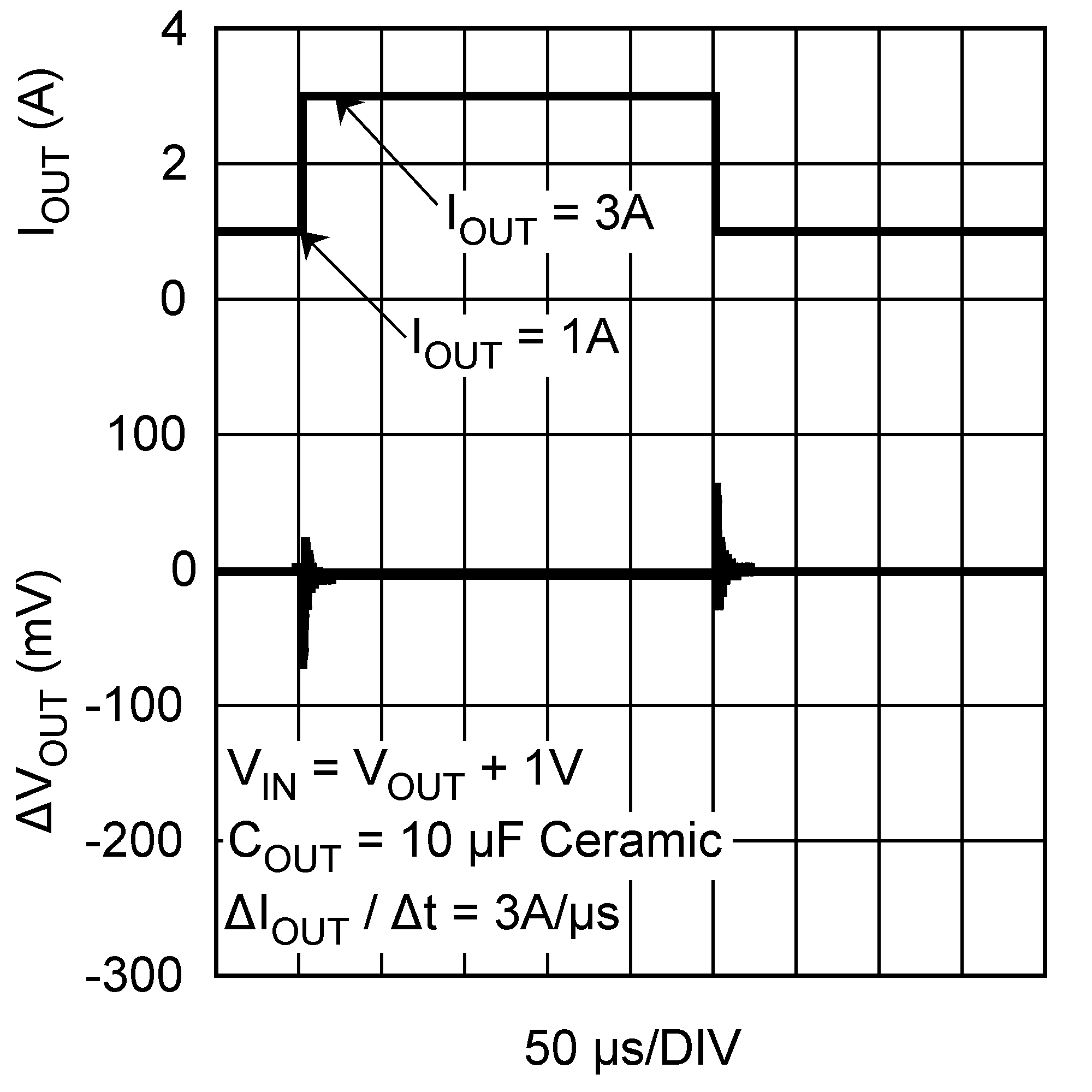

8.2.3 Application Curves

| COUT = 10-μF Ceramic | ||