SLLSEI2A September 2017 – December 2017 SN55HVD233-SP

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Driver Electrical Characteristics

- 7.6 Receiver Electrical Characteristics

- 7.7 Driver Switching Characteristics

- 7.8 Receiver Switching Characteristics

- 7.9 Device Switching Characteristics

- 7.10 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- HKX|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

over operating junction temperature unless otherwise noted(1)(2)| MIN | MAX | UNIT | ||||

|---|---|---|---|---|---|---|

| VCC | Supply voltage | –0.3 | 7 | V | ||

| Voltage at any bus pin (CANH or CANL) | –16 | 16 | V | |||

| Voltage input, transient pulse, CANH and CANL, through 100 Ω (see Figure 18) | –100 | 100 | V | |||

| VI | Input voltage, (D, RS, LBK) | –0.5 | 7 | V | ||

| VO | Output voltage, (R) | –0.5 | 7 | V | ||

| IO | Receiver output current | –10 | 10 | mA | ||

| TJ | Operating junction temperature | 150 | °C | |||

| Tstg | Storage temperature | –65 | 150 | °C | ||

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground pin.

7.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | CANH, CANL, and GND | ±14000 | V |

| Other pins | ±4000 | ||||

| Charged-device model (CDM), per JEDEC specification JESD22-C101, all pins(2) | ±500 | ||||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VCC | Supply voltage | 3 | 3.6 | V | ||

| Voltage at any bus pin (separately or common mode) | –7 | 12 | V | |||

| VIH | High-level input voltage | D, LBK | 2 | 5.5 | V | |

| VIL | Low-level input voltage | D, LBK | 0 | 0.8 | V | |

| VID | Differential input voltage | –6 | 6 | V | ||

| Resistance from RS to ground for slope control | 0 | 50 | kΩ | |||

| VI(RS) | Input voltage at RS for standby | 0.75 VCC | 5.5 | V | ||

| IOH | High-level output current | Driver | –50 | mA | ||

| Receiver | –10 | |||||

| IOL | Low-level output current | Driver | 50 | mA | ||

| Receiver | 10 | |||||

| TJ | Operating junction temperature(1) | –55 | 125 | °C | ||

(1) Maximum junction temperature operation is allowed as long as the device maximum junction temperature is not exceeded.

7.4 Thermal Information

| THERMAL METRIC(2)(1) | SN55HVD233-SP | UNIT | |

|---|---|---|---|

| HKX (CFP) | |||

| 8 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 97.1 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 21.5 | °C/W |

| RθJB | Junction-to-board thermal resistance | 79.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 13.7 | °C/W |

| ψJB | Junction-to-board characterization parameter | 73.6 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 7.0 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) All values except RθJC were taken on a JEDEC-51 standard High-K PCB using a nominal lead form. Differences in lead form, component density, or PCB design can affect these values.

7.5 Driver Electrical Characteristics

The specifications shown below are valid across temperature range of –55°C to 125°C pre-radiation and 25°C post-radiation. When different, the post-radiation values are shown in a separate row specified by the corresponding RHA level (L = 50 krad).| PARAMETER | TEST CONDITIONS | SUBGROUP(2) | MIN | TYP(1) | MAX | UNIT | ||||

|---|---|---|---|---|---|---|---|---|---|---|

| VO(D) | Bus output voltage (dominant) | CANH | V(D) = 0 V, V(RS) = 0 V, see Figure 12 and Figure 13 | [1, 2, 3] | 2.4 | VCC | V | |||

| CANL | [1, 2, 3] | 0.5 | 1.25 | |||||||

| VO | Bus output voltage (recessive) | CANH | V(D) = 3 V, V(RS) = 0 V, see Figure 12 and Figure 13 | 2.3 | V | |||||

| CANL | 2.3 | |||||||||

| VOD(D) | Differential output voltage (dominant) | V(D) = 0 V, V(RS) = 0 V, see Figure 12 and Figure 13 | [1, 2, 3] | 1.5 | 2 | 3 | V | |||

| L | 1.4 | |||||||||

| V(D) = 0 V, V(RS) = 0 V, see Figure 13 and Figure 14 | [1, 2, 3] | 1.2 | 2 | 3 | ||||||

| VOD | Differential output voltage (recessive) | V(D) = 3 V, V(RS) = 0 V, see Figure 12 and Figure 13 | [1, 2, 3] | –120 | 12 | mV | ||||

| V(D) = 3 V, V(RS) = 0 V, no load | [1, 2, 3] | –0.5 | 0.05 | V | ||||||

| VOC(pp) | Peak-to-peak common-mode output voltage | See Figure 20 | 1 | V | ||||||

| IIH | High-level input current | D, LBK | V(D) = 2 V | [1, 2, 3] | –30 | 30 | μA | |||

| IIL | Low-level input current | D, LBK | V(D) = 0.8 V | [1, 2, 3] | –30 | 30 | μA | |||

| IOS | Short-circuit output current | V(CANH) = –7 V, CANL open, see Figure 23 | [1, 2, 3] | –250 | mA | |||||

| V(CANH) = 12 V, CANL open, see Figure 23 | [1, 2, 3] | 1 | ||||||||

| V(CANL) = –7 V, CANH open, see Figure 23 | [1, 2, 3] | –1 | ||||||||

| V(CANL) = 12 V, CANH open, see Figure 23 | [1, 2, 3] | 250 | ||||||||

| CO | Output capacitance | See receiver input capacitance | ||||||||

| IIRS(s) | RS input current for standby | V(RS) = 0.75 VCC | [1, 2, 3] | –10 | μA | |||||

| ICC | Supply current | Standby | V(RS) = VCC, V(D) = VCC, V(LBK) = 0 V | [1, 2, 3] | 200 | 600 | μA | |||

| Dominant | V(D) = 0 V, no load, V(LBK) = 0 V, RS = 0 V | [1, 2, 3] | 6 | mA | ||||||

| Recessive | V(D) = VCC, no load, V(LBK) = 0 V, V(RS) = 0 V | [1, 2, 3] | 6 | |||||||

(1) All typical values are at 25°C and with a 3.3-V supply.

(2) For subgroup definitions, please see Table 1.

7.6 Receiver Electrical Characteristics

The specifications shown below are valid across temperature range of –55°C to 125°C pre-radiation and 25°C post-radiation. When different, the post-radiation values are shown in a separate row specified by the corresponding RHA level (L = 50 krad).| PARAMETER | TEST CONDITIONS | SUBGROUP(2) | MIN | TYP(1) | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|---|

| VIT+ | Positive-going input threshold voltage | V(LBK) = 0 V, see Table 2 | [1, 2, 3] | 750 | 900 | mV | |||

| VIT– | Negative-going input threshold voltage | [1, 2, 3] | 500 | 650 | mV | ||||

| Vhys | Hysteresis voltage (VIT+ – VIT–) | 100 | mV | ||||||

| VOH | High-level output voltage | IO = –4 mA, see Figure 17 | [1, 2, 3] | 2.4 | V | ||||

| VOL | Low-level output voltage | IO = 4 mA, see Figure 17 | [1, 2, 3] | 0.4 | V | ||||

| II | Bus input current | V(CANH) or V(CANL) = 12 V | Other bus pin = 0 V, V(D) = 3 V, V(LBK) = 0 V, V(RS) = 0 V |

[1, 2, 3] | 150 | 500 | μA | ||

| V(CANH) or V(CANL) = 12 V, VCC = 0 V |

[1, 2, 3] | 150 | 600 | ||||||

| CANH or CANL = –7 V | [1, 2, 3] | –610 | –100 | ||||||

| CANH or CANL = –7 V, VCC = 0 V |

[1, 2, 3] | –450 | –100 | ||||||

| CI | Input capacitance (CANH or CANL) | Pin-to-ground, VI = 0.4 sin(4E6πt) + 0.5 V, V(D) = 3 V, V(LBK) = 0 V |

40 | pF | |||||

| CID | Differential input capacitance | Pin-to-pin, VI = 0.4 sin(4E6πt) + 0.5 V, V(D) = 3 V, V(LBK) = 0 V |

20 | pF | |||||

| RID | Differential input resistance | V(D) = 3 V, V(LBK) = 0 V | [4, 5, 6] | 40 | 105 | kΩ | |||

| RIN | Input resistance (CANH or CANL) | [4, 5, 6] | 20 | 55 | kΩ | ||||

| ICC | Supply current | Standby | V(RS) = VCC, V(D) = VCC, V(LBK) = 0 V | [1, 2, 3] | 200 | 600 | μA | ||

| Dominant | V(D) = 0 V, no load, V(RS) = 0 V, V(LBK) = 0 V | [1, 2, 3] | 6 | mA | |||||

| Recessive | V(D) = VCC, no load, V(RS) = 0 V, V(LBK) = 0 V | [1, 2, 3] | 6 | mA | |||||

(1) All typical values are at 25°C and with a 3.3-V supply.

(2) For subgroup definitions, please see Table 1.

7.7 Driver Switching Characteristics

The specifications shown below are valid across temperature range of –55°C to 125°C pre-radiation and 25°C post-radiation. When different, the post-radiation values are shown in a separate row specified by the corresponding RHA level (L = 50 krad).| PARAMETER | TEST CONDITIONS | SUBGROUP(2) | MIN | TYP(1) | MAX | UNIT | |

|---|---|---|---|---|---|---|---|

| tPLH | Propagation delay time, low-to-high-level output |

V(RS) = 0 V, see Figure 15 | [9, 10, 11] | 35 | 85 | ns | |

| RS with 10 kΩ to ground, see Figure 15 | [9, 10, 11] | 70 | 125 | ||||

| RS with 50 kΩ to ground, see Figure 15 | [9, 10, 11] | 500 | 870 | ||||

| tPHL | Propagation delay time, high-to-low-level output |

V(RS) = 0 V, see Figure 15 | [9, 10, 11] | 70 | 120 | ns | |

| RS with 10 kΩ to ground, see Figure 15 | [9, 10, 11] | 130 | 180 | ||||

| RS with 50 kΩ to ground, see Figure 15 | [9, 10, 11] | 870 | 1200 | ||||

| tsk(p) | Pulse skew (|tPHL – tPLH|) | V(RS) = 0 V, see Figure 15 | 35 | ns | |||

| RS with 10 kΩ to ground, see Figure 15 | 60 | ||||||

| RS with 50 kΩ to ground, see Figure 15 | 370 | ||||||

| tr | Differential output signal rise time | V(RS) = 0 V, see Figure 15 | [9, 10, 11] | 20 | 70 | ns | |

| tf | Differential output signal fall time | [9, 10, 11] | 20 | 70 | ns | ||

| tr | Differential output signal rise time | RS with 10 kΩ to ground, see Figure 15 | [9, 10, 11] | 30 | 135 | ns | |

| tf | Differential output signal fall time | [9, 10, 11] | 30 | 135 | ns | ||

| tr | Differential output signal rise time | RS with 50 kΩ to ground, see Figure 15 | [9, 10, 11] | 350 | 1400 | ns | |

| tf | Differential output signal fall time | [9, 10, 11] | 350 | 1400 | ns | ||

| ten(s) | Enable time from standby to dominant | See Figure 19 | [9, 10, 11] | 0.6 | 1.5 | μs | |

(1) All typical values are at 25°C and with a 3.3-V supply.

(2) For subgroup definitions, please see Table 1.

7.8 Receiver Switching Characteristics

The specifications shown below are valid across temperature range of –55°C to 125°C pre-radiation and 25°C post-radiation. When different, the post-radiation values are shown in a separate row specified by the corresponding RHA level (L = 50 krad).| PARAMETER | TEST CONDITIONS | SUBGROUP(2) | MIN | TYP(1) | MAX | UNIT | |

|---|---|---|---|---|---|---|---|

| tPLH | Propagation delay time, low-to-high-level output | See Figure 17 | [9, 10, 11] | 35 | 105 | ns | |

| tPHL | Propagation delay time, high-to-low-level output | [9, 10, 11] | 35 | 105 | ns | ||

| tsk(p) | Pulse skew (|tPHL – tPLH|) | 7 | ns | ||||

| tr | Output signal rise time | 2 | ns | ||||

| tf | Output signal fall time | 2 | ns | ||||

(1) All typical values are at 25°C and with a 3.3-V supply.

(2) For subgroup definitions, please see Table 1.

7.9 Device Switching Characteristics

The specifications shown below are valid across temperature range of –55°C to 125°C pre-radiation and 25°C post-radiation. When different, the post-radiation values are shown in a separate row specified by the corresponding RHA level (L = 50 krad).| PARAMETER | TEST CONDITIONS | SUBGROUP(2) | MIN | TYP(1) | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|---|

| t(LBK) | Loopback delay, driver input to receiver output | See Figure 22 | 7.5 | ns | ||||

| t(loop1) | Total loop delay, driver input to receiver output, recessive to dominant | V(RS) at 0 V, see Figure 21 | [9, 10, 11] | 70 | 150 | ns | ||

| V(RS) with 10 kΩ to ground, see Figure 21 | [9, 10, 11] | 105 | 225 | |||||

| V(RS) with 50 kΩ to ground, see Figure 21 | [9, 10, 11] | 500 | 600 | |||||

| t(loop2) | Total loop delay, driver input to receiver output, dominant to recessive | V(RS) at 0 V, See Figure 21 | [9, 10, 11] | 70 | 150 | ns | ||

| V(RS) with 10 kΩ to ground, see Figure 21 | [9, 10, 11] | 105 | 225 | |||||

| V(RS) with 50 kΩ to ground, see Figure 21 | [9, 10, 11] | 500 | 600 | |||||

(1) All typical values are at 25°C and with a 3.3-V supply.

(2) For subgroup definitions, please see Table 1.

Table 1. Quality Conformance Inspection(1)

| SUBGROUP | DESCRIPTION | TEMPERATURE (°C) |

|---|---|---|

| 1 | Static tests at | 25 |

| 2 | Static tests at | 125 |

| 3 | Static tests at | –55 |

| 4 | Dynamic tests at | 25 |

| 5 | Dynamic tests at | 125 |

| 6 | Dynamic tests at | –55 |

| 7 | Functional tests at | 25 |

| 8A | Functional tests at | 125 |

| 8B | Functional tests at | –55 |

| 9 | Switching tests at | 25 |

| 10 | Switching tests at | 125 |

| 11 | Switching tests at | –55 |

(1) MIL-STD-883, Method 5005 - Group A

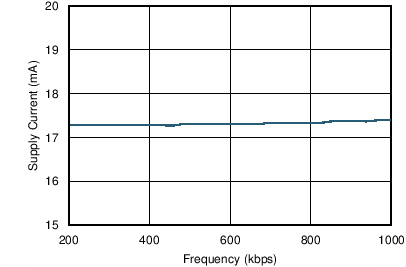

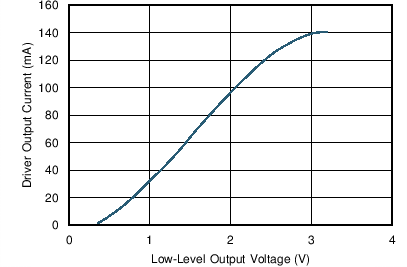

7.10 Typical Characteristics

| V(RS), V(LBK) = 0 V |

Temperature

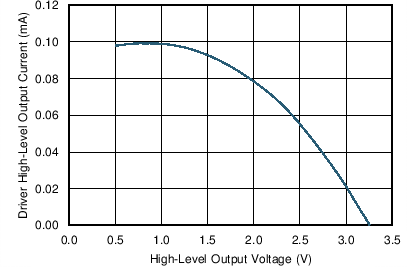

| VCC = 3.3 V | V(RS), V(LBK) = 0 V | TA = 25°C |

| 60-Ω load |

| VCC = 3.3 V | V(RS), V(LBK) = 0 V | TA = 25°C |

High-Level Output Voltage

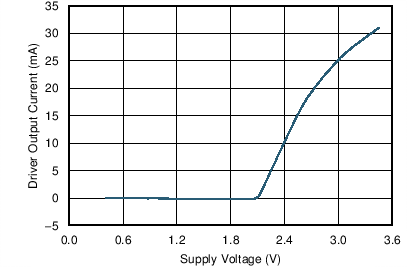

| V(RS), V(LBK) = 0 V | TA = 25°C | RL = 60 Ω |

| V(RS), V(LBK) = 0 V |

Temperature

| VCC = 3.3 V | V(RS), V(LBK) = 0 V | TA = 25°C |

Low-Level Output Voltage

| RL = 60 Ω | V(RS), V(LBK) = 0 V | |

Temperature