SLLS396G SEPTEMBER 1999 – December 2015 SN65LVDS104 , SN65LVDS105

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Selection Guide to LVDS Repeaters

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings—JEDEC

- 7.3 ESD Ratings—MIL-STD

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 SN65LVDS104 Electrical Characteristics

- 7.7 SN65LVDS105 Electrical Characteristics

- 7.8 SN65LVDS104 Switching Characteristics

- 7.9 SN65LVDS105 Switching Characteristics

- 7.10 Dissipation Ratings

- 7.11 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 Point-to-Point Communications

- 10.2.2 Design Requirements

- 10.2.3

Detailed Design Procedure

- 10.2.3.1 Bypass Capacitance

- 10.2.3.2 Driver Supply Voltage

- 10.2.3.3 Driver Input Voltage

- 10.2.3.4 Driver Output Voltage

- 10.2.3.5 Interconnecting Media

- 10.2.3.6 PCB Transmission Lines

- 10.2.3.7 Termination Resistor

- 10.2.3.8 Receiver Supply Voltage

- 10.2.3.9 Receiver Input Common-Mode Range

- 10.2.3.10 Receiver Input Signal

- 10.2.3.11 Receiver Output Signal

- 10.2.4 Application Curve

- 10.3 Multidrop Communications

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- PW|16

- D|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

10.1 Application Information

The SN65LVDS049 is a dual LVDS driver-receiver pair. The functionality of these devices is simple, yet extremely flexible, leading to their use in designs ranging from wireless base stations to desktop computers. The varied class of potential applications share features and applications discussed in the paragraphs below.

10.2 Typical Application

10.2.1 Point-to-Point Communications

The most basic application for LVDS buffers, as found in this data sheet, is for point-to-point communications of digital data, as shown in Figure 37.

Figure 37. Point-to-Point Topology

Figure 37. Point-to-Point Topology

A point-to-point communications channel has a single transmitter (driver) and a single receiver. This communications topology is often referred to as simplex. In Figure 37 the driver receives a single-ended input signal and the receiver outputs a single-ended recovered signal. The LVDS driver converts the single-ended input to a differential signal for transmission over a balanced interconnecting media of 100-Ω characteristic impedance. The conversion from a single-ended signal to an LVDS signal retains the digital data payload while translating to a signal whose features are more appropriate for communication over extended distances or in a noisy environment.

10.2.2 Design Requirements

For this design example, use the parameters listed in Table 3.

Table 3. Design Parameters

| DESIGN PARAMETER | EXAMPLE VALUE |

|---|---|

| Driver supply voltage (VCCD) | 3 to 3.6 V |

| Driver input voltage | 0.8 to VCCDV |

| Driver signaling rate | DC to 400 Mbps |

| Interconnect characteristic impedance | 100 Ω |

| Termination resistance | 100 Ω |

| Receiver supply voltage (VCCR) | 3 to 3.6 V |

| Number of receiver nodes | 1 |

| Receiver input voltage | 0 to VCCR – 0.8 V |

| Ground shift between driver and receiver | ±1 |

10.2.3 Detailed Design Procedure

10.2.3.1 Bypass Capacitance

Bypass capacitors play a key role in power distribution circuitry. At low frequencies, power supply offers very low-impedance paths between the terminals. However, as higher frequency currents propagate through power traces, the source is quite often incapable of maintaining a low-impedance path to ground. Bypass capacitors are used to address this shortcoming. Usually, large bypass capacitors (10 μF to 1000 μF) at the board level do a good job into the kHz range. Due to their size and length of their leads, large capacitors tend to have large inductance values at the switching frequencies. To solve this problem, smaller capacitors must be (nF to μF range) installed locally next to the integrated circuit.

Multilayer ceramic chip or surface-mount capacitors (size 0603 or 0805) minimize lead inductances of bypass capacitors in high-speed environments, because their lead inductance is about 1 nH. For comparison purposes, a typical capacitor with leads has a lead inductance of approximately 5 nH.

The value of the bypass capacitors used locally with LVDS chips can be determined by the following formula according to Johnson, equations 8.18 to 8.21. A conservative rise time of 4 ns and a worst-case change in supply current of 100 mA covers the whole range of LVDS devices offered by TI. In this example, the maximum power supply noise tolerated is 100 mV. However, this figure varies depending on the noise budget available in your design.

The following example, Figure 38, lowers lead inductance and covers intermediate frequencies between the board-level capacitor (>10 μF) and the value of capacitance found in Equation 2 (0.004 μF). You must place the smallest value of capacitance as close as possible to the chip.

Figure 38. Recommended LVDS Bypass Capacitor Layout

Figure 38. Recommended LVDS Bypass Capacitor Layout

10.2.3.2 Driver Supply Voltage

The device can support operation with a supply as low as 3 V and as high as 3.6 V. As shown in the SN65LVDS104 Electrical Characteristics and SN65LVDS105 Electrical Characteristics, the differential output voltage is nominally 350 mV over the complete output range. The minimum output voltage stays within the specified LVDS limits (247 mV to 454 mV) for a 3.3-V supply.

10.2.3.3 Driver Input Voltage

The driver will operate with a decision threshold of approximately 1.4 V for LVTTL input signals.

10.2.3.4 Driver Output Voltage

The SN65LVDS049 driver output is a 1.2-V common-mode voltage, with a nominal differential output signal of 350 mV. This 350 mV is the absolute value of the differential swing (VOD = |V+ – V–|). The peak-to-peak differential voltage is twice this value, or 700 mV.

10.2.3.5 Interconnecting Media

The physical communication channel between the driver and the receiver may be any balanced paired metal conductors meeting the requirements of the LVDS standard. This media may be a twisted-pair, twinax, flat ribbon cable, or PCB traces. The nominal characteristic impedance of the interconnect must be from 100 Ω to 120 Ω with variation no more than 10% (90 Ω to 132 Ω).

10.2.3.6 PCB Transmission Lines

As per SNLA187, Figure 39 depicts several transmission line structures commonly used in PCBs. Each structure consists of a signal line and a return path with uniform cross-section along its length. A microstrip is a signal trace on the top (or bottom) layer, separated by a dielectric layer from its return path in a ground or power plane. A stripline is a signal trace in the inner layer, with a dielectric layer in between a ground plane above and below the signal trace. The dimensions of the structure along with the dielectric material properties determine the characteristic impedance of the transmission line (also called controlled-impedance transmission line).

When two signal lines are placed near one another, they form a pair of coupled transmission lines. Figure 39 shows examples of edge-coupled microstrips, and edge-coupled or broad-side-coupled striplines. When excited by differential signals, the coupled transmission line is referred to as a differential pair. The characteristic impedance of each line is called odd-mode impedance. The sum of the odd-mode impedances of each line is the differential impedance of the differential pair. In addition to the trace dimensions and dielectric material properties, the spacing between the two traces determines the mutual coupling and impacts the differential impedance. When the two lines are immediately adjacent; for example, if S is less than 2×W, the differential pair is called a tightly-coupled differential pair. To maintain constant differential impedance along the length, it is important to keep the trace width and spacing uniform along the length, as well as maintain good symmetry between the two lines.

Figure 39. Controlled-Impedance Transmission Lines

Figure 39. Controlled-Impedance Transmission Lines

10.2.3.7 Termination Resistor

As shown earlier in Figure 37, an LVDS communication channel employs a current source driving a transmission line which is terminated with a resistive load. This load serves to convert the transmitted current into a voltage at the receiver input. To ensure good signal integrity, the termination resistance must be matched to the characteristic impedance of the transmission line. The designer must ensure that the termination resistance is within 10% of the nominal media characteristic impedance. If the transmission line is targeted for 100-Ω impedance, the termination resistance must be from 90 Ω to 110 Ω.

The line termination resistance must be located as close as possible to the receiver, thereby minimizing the stub length from the resistor to the receiver.

When a multidrop topology is used, line termination resistors are typically placed at the end (or ends) of the transmission line.

10.2.3.8 Receiver Supply Voltage

The receiver can support operation with a supply as low as 3 V and as high as 3.6 V.

10.2.3.9 Receiver Input Common-Mode Range

Receiver supports common-mode values in the range of 0.05 V to 2.35 V. This is assuming 100 mV differential signal and a 3.3 V supply.

The driver has an output common-mode range of 1.2 V. Using the receiver discussed here, we see that valid operation of the communication link will occur when the ground difference between transmitter and receiver is within approximately ±1 V. The use of differential signaling in LVDS allows operation in an environment where the combination of ground difference and common-mode noise result in a common-mode difference between transmitter and receiver of 1 V. This 1-V potential difference hints at the intended application of LVDS circuits.

Standards such as RS-485 support potential differences of almost 10 V, allowing for communication over distances of greater than 1 km. The intended application of LVDS devices is more moderate distances, such as those from chip to chip on a board, board to board in a rack, or from rack to nearby rack. When the 1-V potential difference is not adequate, yet the high-speed and low-voltage features of LVDS are still needed, the designer can choose from either M-LVDS devices available from TI, or from LVDS devices with extended common-mode ranges, such as the SN65LVDS33.

10.2.3.10 Receiver Input Signal

The LVDS receivers herein comply with the LVDS standard and correctly determine the bus state when the differential input voltage is greater than 100 mV (HI output) or less than –100 mV (LO output).

10.2.3.11 Receiver Output Signal

Receiver outputs comply with LVTTL output voltage standards when the supply voltage is within the range of 3 V to 3.6 V.

10.2.4 Application Curve

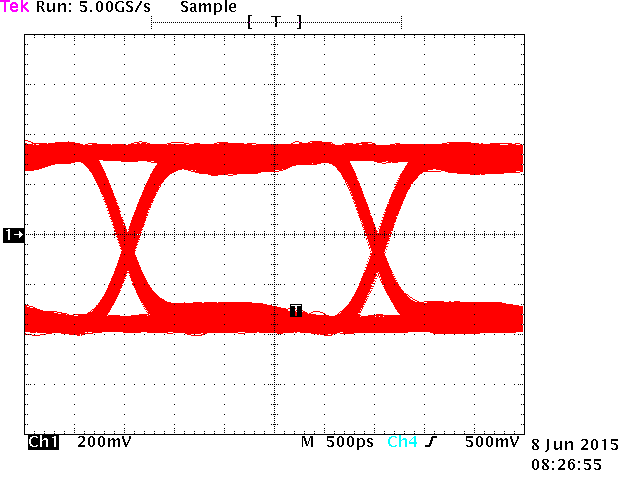

Figure 40. Typical Driver Output Eye Pattern in Point-to-Point System

Figure 40. Typical Driver Output Eye Pattern in Point-to-Point System

10.3 Multidrop Communications

A second common application of LVDS buffers is a multidrop topology. In a multidrop configuration, a single driver and a shared bus are present, along with two or more receivers (with a maximum permissible number of 32 receivers). Figure 41 shows an example of a multidrop system.

Figure 41. Multidrop Topology

Figure 41. Multidrop Topology

10.3.1 Design Requirements

For this design example, use the parameters listed in Table 4

Table 4. Design Parameters

| DESIGN PARAMETERS | EXAMPLE VALUE |

|---|---|

| Driver supply voltage (VCCD ) | 3 to 3.6 V |

| Driver input voltage | 0.8 to VCCD V |

| Driver signaling rate | DC to 400 Mbps |

| Interconnect characteristic impedance | 100 Ω |

| Termination resistance | 100 Ω |

| Number of receiver nodes | 2 to 32 |

| Receiver supply voltage (VCCR) | 3 to 3.6 V |

| Receiver input voltage | 0 to VCCR – 0.8 V |

| Receiver signaling rate | DC to 400 Mbps |

| Ground shift between driver and receiver | ±1 V |

10.3.2 Detailed Design Procedure

10.3.2.1 Interconnecting Media

The interconnect in a multidrop system differs considerably from a point-to-point system. While point-to-point interconnects are straightforward, and well understood, the bus type architecture encountered with multidrop systems requires more careful attention. We will use Figure 41 to explore these details.

The most basic multidrop system would include a single driver, located at a bus origin, with multiple receiver nodes branching off the main line, and a final receiver at the end of the transmission line, co-located with a bus termination resistor. While this would be the most basic multidrop system, it has several considerations not yet explored.

The location of the transmitter at one bus end allows the design concerns to be simplified, but this comes at the cost of flexibility. With a transmitter located at the origin, a single bus termination at the far-end is required. The far-end termination absorbs the incident traveling wave. The flexibility lost with this arrangement is thus: if the single transmitter needed to be relocated on the bus, at any location other than the origin, we would be faced with a bus with one open-circuited end, and one properly terminated end. Locating the transmitter say in the middle of the bus may be desired to reduce (by ½) the maximum flight time from the transmitter to receiver.

Another new feature in Figure 41 is clear in that every node branching off the main line results in stubs. The stubs must be minimized in any case, but have the unintended effect of locally changing the loaded impedance of the bus.

To a good approximation, the characteristic transmission line impedance of an unloaded multipoint or multidrop bus is defined by √L/C, where L is the inductance per unit length and C is the capacitance per unit length. As capacitance is added to the bus in the form of devices and interconnections, the bus characteristic impedance is lowered. This may result in signal reflections from the impedance mismatch between the unloaded and loaded segments of the bus.

If the number of loads is constant and can be distributed evenly along the line, reflections can be reduced by changing the bus termination resistors to match the loaded characteristic impedance. Normally, the number of loads are not constant or distributed evenly and the reflections resulting from any mismatching must be accounted for in the noise budget.