SCLS068G November 1988 – July 2022 SN74HCT273

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- DB|20

- NS|20

- N|20

- DW|20

- PW|20

Thermal pad, mechanical data (Package|Pins)

Orderable Information

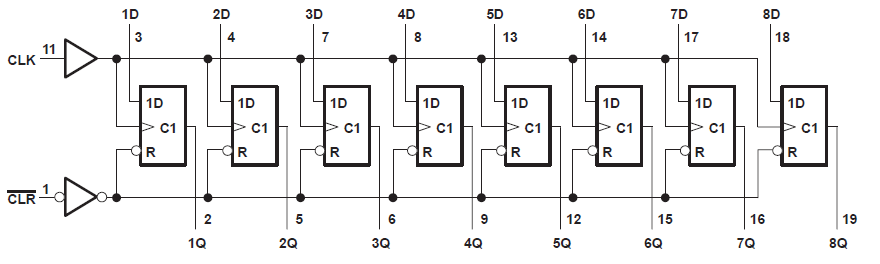

3 Description

These devices are positive-edge-triggered D-type flip-flops with a common enable input. The ’HCT273 devices are similar to the ’HCT377 devices, but feature a common clear enable (CLR) input instead of a latched clock.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| SN74HCT273DW | SOIC (20) | 12.80 mm × 7.50 mm |

| SN74HCT273DB | SSOP (20) | 7.20 mm × 5.30 mm |

| SN74HCT273N | PDIP (20) | 25.40 mm × 6.35 mm |

| SN74HCT273NS | SO (20) | 15.00 mm × 5.30 mm |

| SN74HCT273PW | TSSOP (20) | 6.50 mm × 4.40 mm |

(1) For all available packages, see

the orderable addendum at the end of the data sheet.

Logic Diagram, (postive logic)

Logic Diagram, (postive logic) Logic Diagram, Each Flip Flop (positive logic)

Logic Diagram, Each Flip Flop (positive logic)