SNAS647D February 2015 – March 2016 TDC7200

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Companion Device

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 Register Initialization

- 8.6.2 CONFIG1: Configuration Register 1 R/W (address = 00h) [reset = 0h]

- 8.6.3 CONFIG2: Configuration Register 2 R/W (address = 01h) [reset = 40h]

- 8.6.4 INT_STATUS: Interrupt Status Register (address = 02h) [reset = 00h]

- 8.6.5 INT_MASK: Interrupt Mask Register R/W (address = 03h) [reset = 07h]

- 8.6.6 COARSE_CNTR_OVF_H: Coarse Counter Overflow High Value Register (address = 04h) [reset = FFh]

- 8.6.7 COARSE_CNTR_OVF_L: Coarse Counter Overflow Low Value Register (address = 05h) [reset = FFh ]

- 8.6.8 CLOCK_CNTR_OVF_H: Clock Counter Overflow High Register (address = 06h) [reset = FFh]

- 8.6.9 CLOCK_CNTR_OVF_L: Clock Counter Overflow Low Register (address = 07h) [reset = FFh]

- 8.6.10 CLOCK_CNTR_STOP_MASK_H: CLOCK Counter STOP Mask High Value Register (address = 08h) [reset = 00h]

- 8.6.11 CLOCK_CNTR_STOP_MASK_L: CLOCK Counter STOP Mask Low Value Register (address = 09h) [reset = 00h]

- 8.6.12 TIME1: Time 1 Register (address: 10h) [reset = 00_0000h]

- 8.6.13 CLOCK_COUNT1: Clock Count Register (address: 11h) [reset = 00_0000h]

- 8.6.14 TIME2: Time 2 Register (address: 12h) [reset = 00_0000h]

- 8.6.15 CLOCK_COUNT2: Clock Count Register (address: 13h) [reset = 00_0000h]

- 8.6.16 TIME3: Time 3 Register (address: 14h) [reset = 00_0000h]

- 8.6.17 CLOCK_COUNT3: Clock Count Registers (address: 15h) [reset = 00_0000h]

- 8.6.18 TIME4: Time 4 Register (address: 16h) [reset = 00_0000h]

- 8.6.19 CLOCK_COUNT4: Clock Count Register (address: 17h) [reset = 00_0000h]

- 8.6.20 TIME5: Time 5 Register (address: 18h) [reset = 00_0000h]

- 8.6.21 CLOCK_COUNT5: Clock Count Register (address: 19h) [reset = 00_0000h]

- 8.6.22 TIME6: Time 6 Register (address: 1Ah) [reset = 00_0000h]

- 8.6.23 CALIBRATION1: Calibration 1 Register (address: 1Bh ) [reset = 00_0000h]

- 8.6.24 CALIBRATION2: Calibration 2 Register (address: 1Ch ) [reset = 00_0000h]

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PW|14

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8 Detailed Description

8.1 Overview

The TDC7200 is a stopwatch IC used to measure time between a single event (edge on START pin) and multiple subsequent events (edge on STOP pin). An event from a START pulse to a STOP pulse is also known as time-of-flight, or TOF for short. The device has an internal time base that is used to measure time with accuracy in the order of picoseconds. This accuracy makes the TDC7200 ideal for application such as flow meter, where zero and low flow measurements require high accuracy in the picoseconds range.

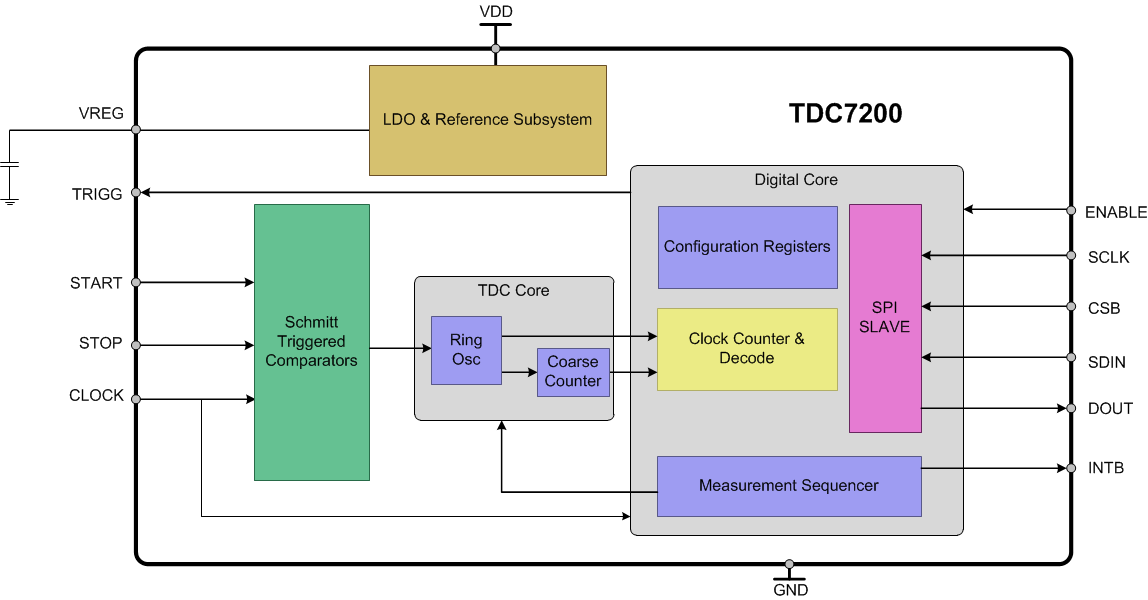

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 LDO

The LDO (low-dropout) is an internal supply voltage regulator for the TDC7200. No external circuitry needs to be connected to the output of this regulator other than the mandatory external decoupling capacitor.

Recommendations for the decoupling capacitor parameters:

- Type: ceramic

- Capacitance: 0.4 µF–2.7 µF (1 µF typical). If using a capacitor value outside the recommended range, the part may malfunction and can be damaged.

- ESR: 100 mΩ (max)

8.3.2 CLOCK

TDC7200 needs an external reference clock connected to the CLOCK pin. The external CLOCK is used to calibrate the internal time base accurately and therefore, the measurement accuracy is heavily dependent on the external CLOCK accuracy. This reference clock is also used by all digital circuits inside the device; thus, CLOCK has to be available and stable at all times when the device is enabled (ENABLE = HIGH).

Figure 15 shows the typical effect of the external CLOCK frequency on the measurement uncertainty. With a reference clock of 1MHz, the standard deviation of a set of measurement results is approximately 243ps. As the reference clock frequency is increased, the standard deviation (or measurement uncertainty) reduces. Therefore, using a reference clock of 16MHz is recommended for optimal performance.

Figure 15. Standard Deviation vs. CLOCK

Figure 15. Standard Deviation vs. CLOCK

8.3.3 Counters

8.3.3.1 Coarse and Clock Counters Description

Time measurements by the TDC7200 rely on two counters: the Coarse Counter and the Clock Counter. The Coarse Counter counts the number of times the ring oscillator (the TDC7200’s core time measurement mechanism) wraps, which is used to generate the results in the TIME1 to TIME6 registers.

The Clock Counter counts the number of integer clock cycles between START and STOP events and is used in Measurement Mode 2 only. The results for the Clock Counter are displayed in the CLOCK_COUNT1 to CLOCK_COUNT5 registers.

8.3.3.2 Coarse and Clock Counters Overflow

Once the coarse counter value has reached the corresponding value of the Coarse Counter Overflow registers, then its interrupt bit will be set to 1. In other words, if (TIMEn / 63) ≥ COARSE_CNTR_OVF, then COARSE_CNTR_OVF_INT = 1 (this interrupt bit is located in the INT_STATUS register). COARSE_CNTR_OVF = (COARSE_CNTR_OVF_H x 28 + COARSE_CNTR_OVF_L), and TIMEn refers to the TIME1 to TIME6 registers.

Similarly, once the clock counter value has reached the corresponding value of the Clock Counter Overflow registers, then its interrupt bit will be set to 1. In other words, if CLOCK_COUNTn > CLOCK_CNTR_OVF, then CLOCK_CNTR_OVF_INT = 1 (this interrupt bit is located in the INT_STATUS register). CLOCK_CNTR_OVF = (CLOCK_CNTR_OVF_H x 28 + CLOCK_CNTR_OVF_L), and CLOCK_COUNTn refers to the CLOCK_COUNT1 to CLOCK_COUNT5 registers.

As soon as there is an overflow detected, the running measurement will be terminated immediately.

8.3.3.3 Clock Counter STOP Mask

The value in the Clock Counter STOP Mask registers define the end of the mask window. The Clock Counter STOP Mask value will be referred to as CLOCK_CNTR_STOP_MASK = (CLOCK_CNTR_STOP_MASK_H x 28 + CLOCK_CNTR_STOP_MASK_L).

The Clock Counter is started by the first rising edge of the external CLOCK after the START signal (see Figure 18). All STOP signals occurring before the value set by the CLOCK_CNTR_STOP_MASK registers will be ignored. This feature can be used to help suppress wrong or unwanted STOP trigger signals.

For example, assume the following values:

- The first time-of-flight (TOF1), which is defined as the time measurement from the START to the 1st STOP = 19 μs.

- The second time-of-flight (TOF2), which is defined as the time measurement from the START to the 2nd STOP = 119 μs.

- CLOCK = 8 MHz

In this example, the TDC7200 will provide a CLOCK_COUNT1 of approximately 152 (19 μs / tCLOCK), and CLOCK_COUNT2 of approximately 952 (119 μs / tCLOCK). If the user sets CLOCK_CNTR_STOP_MASK anywhere between 152 and 952, then the 1st STOP will be ignored and 2nd STOP will be measured.

The Clock Counter Overflow value (CLOCK_CNTR_OVF_H x 28 + CLOCK_CNTR_OVF_L) should always be higher than the Clock Counter STOP Mask value (CLOCK_CNTR_STOP_MASK_H x 28 + CLOCK_CNTR_STOP_MASK_L). Otherwise, the Clock Counter Overflow Interrupt will be set before the STOP mask time expires, and the measurement will be halted.

8.3.3.4 ENABLE

The ENABLE pin is used as a reset to all digital circuits in the TDC7200. Therefore, it is essential that the ENABLE pin sees a positive edge after the device has powered up. It is also important to ensure that there are no transients (glitches, etc.) on the ENABLE pin; such glitches could cause the device to RESET.

8.4 Device Functional Modes

8.4.1 Calibration

The time measurements performed by the TDC7200 are based on an internal time base which is represented as the LSB value of the TIME1 to TIME6 results registers. The typical LSB value can be seen in Electrical Characteristics. However, the actual value of the LSB can vary depending on environmental variables (temperature, systematic noise, etc.). This variation can introduce significant error into the measurement result. There is also an offset error in the measurement due to certain internal delays in the device.

In order to compensate for these errors and to calculate the actual LSB value, calibration needs to be performed. The TDC7200 calibration consists of two measurement cycles of the external CLOCK. The first is a measurement of a single clock cycle period of the external clock; the second measurement is for the number of external CLOCK periods set by the CALIBRATION2_PERDIOS in the CONFIG2 register. The results from the calibration measurements are stored in the CALIBRATION1 and CALIBRATION2 registers.

The two-point calibration is used to determine the actual LSB in real time in order to convert the TIME1 to TIME6 results from number of delays to a real time-of-flight (TOF) number. As discussed in the next sections, the calibrations will be used for calculating time-of-flight (TOF) in measurement modes 1 and 2.

8.4.2 Measurement Modes

8.4.2.1 Measurement Mode 1

In measurement mode 1 as shown in Figure 16, the TDC7200 performs the entire counting from START to the last STOP using its internal ring oscillator plus coarse counter. This method is recommended for measuring shorter time durations of < 500 ns. Using measurement mode 1 for measuring time > 500ns decreases accuracy of the measurement (as shown in Figure 17), and is not recommended.

Figure 16. Measurement Mode 1

Figure 16. Measurement Mode 1

Figure 17. Measurement Mode 1 Standard Deviation vs. Measured Time-of-Flight

Figure 17. Measurement Mode 1 Standard Deviation vs. Measured Time-of-Flight

8.4.2.1.1 Calculating Time-of-Flight (Measurement Mode 1)

For measurement mode 1, the time-of-flight (TOF) between the START to the nth STOP can be calculated using Equation 1:

where

- TOFn [sec] = time-of-flight measurement from the START to the nth STOP

- TIMEn = nth TIME measurement given by the TIME1 to TIME6 registers

- normLSB [sec] = normalized LSB value from calibration

- CLOCKperiod [sec] = external CLOCK period

- CALIBRATION1 [count] = TDC count for first calibration cycle

- CALIBRATION2 [count] = TDC count for second calibration cycle

- CALIBRATION2_PERIODS = setting for the second calibration cycle; located in register CONFIG2

For example, assume the time-of-flight between the START to the 1st STOP is desired, and the following readouts were obtained:

- CALIBRATION2 = 21121 (decimal)

- CALIBRATION1 = 2110 (decimal)

- CALIBRATION2_PERIODS = 10

- CLOCK = 8MHz

- TIME1 = 4175 (decimal)

Therefore, the calculation for time-of-flight is:

- calCount = (21121 – 2110) / (10 – 1) = 2112.33

- normLSB = (1/8MHz) / (2112.33) = 5.917 x 10-11

- TOF1 = (4175)(5.917 x 10-11) = 247.061 ns

8.4.2.2 Measurement Mode 2

In measurement mode 2, the internal ring oscillator of the TDC7200 is used only to count fractional parts of the total measured time. As shown in Figure 18, the internal ring oscillator starts counting from when it receives the START signal until the first rising edge of the CLOCK. Then, the internal ring oscillator switches off, and the Clock counter starts counting the clock cycles of the external CLOCK input until a STOP pulse is received. The internal ring oscillator again starts counting from the STOP signal until the next rising edge of the CLOCK.

Figure 18. Measurement Mode 2

Figure 18. Measurement Mode 2

8.4.2.2.1 Calculating Time-of-Flight (TOF) (Measurement Mode 2)

The time-of-flight (TOF) between the START to the nth STOP can be calculated using Equation 2:

where

- TOFn [sec] = time-of-flight measurement from the START to the nth STOP

- TIME1 = time 1 measurement given by the TDC7200 register address 0x10

- TIME(n+1) = (n+1) time measurement, where n = 1 to 5 (TIME2 to TIME6 registers)

- normLSB [sec] = normalized LSB value from calibration

- CLOCK_COUNTn = nth clock count, where n = 1 to 5 (CLOCK_COUNT1 to CLOCK_COUNT5)

- CLOCKperiod [sec] = external CLOCK period

- CALIBRATION1 [count] = TDC count for first calibration cycle

- CALIBRATION2 [count] = TDC count for second calibration cycle

- CALIBRATION2_PERIODS = setting for the second calibration; located in register CONFIG2

For example, assume the time-of-flight between the START to the 1st STOP is desired, and the following readouts were obtained:

- CALIBRATION2 = 23133 (decimal)

- CALIBRATION1 = 2315 (decimal)

- CALIBRATION2_PERIODS = 10

- CLOCK = 8MHz

- TIME1 = 2147 (decimal)

- TIME2 = 201 (decimal)

- CLOCK_COUNT1 = 318 (decimal)

Therefore, the calculation for time-of-flight is:

8.4.3 Timeout

For one STOP, the TDC performs the measurement by counting from the START signal to the STOP signal. If no STOP signal is received, either the Clock Counter or Coarse Counter will overflow and will generate an interrupt (see Coarse and Clock Counters Overflow). If no START signal is received, the timer waits indefinitely for a START signal to arrive.

For multiple STOPs, the TDC performs the measurement by counting from the START signal to the last STOP signal. All earlier STOP signals are captured and stored into the corresponding Measurement Results registers (TIME1 to TIME6, CLOCK_COUNT1 to CLOCK_COUNT5, CALIBRATION1, CALIBRATION2). The minimum time required between two consecutive STOP signals is defined in the Recommended Operating Conditions table. The device can be programmed to measure up to 5 STOP signals by setting the NUM_STOP bits in the CONFIG2 register.

8.4.4 Multi-Cycle Averaging

In the Multi-Cycle Averaging Mode, the TDC7200 will perform a series of measurements on its own and will only send an interrupt to the MCU (for example, MSP430, C2000, etc) for wake up after the series has been completed. While waiting, the MCU can remain in sleep mode during the whole cycle (as shown in Figure 19).

Multi-Cycle Averaging Mode Setup and Conditions:

- The number of averaging cycles should be selected (1 to 128). This is done by programming the AVG_CYCLES bit in the CONFIG2 register.

- The results of all measurements are reported in the Measurement Results registers (TIME1 to TIME6, CLOCK_COUNT1 to CLOCK_COUNT5, CALIBRATION1, CALIBRATION2 registers). The CLOCK_COUNTn registers should be right shifted by the log2(AVG_CYCLES) before calculating the time-of-flight (TOF). For example, if using the multi-cycle averaging mode, Equation 2 should be rewritten as: TOFn = normLSB [TIME1 - TIME(n+1)] + [CLOCK_COUNTn >> log 2 (AVG_CYCLES)] x [CLOCKperiod]

- Following each average cycle, the TDC generates either a trigger event on the TRIGG pin after the calibration measurement to commence a new measurement or an interrupt on the INTB pin, indicating that the averaging sequence has completed.

This mode allows multiple measurements without MCU interaction, thus optimizing power consumption for the overall system.

Figure 19. Multi-Cycle Averaging Mode Example with 2 Averaging Cycles and 5 STOP Signals

Figure 19. Multi-Cycle Averaging Mode Example with 2 Averaging Cycles and 5 STOP Signals

8.4.5 START and STOP Edge Polarity

In order to achieve the highest measurement accuracy, having the same edge polarity for the START and STOP input signals is highly recommended. Otherwise, slightly different propagation delays due to symmetry shift between the rising and falling edge configuration will impact the measurement accuracy.

For highest measurement accuracy in measurement mode 2, it’s strongly recommended to choose for the START and STOP signal the “rising edge”. This is done by setting the START_EDGE and STOP_EDGE bits in the CONFIG1 register to 0.

8.4.6 Measurement Sequence

The TDC7200 is a stopwatch IC that measures time between a START and multiple STOP events. The measurement sequence of the TDC7200 is as follows:

- After powering up the device, the EN pin needs to be low. There is one low to high transition required while VDD is supplied for correct initialization of the device.

- MCU software requests a new measurement to be initiated via the SPI™ interface.

- After the start new measurement bit START_MEAS has been set in the CONFIG1 register, the TDC7200 generates a trigger signal on the TRIGG pin, which is typically used by the corresponding ultrasonic analog-front-end (such as the TDC1000) as start trigger for a measurement (for example, transmit signal for the ultrasonic burst)

- Immediately after sending the trigger, the TDC7200 enables the START pin and waits to receive the START pulse edge

- After receiving a START, the TDC resets the TRIGG pin

- The Clock counter is started after the next rising edge of the external clock signal (Measurement Mode 2). The Clock Counter STOP Mask registers (CLOCK_CNTR_STOP_MASK_H and CLOCK_CNTR_STOP_MASK_L) determine the length of the STOP mask window.

- After reaching the Clock Counter STOP Mask value, the STOP pin waits to receive a single or multiple STOP trigger signal from the analog-front-end (for example, detected echo signal of the ultrasonic burst signal)

- After the last STOP trigger has been received, the TDC will signal to the MCU via interrupt (INTB pin) that there are new measurement results waiting in the registers. START, STOP and TRIGG pin are disabled (in Multi-Cycle Averaging Mode, the TDC will start the next cycle automatically by generating a new TRIGG signal). Note: INTB must be utilized to determine TDC measurement completion; polling the INT_STATUS register to determine measurement completion is NOT recommended as it will interfere with the TDC measurement.

- After the results are retrieved, the MCU can then start a new measurement with the same register settings. This is done by just setting the START measurement bit via SPI. It is not required to drive the ENABLE pin low between measurements.

- The ENABLE pin can be taken low, if the time duration between measurements is long, and it is desired to put the TDC7200 in its lowest power state. However, upon taking ENABLE high again, the device will come up with its default register settings and will need to be configured via SPI.

8.4.7 Wait Times for TDC7200 Startup

The required wait time following the rising edge of the ENABLE pin of the TDC7200 is defined by three key times, as shown in Figure 20. All three times relate to the startup of the TDC7200’s internal LDO, which is power gated when the device is disabled for optimal power consumption. The first parameter, T1SPI_RDY, is the time after which the SPI interface is accessible. The second (T2LDO_SET1) parameter and third (T3LDO_SET2) parameter are related to the performance of a measurement made while the internal LDO is settling. The LDO supplies the TDC7200’s time measurement device, and a change in voltage on its supply during a measurement translates directly to an inaccuracy. It is therefore recommended to wait until the LDO is settled before time measurement begins.

The first time period relating to the measurement accuracy is T2LDO_SET1, the LDO settling time 1. This is the time after which the LDO has settled to within 0.3% of its final value. A 0.3% error translates to a worst case time error (due to the LDO settling) of 0.3% x tCLOCK, which is 375ps in the case of an 8MHz reference clock, or 187.5ps if a 16MHz clock is used. Finally, the time T3LDO_SET2 is the time after which the LDO has settled to its final value. For best performance, it is recommended that a time measurement is not started before T3LDO_SET2 to allow the LDO to fully settle. Typical times for T1SPI_RDY is 100 µs, for T2LDO_SET1 is 300 µs, and for T3LDO_SET2 is 1.5 ms.

Figure 20. VREG Startup Time

Figure 20. VREG Startup Time

8.5 Programming

8.5.1 Serial Peripheral Interface (SPI)

The serial interface consists of data input (DIN), data output (DOUT), serial interface clock (SCLK), and chip select bar (CSB). The serial interface is used to configure the TDC7200 parameters available in various configuration registers.

The communication on the SPI bus supports write and read transactions. A write transaction consists of a single write command byte, followed by single data byte. A read transaction consists of a single read command byte followed by 8 or 24 SCLK cycles. The write and read command bytes consist of a 1-bit auto-increment bit, a 1-bit read or write instruction, and a 6-bit register address. Figure 21 shows the SPI protocol for a transaction involving one byte of data (read or write).

Figure 21. SPI Protocol

Figure 21. SPI Protocol

8.5.1.1 CSB

CSB is an active-low signal and needs to be low throughout a transaction. That is, CSB should not pulse between the command byte and the data byte of a single transaction.

De-asserting CSB always terminates an ongoing transaction, even if it is not yet complete. Re-asserting CSB will always bring the device into a state ready for the next transaction, regardless of the termination status of a previous transaction.

8.5.1.2 SCLK

SPI clock can idle high or low. It is recommended to keep SCLK as clean as possible to prevent glitches from corrupting the SPI frame.

8.5.1.3 DIN

Data In (DIN) is driven by the SPI master by sending the command and the data byte to configure the TDC7200.

8.5.1.4 DOUT

Data Out (DOUT) is driven by the TDC7200 when the SPI master initiates a read transaction. When the TDC7200 is not being read out, the DOUT pin is in high impedance mode and is undriven.

8.5.1.5 Register Read/Write

Access to the internal registers can be done through the serial interface formed by pins CSB (Chip Select - active low), SCLK (serial interface clock), DIN (data input), and DOUT (data out).

Serial shift of bits into the device is enabled when CSB is low. Serial data DIN is latched (MSB received first, LSB received last) at every rising edge of SCLK when CSB is active (low). The serial data is loaded into the register with the last data bit SCLK rising edge when CSB is low. In the case that the word length exceeds the register size, the excess bits are ignored. The interface can work with SCLK frequency from 20MHz down to very low speeds (a few Hertz) and even with a non-50% duty-cycle SCLK.

The SPI transaction is divided in two main portions:

- Address and Control: Auto Increment Mode selection bit, Read/Write bit, Address 6 bits

- Data: 8 bit or 24 bit

When writing to a register with unused bits, these should be set to 0.

| Address and Control (A7 - A0) | |||||||

|---|---|---|---|---|---|---|---|

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| Auto Increment | RW | Register Address | |||||

| 0: OFF 1: ON |

Read = 0 Write = 1 |

00 h up to 3Fh | |||||

8.5.1.6 Auto Increment Mode

When the Auto Increment Mode is OFF, only the register indicated by the Register Address will be accessed, all cycles beyond the register length will be ignored. When the Auto Increment is ON, the register of the Register Address is accessed first, then without interruption, subsequent registers are accessed.

The Auto Increment Mode can be either used to access the configuration (CONFIG1 and CONFIG2) and status (INT_STATUS) registers, or for the Measurement Results registers (TIME1 to TIME6, CLOCK_COUNT1 to CLOCK_COUNT5, CALIBRATION1, CALIBRATION2). As both register block use registers with different length, it’s not possible to access all registers of the device within one single access cycle.

8.6 Register Maps

8.6.1 Register Initialization

After power up (VDD supplied, ENABLE Pin low to high transition) the internal registers are initialized with the default value. Disabling the part by pulling ENABLE pin to GND will set the device into total shutdown. As the internal LDO is turned off settings in the register will be lost. The device initializes the registers with default values with the next enable (ENABLE pin to VDD).

Table 1. Register Summary

| REGISTER ADDRESS | REGISTER NAME | REGISTER DESCRIPTION | SIZE (BITS) | RESET VALUE |

|---|---|---|---|---|

| 00h | CONFIG1 | Configuration Register 1 | 8 | 00h |

| 01h | CONFIG2 | Configuration Register 2 | 8 | 40h |

| 02h | INT_STATUS | Interrupt Status Register | 8 | 00h |

| 03h | INT_MASK | Interrupt Mask Register | 8 | 07h |

| 04h | COARSE_CNTR_OVF_H | Coarse Counter Overflow Value High | 8 | FFh |

| 05h | COARSE_CNTR_OVF_L | Coarse Counter Overflow Value Low | 8 | FFh |

| 06h | CLOCK_CNTR_OVF_H | CLOCK Counter Overflow Value High | 8 | FFh |

| 07h | CLOCK_CNTR_OVF_L | CLOCK Counter Overflow Value Low | 8 | FFh |

| 08h | CLOCK_CNTR_STOP_MASK_H | CLOCK Counter STOP Mask High | 8 | 00h |

| 09h | CLOCK_CNTR_STOP_MASK_L | CLOCK Counter STOP Mask Low | 8 | 00h |

| 10h | TIME1 | Measured Time 1 | 24 | 00_0000h |

| 11h | CLOCK_COUNT1 | CLOCK Counter Value | 24 | 00_0000h |

| 12h | TIME2 | Measured Time 2 | 24 | 00_0000h |

| 13h | CLOCK_COUNT2 | CLOCK Counter Value | 24 | 00_0000h |

| 14h | TIME3 | Measured Time 3 | 24 | 00_0000h |

| 15h | CLOCK_COUNT3 | CLOCK Counter Value | 24 | 00_0000h |

| 16h | TIME4 | Measured Time 4 | 24 | 00_0000h |

| 17h | CLOCK_COUNT4 | CLOCK Counter Value | 24 | 00_0000h |

| 18h | TIME5 | Measured Time 5 | 24 | 00_0000h |

| 19h | CLOCK_COUNT5 | CLOCK Counter Value | 24 | 00_0000h |

| 1Ah | TIME6 | Measured Time 6 | 24 | 00_0000h |

| 1Bh | CALIBRATION1 | Calibration 1, 1 CLOCK Period | 24 | 00_0000h |

| 1Ch | CALIBRATION2 | Calibration 2, 2/10/20/40 CLOCK Periods | 24 | 00_0000h |

8.6.2 CONFIG1: Configuration Register 1 R/W (address = 00h) [reset = 0h]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| FORCE_CAL | PARITY_EN | TRIGG_EDGE | STOP_EDGE | START_EDGE | MEAS_MODE | START_MEAS | |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 2. Configuration Register 1 Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | FORCE_CAL | R/W | 0 |

0: Calibration is not performed after interrupted measurement (for example, due to counter overflow or missing STOP signal) 1: Calibration is always performed at the end (for example, after a counter overflow) |

| 6 | PARITY_EN | R/W | 0 |

0: Parity bit for Measurement Result Registers* disabled (Parity Bit always 0) 1: Parity bit for Measurement Result Registers enabled (Even Parity) *The Measurement Results registers are the TIME1 to TIME6, CLOCK_COUNT1 to CLOCK_COUNT5, CALIBRATION1, CALIBRATION2 registers. |

| 5 | TRIGG_EDGE | R/W | 0 |

0: TRIGG is output as a Rising edge signal 1: TRIGG is output as a Falling edge signal |

| 4 | STOP_EDGE | R/W | 0 |

0: Measurement is stopped on Rising edge of STOP signal 1: Measurement is stopped on Falling edge of STOP signal |

| 3 | START_EDGE | R/W | 0 |

0: Measurement is started on Rising edge of START signal 1: Measurement is started on Falling edge of START signal |

| [2:1] | MEAS_MODE | R/W | 00h | 00: Measurement Mode 1 (for expected time-of-flight < 500 ns). 01: Measurement Mode 2 (recommended) 10, 11: Reserved for future functionality |

| 0 | START_MEAS | R/W | 0 |

Start New Measurement: 0: No effect 1: Start New Measurement. Writing a 1 will clear all bits in the Interrupt Status Register and Start the measurement (by generating an TRIGG signal) and will reset the content of all Measurement Results registers (TIME1 to TIME6, CLOCK_COUNT1 to CLOCK_COUNT5, CALIBRATION1, CALIBRATION2) to 0. |

8.6.3 CONFIG2: Configuration Register 2 R/W (address = 01h) [reset = 40h]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CALIBRATION2_PERIODS | AVG_CYCLES | NUM_STOP | |||||

| R/W-0h | R/W-1h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 3. Configuration Register 2 Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| [7:6] | CALIBRATION2_PERIODS | R/W | 01h |

00: Calibration 2 - measuring 2 CLOCK periods 01: Calibration 2 - measuring 10 CLOCK periods 10: Calibration 2 - measuring 20 CLOCK periods 11: Calibration 2 - measuring 40 CLOCK periods |

| [5:3] | AVG_CYCLES | R/W | 00h |

000: 1 Measurement Cycle only (no Multi-Cycle Averaging Mode) 001: 2 Measurement Cycles 010: 4 Measurement Cycles 011: 8 Measurement Cycles 100: 16 Measurement Cycles 101: 32 Measurement Cycles 110: 64 Measurement Cycles 111: 128 Measurement Cycles |

| [2:0] | NUM_STOP | R/W | 00h |

000: Single Stop 001: Two Stops 010: Three Stops 011: Four Stops 100: Five Stops 101, 110, 111: No Effect. Single Stop |

8.6.4 INT_STATUS: Interrupt Status Register (address = 02h) [reset = 00h]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Reserved | Reserved | Reserved | MEAS_COMPLETE_FLAG | MEAS_STARTED_FLAG | CLOCK_CNTR_ OVF_INT |

COARSE_CNTR_ OVF_INT |

NEW_MEAS_ INT |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 4. Interrupt Status Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | Reserved | R/W | 0h |

|

| 6 | Reserved | R/W | 0h |

|

| 5 | Reserved | R/W | 0h |

|

| 4 | MEAS_COMPLETE_FLAG | R/W | 0h |

Writing a 1 will clear the status 0: Measurement has not completed 1: Measurement has completed (same information as NEW_MEAS_INT) |

| 3 | MEAS_STARTED_FLAG | R/W | 0h |

Writing a 1 will clear the status 0: Measurement has not started 1: Measurement has started (START signal received) |

| 2 | CLOCK_CNTR_OVF_INT | R/W | 0h |

Requires writing a 1 to clear interrupt status 0: No overflow detected 1: Clock overflow detected, running measurement will be stopped immediately |

| 1 | COARSE_CNTR_OVF_INT | R/W | 0h |

Requires writing a 1 to clear interrupt status 0: No overflow detected 1: Coarse overflow detected, running measurement will be stopped immediately |

| 0 | NEW_MEAS_INT | R/W | 0h |

Requires writing a 1 to clear interrupt status 0: Interrupt not detected 1: Interrupt detected – New Measurement has been completed |

8.6.5 INT_MASK: Interrupt Mask Register R/W (address = 03h) [reset = 07h]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Reserve | Reserve | Reserve | Reserve | Reserve | CLOCK_CNTR _OVF_MASK |

COARSE_CNTR _OVF_MASK |

NEW_MEAS _MASK |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-1h | R/W-1h | R/W-1h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 5. Interrupt Mask Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | Reserve | R/W | 0 | |

| 6 | Reserve | R/W | 0 | |

| 5 | Reserve | R/W | 0 | |

| 4 | Reserve | R/W | 0 | |

| 3 | Reserve | R/W | 0 | |

| 2 | CLOCK_CNTR_OVF_MASK | R/W | 1 |

0: CLOCK Counter Overflow Interrupt disabled 1: CLOCK Counter Overflow Interrupt enabled |

| 1 | COARSE_CNTR_OVF_MASK | R/W | 1 |

0: Coarse Counter Overflow Interrupt disabled 1: Coarse Counter Overflow Interrupt enabled |

| 0 | NEW_MEAS_MASK | R/W | 1 |

0: New Measurement Interrupt disabled 1: New Measurement Interrupt enabled |

A disabled interrupt will no longer be visible on the device pin (INTB). The interrupt bit in the INT_STATUS register will still be active.

8.6.6 COARSE_CNTR_OVF_H: Coarse Counter Overflow High Value Register (address = 04h) [reset = FFh]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| COARSE_CNTR_OVF_H | |||||||

| R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 6. Coarse Counter Overflow Value_H Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7-0 | COARSE_CNTR_OVF_H | R/W | FFh | Coarse Counter Overflow Value, upper 8 Bit |

8.6.7 COARSE_CNTR_OVF_L: Coarse Counter Overflow Low Value Register (address = 05h) [reset = FFh ]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| COARSE_CNTR_OVF_L | |||||||

| R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 7. Coarse Counter Overflow Value_L Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7-0 | COARSE_CNTR_OVF_L | R/W | FFh |

Coarse Counter Overflow Value, lower 8 Bit Note: Don't set COARSE_CNTR_OVF_L to 1. |

8.6.8 CLOCK_CNTR_OVF_H: Clock Counter Overflow High Register (address = 06h) [reset = FFh]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CLOCK_CNTR_OVF_H | |||||||

| R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 8. CLOCK Counter Overflow Value_H Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7-0 | CLOCK_CNTR_OVF_H | R/W | FFh | CLOCK Counter Overflow Value, upper 8 Bit |

8.6.9 CLOCK_CNTR_OVF_L: Clock Counter Overflow Low Register (address = 07h) [reset = FFh]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CLOCK_CNTR_OVF_L | |||||||

| R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h | R/W-1h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 9. CLOCK Counter Overflow Value_L Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7-0 | CLOCK_CNTR_OVF_L | R/W | FFh | CLOCK Counter Overflow Value, lower 8 Bit |

8.6.10 CLOCK_CNTR_STOP_MASK_H: CLOCK Counter STOP Mask High Value Register (address = 08h) [reset = 00h]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CLOCK_CNTR_STOP_MASK_H | |||||||

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 10. CLOCK Counter STOP Mask_H Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7-0 | CLOCK_CNTR_STOP_MASK_H | R/W | 0 | CLOCK Counter STOP Mask, upper 8 Bit |

8.6.11 CLOCK_CNTR_STOP_MASK_L: CLOCK Counter STOP Mask Low Value Register (address = 09h) [reset = 00h]

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CLOCK_CNTR_STOP_MASK_L | |||||||

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 11. CLOCK Counter STOP Mask_L Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7-0 | CLOCK_CNTR_STOP_MASK_L | R/W | 0 | CLOCK Counter STOP Mask, lower 8 Bit |

8.6.12 TIME1: Time 1 Register (address: 10h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | Measurement Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 12. TIME1 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity Bit | R | 0 | Parity Bit |

| 22-0 | Measurement Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) | R | 0 | Measurement Result |

8.6.13 CLOCK_COUNT1: Clock Count Register (address: 11h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | CLOCK_COUNT1 Result | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 13. CLOCK_COUNT1 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity Bit | R | 0 | Parity Bit |

| 22-16 | Not Used | R | 0 | These bits will be used in Multi-Cycle Averaging Mode in order to allow higher averaging results. |

| 15-0 | CLOCK_COUNT1 Measurement Result | R | 0 | CLOCK_COUNT1 Measurement Result |

8.6.14 TIME2: Time 2 Register (address: 12h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | Measurement Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 14. TIME2 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity Bit | R | 0 | Parity Bit |

| 22-0 | Measurement Result | R | 0 | Measurement Result |

8.6.15 CLOCK_COUNT2: Clock Count Register (address: 13h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | CLOCK_COUNT2 | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 15. CLOCK_COUNT2 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | Parity Bit |

| 22-16 | Not Used | R | 0 | These bits will be used in Multi-Cycle Averaging Mode in order to allow higher averaging results. |

| 15-0 | CLOCK_COUNT2 result | R | 0 | CLOCK_COUNT2 result |

8.6.16 TIME3: Time 3 Register (address: 14h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | Measurement Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 16. TIME3 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | Parity Bit |

| 22-0 | Measurement result | R | 0 | Measurement Result |

8.6.17 CLOCK_COUNT3: Clock Count Registers (address: 15h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | CLOCK_COUNT3 | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 17. CLOCK_COUNT3 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | Parity bit |

| 22-16 | Not Used | R | 0 | These bits will be used in Multi-Cycle Averaging Mode in order to allow higher averaging results. |

| 15-0 | CLOCK_COUNT3 Result | R | 0 | CLOCK_COUNT3 Result |

8.6.18 TIME4: Time 4 Register (address: 16h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | Measurement Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 18. TIME4 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | |

| 22-0 | Measurement result | R | 0 | Measurement result |

8.6.19 CLOCK_COUNT4: Clock Count Register (address: 17h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | CLOCK_COUNT4 | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 19. CLOCK_COUNT4 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | Parity bit |

| 22-16 | Not Used | R | 0 | These bits will be used in Multi-Cycle Averaging Mode in order to allow higher averaging results. |

| 15-0 | CLOCK_COUNT4 Result | R | 0 | CLOCK_COUNT4 Result |

8.6.20 TIME5: Time 5 Register (address: 18h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | Measurement Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 20. TIME5 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | Parity Bit |

| 22-0 | Measurement result | R | 0 | Measurement result |

8.6.21 CLOCK_COUNT5: Clock Count Register (address: 19h) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | CLOCK_COUNT5 | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 21. CLOCK_COUNT5 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | Parity bit |

| 22-16 | Not Used | R | 0 | These bits will be used in Multi-Cycle Averaging Mode in order to allow higher averaging results. |

| 15-0 | CLOCK_COUNT5 Result | R | 0 | CLOCK_COUNT5 Result |

8.6.22 TIME6: Time 6 Register (address: 1Ah) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | Measurement Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 22. TIME6 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity bit | R | 0 | Parity Bit |

| 22-0 | Measurement result | R | 0 | Measurement result |

8.6.23 CALIBRATION1: Calibration 1 Register (address: 1Bh ) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | CALIBRATION1 | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 23. CALIBRATION1 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity BIt | R | 0 | Parity Bit |

| 22-0 | CALIBRATION1 | R | 0 | Calibration 1 Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) |

8.6.24 CALIBRATION2: Calibration 2 Register (address: 1Ch ) [reset = 00_0000h]

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Parity Bit | CALIBRATION2 | ||||||||||||||||||||||

| R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 24. CALIBRATION2 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 23 | Parity BIt | R | 0 | Parity Bit |

| 22-0 | CALIBRATION2 | R | 0 | Calibration 2 Result: 23 bit integer value (Bit 22: MSB, Bit 0: LSB) |