SNLS745A November 2023 – April 2024 TDP2004

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- RNQ|40

Thermal pad, mechanical data (Package|Pins)

Orderable Information

5.9 Typical Jitter Characteristics

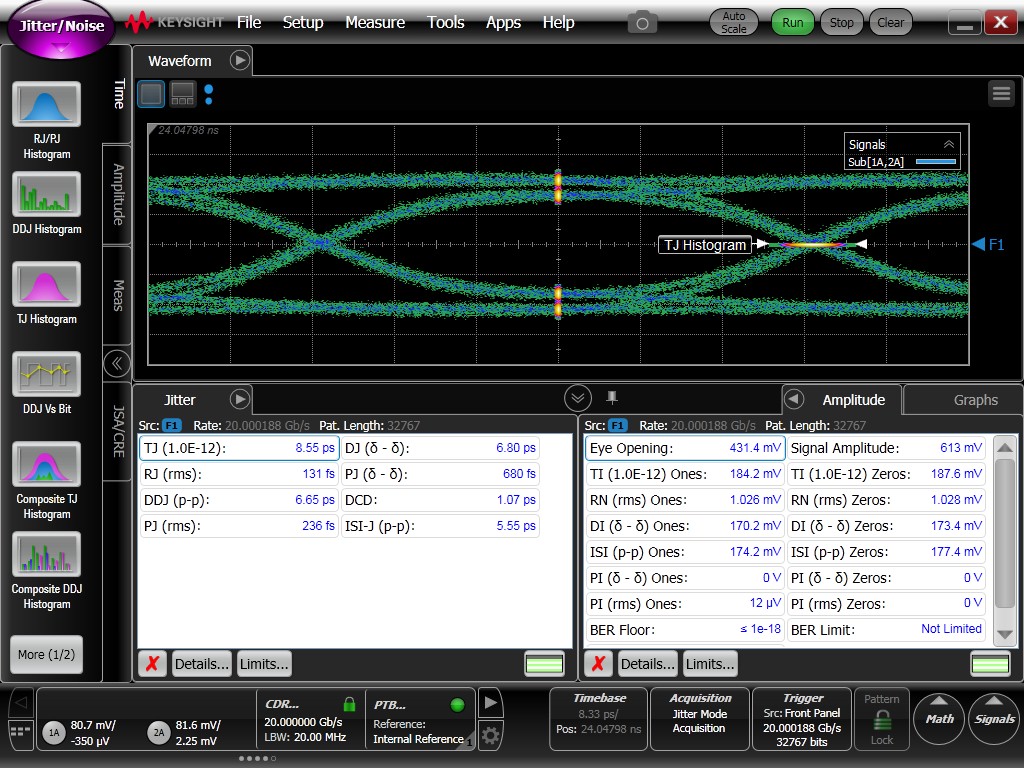

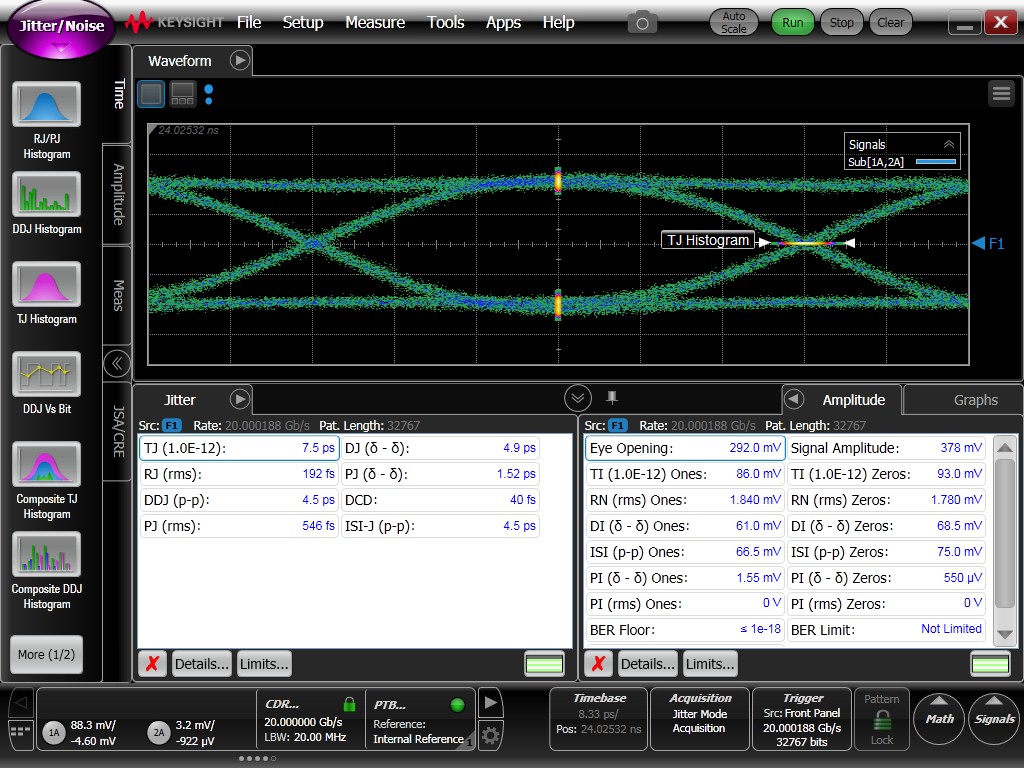

Figure 5-3 and Figure 5-4 show eye diagrams at 20Gbps that compare jitter through calibration traces (left), and jitter through TDP2004 (right) at TI evaluation boards with minimal channels. The eye diagrams illustrate that TDP2004 adds very little random jitter (RJ).

Figure 5-3 Through

Baseline Calibration Trace Setup for 20Gbps

Figure 5-3 Through

Baseline Calibration Trace Setup for 20Gbps  Figure 5-4 Through TDP2004 for 20Gbps

Figure 5-4 Through TDP2004 for 20Gbps