SBOS778D April 2016 – April 2021 THS4551

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Companion Devices

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: (VS+) – (VS–) = 5 V

- 7.6 Electrical Characteristics: (VS+) – (VS–) = 3 V

- 7.7 Typical Characteristics: (VS+) – (VS–) = 5 V

- 7.8 Typical Characteristics: (VS+) – (VS–) = 3 V

- 7.9 Typical Characteristics: 3-V to 5-V Supply Range

-

8 Parameter Measurement Information

- 8.1 Example Characterization Circuits

- 8.2 Output Interface Circuit for DC-Coupled Differential Testing

- 8.3 Output Common-Mode Measurements

- 8.4 Differential Amplifier Noise Measurements

- 8.5 Balanced Split-Supply Versus Single-Supply Characterization

- 8.6 Simulated Characterization Curves

- 8.7 Terminology and Application Assumptions

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

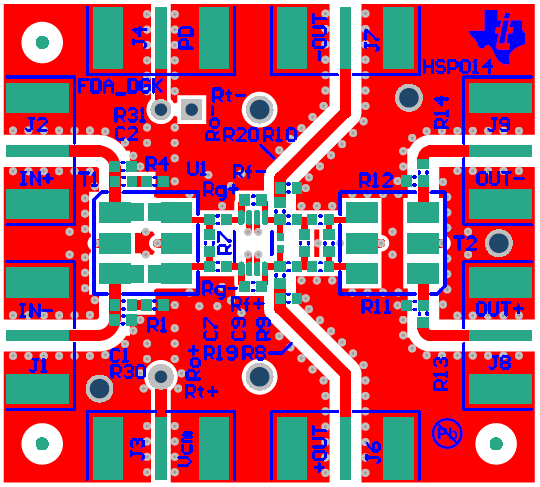

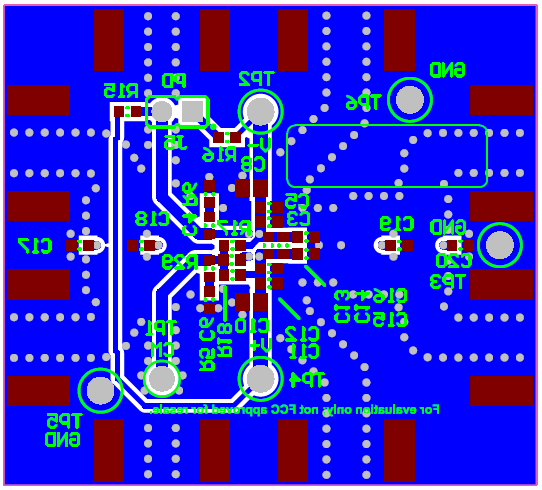

12.3 EVM Board

Figure 12-2 and Figure 12-3 show the layout of the top and bottom layers of the THS4551DGKEVM evaluation module, respectively.

Figure 12-2 THS4551DGKEVM Top Layer

Figure 12-2 THS4551DGKEVM Top Layer Figure 12-3 THS4551DGKEVM Bottom Layer

Figure 12-3 THS4551DGKEVM Bottom Layer