SLFS078C October 2006 – April 2024 TLC555-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

3 Description

The TLC555-Q1 is a monolithic timing circuit fabricated using TI LinCMOS™ technology. The timer is fully compatible with CMOS, TTL, and MOS logic and operates at frequencies up to 2MHz. As a result of the high input impedance, this device supports smaller timing capacitors than capacitors used by the NE555. Thus, more accurate time delays and oscillations are possible. Power consumption is low across the full power-supply voltage range.

Like the NE555, the TLC555-Q1 has a trigger level equal to approximately one-third of the supply voltage, and a threshold level equal to approximately two-thirds of the supply voltage. These levels can be altered by using the control voltage pin (CONT). When the trigger input (TRIG) falls below the trigger level, the flip-flop is set, and the output goes high. If TRIG is greater than the trigger level and the threshold input (THRES) is greater than the threshold level, the flip-flop is reset and the output goes low. The reset input (RESET) can override all other inputs and is used to initiate a new timing cycle. If RESET is low, the flip-flop is reset and the output goes low. Whenever the output is low, a low-impedance path is provided between the discharge pin (DISCH) and GND. Tie all unused inputs to an appropriate logic level to prevent false triggering.

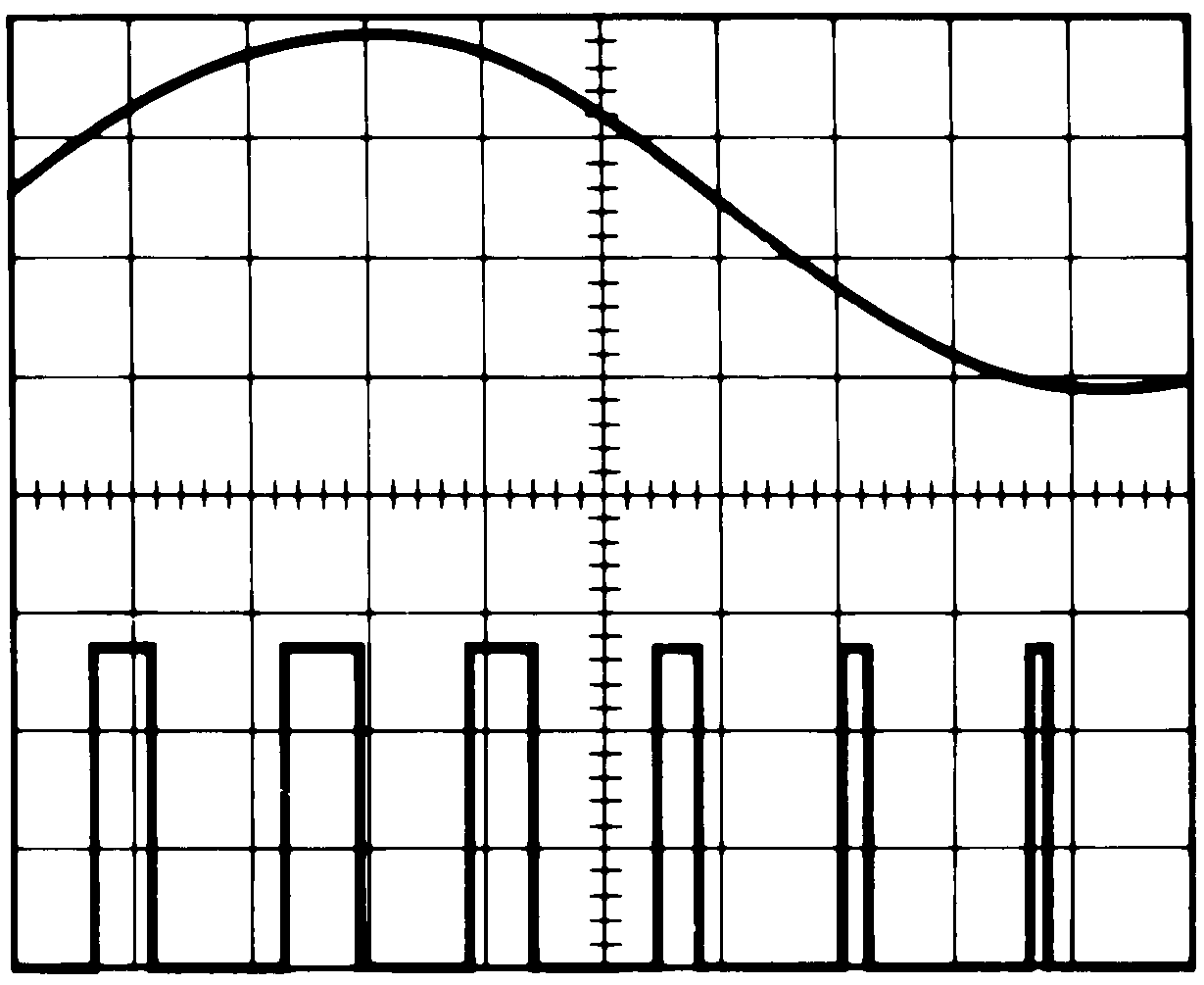

Pulse Width Modulator

Pulse Width Modulator Pulse Width Modulator

Waveform:

Pulse Width Modulator

Waveform: Top Waveform - Modulation

Bottom Waveform - Output Voltage