SLLSF62B December 2020 – April 2022 TLIN1021A-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specification

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 10Application Information Disclaimer

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- DRB|8

Orderable Information

10.2.3 Application Curves

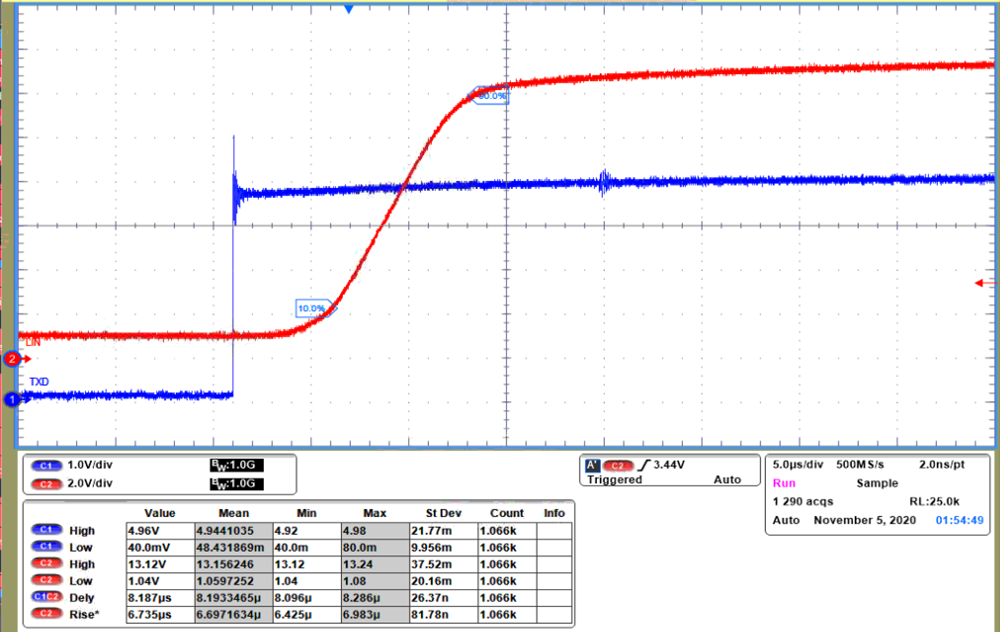

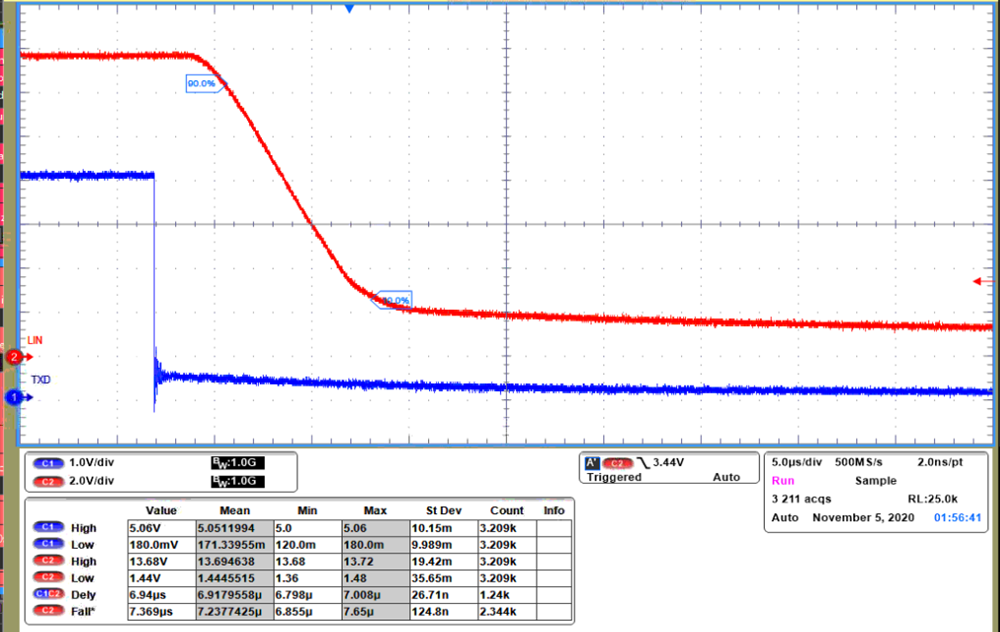

Figure 10-2 and Figure 10-3 show the propagation delay from the TXD pin to the LIN pin for the dominant to recessive and recessive to dominant edges. Device was configured in commander mode with external pull-up resistor (1 kΩ) and 680 pF bus capacitance.

Figure 10-2 Dominant To Recessive Propagation Delay

Figure 10-2 Dominant To Recessive Propagation Delay Figure 10-3 Recessive to Dominant Propagation Delay

Figure 10-3 Recessive to Dominant Propagation Delay