SLLSEL3C July 2015 – September 2017 TLK10031

PRODUCTION DATA.

- 1 Device Overview

- 2 Revision History

- 3 Description

- 4 Terminal Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Electrical Characteristics: High Speed Side Serial Transmitter

- 5.6 Electrical Characteristics: High Speed Side Serial Receiver

- 5.7 Electrical Characteristics: Low Speed Side Serial Transmitter

- 5.8 Electrical Characteristics: Low Speed Side Serial Receiver

- 5.9 Electrical Characteristics: LVCMOS (VDDO):

- 5.10 Electrical Characteristics: Clocks

- 5.11 Timing Requirements

- 5.12 Typical Characteristics

- 6 Parametric Measurement Information

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagrams

- 7.3

Feature Description

- 7.3.1 10GBASE-KR Transmit Data Path Overview

- 7.3.2 10GBASE-KR Receive Data Path Overview

- 7.3.3 Channel Synchronization Block

- 7.3.4 8B/10B Encoder

- 7.3.5 8B/10B Decoder

- 7.3.6 64B/66B Encoder/Scrambler

- 7.3.7 Forward Error Correction

- 7.3.8 64B/66B Decoder/Descrambler

- 7.3.9 Transmit Gearbox

- 7.3.10 Receive Gearbox

- 7.3.11 XAUI Lane Alignment / Code Gen (XAUI PCS)

- 7.3.12 Inter-Packet Gap (IPG) Characters

- 7.3.13 Clock Tolerance Compensation (CTC)

- 7.3.14 10GBASE-KR Auto-Negotiation

- 7.3.15 10GBASE-KR Link Training

- 7.3.16 10GBASE-KR Line Rate, PLL Settings, and Reference Clock Selection

- 7.3.17 10GBASE-KR Test Pattern Support

- 7.3.18 10GBASE-KR Latency

- 7.4

Device Functional Modes

- 7.4.1 10GBASE-KR Mode

- 7.4.2 1GBASE-KX Mode

- 7.4.3 General Purpose (10G) Serdes Mode Functional Description

- 7.4.4 General Purpose SERDES Receive Data Path

- 7.4.5 Channel Synchronization

- 7.4.6 8B/10B Encoder and Decoder

- 7.4.7 Lane Alignment Scheme for 8b/10b General Purpose Serdes Mode

- 7.4.8 Lane Alignment Components

- 7.4.9 Lane Alignment Operation

- 7.4.10 Line Rate, SERDES PLL Settings, and Reference Clock Selection for the General Purpose SERDES Mode

- 7.4.11 General Purpose SERDES Mode Test Pattern Support

- 7.4.12 General Purpose SERDES Mode Latency

- 7.4.13 Intelligent Switching Modes

- 7.4.14 Serial Loopback Modes

- 7.4.15 Latency Measurement Function (General Purpose SerDes Mode)

- 7.4.16 Power Down Mode

- 7.4.17 MDIO Management Interface

- 7.4.18 MDIO Protocol Timing

- 7.4.19 Clause 22 Indirect Addressing

- 7.4.20 Provisionable XAUI Clock Tolerance Compensation

- 7.5

Register Maps

- 7.5.1 Register Bit Definitions

- 7.5.2

Vendor Specific Device Registers

- 7.5.2.1 GLOBAL_CONTROL_1 (register: 0x0000) (default: 0x0610) (device address: 0x1E)

- 7.5.2.2 CHANNEL_CONTROL_1 (register: 0x0001) (default: 0x0B00) (device address: 0x1E)

- 7.5.2.3 HS_SERDES_CONTROL_1 (register: 0x0002 ) (default: 0x831D) (device address: 0x1E)

- 7.5.2.4 HS_SERDES_CONTROL_2 (register: 0x0003) (default: 0xA848) (device address: 0x1E)

- 7.5.2.5 HS_SERDES_CONTROL_3 (register: 0x0004) (default: 0x1500) (device address: 0x1E)

- 7.5.2.6 HS_SERDES_CONTROL_4 (register: 0x0005) (default: 0x2000) (device address: 0x1E)

- 7.5.2.7 LS_SERDES_CONTROL_1 (register: 0x0006) (default: 0xF115) (device address: 0x1E)

- 7.5.2.8 LS_SERDES_CONTROL_2 (register: 0x0007) (default: 0xDC04) (device address: 0x1E)

- 7.5.2.9 LS_SERDES_CONTROL_3 (register: 0x0008) (default: 0x000D) (device address: 0x1E)

- 7.5.2.10 HS_OVERLAY_CONTROL (register: 0x0009) (default: 0x0380) (device address: 0x1E)

- 7.5.2.11 LS_OVERLAY_CONTROL (register: 0x000A) (default: 0x4000) (device address: 0x1E)

- 7.5.2.12 LOOPBACK_TP_CONTROL (register: 0x000B) (default: 0x0D10) (device address: 0x1E)

- 7.5.2.13 LS_CONFIG_CONTROL (register: 0x000C) (default: 0x0330) (device address: 0x1E)

- 7.5.2.14 LS_CONFIG_CONTROL (register: 0x000C) (default: 0x0330) (device address: 0x1E)

- 7.5.2.15 CLK_CONTROL (register: 0x000D) (default: 0x2F80) (device address: 0x1E)

- 7.5.2.16 RESET_CONTROL (register: 0x000E) (default: 0x0000) (device address: 0x1E)

- 7.5.2.17 CHANNEL_STATUS_1 (register: 0x000F) (default: 0x0000) (device address: 0x1E)

- 7.5.2.18 HS_ERROR_COUNTER (register: 0x0010) (default: 0x0FFFD) (device address: 0x1E)

- 7.5.2.19 LS_LN0_ERROR_COUNTER (register: 0x0011) (default: 0xFFFD) (device address: 0x1E)

- 7.5.2.20 LS_LN1_ERROR_COUNTER (register: 0x0012 ) (default: 0xFFFD) (device address: 0x1E)

- 7.5.2.21 LS_LN2_ERROR_COUNTER (register: 0x0013) (default: 0xFFFD) (device address: 0x1E)

- 7.5.2.22 LS_LN3_ERROR_COUNTER (register: 0x0014) (default: 0xFFFD) (device address: 0x1E)

- 7.5.2.23 LS_STATUS_1 (register: 0x0015) (default: 0x0000) (device address: 0x1E)

- 7.5.2.24 HS_STATUS_1 (register: 0x0016) (default: 0x0000) (device address: 0x1E)

- 7.5.2.25 DST_CONTROL_1 (register = 0x0017) (default = 0x2000) (device address: 0x1E)

- 7.5.2.26 DST_CONTROL_2 (register = 0x0018 ) (default = 0x0C20) (device address: 0x1E)

- 7.5.2.27 DSR_CONTROL_1 (register = 0x0019) (default = 0x2500) (device address: 0x1E)

- 7.5.2.28 DSR_CONTROL_2 (register = 0x001A) (default = 0x4C20) (device address: 0x1E)

- 7.5.2.29 DATA_SWITCH_STATUS (register = 0x001B) (default = 0x1020) (device address: 0x1E)

- 7.5.2.30 LS_CH_CONTROL_1 (register =0x001C) (default =0x0000) (device address: 0x1E)

- 7.5.2.31 HS_CH_CONTROL_1 (register = 0x001D) (default = 0x0000) (device address: 0x1E)

- 7.5.2.32 EXT_ADDRESS_CONTROL (register = 0x001E) (default = 0x0000) (device address: 0x1E)

- 7.5.2.33 EXT_ADDRESS_DATA (register = 0x001F) (default = 0x0000) (device address: 0x1E)

- 7.5.2.34 VS_10G_LN_ALIGN_ACODE_P (register =0x8003) (default = 0x0283) (device address: 0x1E)

- 7.5.2.35 VS_10G_LN_ALIGN_ACODE_N (register =0x8004 ) (default = 0x017C) (device address: 0x1E)

- 7.5.2.36 MC_AUTO_CONTROL (register = 0x8021) (default = 0x000F) (device address: 0x1E)

- 7.5.2.37 DST_ON_CHAR_CONTROL (register = 0x802A) (default = 0x02FD) (device address: 0x1E)

- 7.5.2.38 DST_OFF_CHAR_CONTROL (register = 0x802B ) (default = 0x02FD) (device address: 0x1E)

- 7.5.2.39 DST_STUFF_CHAR_CONTROL (register = 0x802C) (default = 0x0207) (device address: 0x1E)

- 7.5.2.40 DSR_ON_CHAR_CONTROL (register = 0x802D) (default = 0x02FD) (device address: 0x1E)

- 7.5.2.41 DSR_OFF_CHAR_CONTROL (register = 0X802E) (default = 0x02FD) (device address: 0x1E)

- 7.5.2.42 DSR_STUFF_CHAR_CONTROL (register = 0x802F) (default = 0x0207) (device address: 0x1E)

- 7.5.2.43 LATENCY_MEASURE_CONTROL (register = 0x8040) (default = 0x0000) (device address: 0x1E)

- 7.5.2.44 LATENCY_COUNTER_2 (register = 0x8041) (default =0x0000) (device address: 0x1E)

- 7.5.2.45 LATENCY_COUNTER_1 (register = 0x8042) (default = 0x0000) (device address: 0x1E)

- 7.5.2.46 TRIGGER_LOAD_CONTROL (register =0x8100) (default = 0x0000) (device address: 0x1E)

- 7.5.2.47 TRIGGER_EN_CONTROL (register = 0x8101) (default = 0x0000) (device address: 0x1E)

- 7.5.3

PMA/PMD Registers

- 7.5.3.1 PMA_CONTROL_1 (register = 0x0000) (default = 0x0000) (device address: 0x01)

- 7.5.3.2 PMA_STATUS_1 (register = 0x0001) (default = 0x0002) (device address: 0x01)

- 7.5.3.3 PMA_DEV_IDENTIFIER_1 (register = 0x0002) (default = 0x4000) (device address: 0x01)

- 7.5.3.4 PMA_DEV_IDENTIFIER_2 (register = 0x0003) (default = 0x5100) (device address: 0x01)

- 7.5.3.5 PMA_SPEED_ABILITY (register = 0x0004) (default = 0x0011) (device address: 0x01)

- 7.5.3.6 PMA_DEV_PACKAGE_1 (register = 0x0005) (default = 0x000B) (device address: 0x01)

- 7.5.3.7 PMA_DEV_PACKAGE_2 (register = 0x0006) (default = 0x4000) (device address: 0x01)

- 7.5.3.8 PMA_DEV_PACKAGE_2 (register = 0x0006) (default = 0x4000) (device address: 0x01)

- 7.5.3.9 PMA_RX_SIGNAL_DET_STATUS (register = 0x000A) (default = 0x0000) (device address: 0x01)

- 7.5.3.10 PMA_EXTENDED_ABILITY (register = 0x000B) (default = 0x0050) (device address: 0x01)

- 7.5.3.11 LT_TRAIN_CONTROL (register =0x0096) (default = 0x0002) (device address: 0x01)

- 7.5.3.12 LT_TRAIN_STATUS (register = 0x0097) (default = 0x0000) (device address: 0x01)

- 7.5.3.13 LT_LINK_PARTNER_CONTROL (register = 0x0098) (default = 0x0000) (device address: 0x01)

- 7.5.3.14 LT_LINK_PARTNER_STATUS (register = 0x0099) (default = 0x0000) (device address: 0x01)

- 7.5.3.15 LT_LOCAL_DEVICE_CONTROL (register = 0x009A) (default = 0x0000) (device address: 0x01)

- 7.5.3.16 LT_LOCAL_DEVICE_STATUS (register = 0x009B) (default = 0x0000) (device address: 0x01)

- 7.5.3.17 KX_STATUS (register = 0x00A1) (default = 0x3000) (device address: 0x01)

- 7.5.3.18 KR_FEC_ABILITY (register = 0x00AA) (default = 0x0003) (device address: 0x01)

- 7.5.3.19 KR_FEC_CONTROL (register = 0x00AB) (default = 0x0000) (device address: 0x01)

- 7.5.3.20 KR_FEC_C_COUNT_1 (register = 0x00AC) (default = 0x0000) (device address: 0x01)

- 7.5.3.21 KR_FEC_C_COUNT_2 (register = 0x00AD) (default = 0x0000) (device address: 0x01)

- 7.5.3.22 KR_FEC_UC_COUNT_1 (register = 0x00AE) (default = 0x0000) (device address: 0x01)

- 7.5.3.23 KR_FEC_UC_COUNT_2 (register = 0x00AF) (default = 0x0000) (device address: 0x01)

- 7.5.3.24 KR_VS_FIFO_CONTROL_1 (register = 0x8001) (default = 0xCC4C) (device address: 0x01)

- 7.5.3.25 KR_VS_TP_GEN_CONTROL (register =0x8002) (default = 0x0000) (device address: 0x01)

- 7.5.3.26 KR_VS_TP_VER_CONTROL (register = 0x8003) (default = 0x0000) (device address: 0x01)

- 7.5.3.27 KR_VS_CTC_ERR_CODE_LN0 (register = 0x8005) (default = 0xCE00) (device address: 0x01)

- 7.5.3.28 KR_VS_CTC_ERR_CODE_LN1 (register = 0x8006) (default =0x0000) (device address: 0x01)

- 7.5.3.29 KR_VS_CTC_ERR_CODE_LN2 (register = 0x8007) (default = 0x0000) (device address: 0x01)

- 7.5.3.30 KR_VS_CTC_ERR_CODE_LN3 (register = 0x8008) (default = 0x0080) (device address: 0x01)

- 7.5.3.31 KR_VS_LN0_EOP_ERROR_COUNTER (register = 0x8010) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.32 KR_VS_LN1_EOP_ERROR_COUNTER (register = 0x8011) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.33 KR_VS_LN2_EOP_ERROR_COUNTER (register = 0x8012) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.34 KR_VS_LN3_EOP_ERROR_COUNTER (register =0x8013 ) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.35 KR_VS_TX_CTC_DROP_COUNT (register = 0x8014) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.36 KR_VS_TX_CTC_INSERT_COUNT (register = 0x8015) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.37 KR_VS_RX_CTC_DROP_COUNT (register = 0x8016) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.38 KR_VS_RX_CTC_INSERT_COUNT (register = 0x8017) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.39 KR_VS_STATUS_1 (register = 0x8018) (default = 0x0000) (device address: 0x01)

- 7.5.3.40 KR_VS_TX_CRCJ_ERR_COUNT_1 (register = 0x8019) (default = 0xFFFF) (device address: 0x01)

- 7.5.3.41 KR_VS_TX_CRCJ_ERR_COUNT_2 (register = 0x801A) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.42 KR_VS_TX_LN0_HLM_ERR_COUNT (register = 0x801B) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.43 KR_VS_TX_LN1_HLM_ERR_COUNT (register = 0x801C) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.44 KR_VS_TX_LN2_HLM_ERR_COUNT (register = 0x801D) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.45 KR_VS_TX_LN3_HLM_ERR_COUNT (register = 0x801E) (default = 0xFFFD) (device address: 0x01)

- 7.5.3.46 LT_VS_CONTROL_2 (register = 0x9001) (default = 0x0000) (device address: 0x01)

- 7.5.4

PCS Registers

- 7.5.4.1 PCS_CONTROL (register = 0x0000) (default = 0x0000) (device address: 0x03)

- 7.5.4.2 PCS_STATUS_1 (register = 0x0001) (default = 0x0002) (device address: 0x03)

- 7.5.4.3 PCS_STATUS_2 (register = 0x0008) (default = 0x8001) (device address: 0x03)

- 7.5.4.4 KR_PCS_STATUS_1 (register = 0x0020) (default = 0x0004) (device address: 0x03)

- 7.5.4.5 KR_PCS_STATUS_2 (register = 0x0021) (default = 0x0000) (device address: 0x03)

- 7.5.4.6 PCS_TP_SEED_A0 (register = 0x0022) (default = 0x0000) (device address: 0x03)

- 7.5.4.7 PCS_TP_SEED_A1 (register = 0x0023) (default = 0x0000) (device address: 0x03)

- 7.5.4.8 PCS_TP_SEED_A2 (register = 0x0024) (default = 0x0000) (device address: 0x03)

- 7.5.4.9 PCS_TP_SEED_A3 (register = 0x0025) (default = 0x0000) (device address: 0x03)

- 7.5.4.10 PCS_TP_SEED_B0 (register = 0x0026) (default = 0x0000) (device address: 0x03)

- 7.5.4.11 PCS_TP_SEED_B1 (register = 0x0027) (default = 0x0000) (device address: 0x03)

- 7.5.4.12 PCS_TP_SEED_B2 (register = 0x0028) (default = 0x0000) (device address: 0x03)

- 7.5.4.13 PCS_TP_SEED_B3 (register = 0x0029) (default = 0x0000) (device address: 0x03)

- 7.5.4.14 PCS_TP_CONTROL (register = 0x002A) (default = 0x0000) (device address: 0x03)

- 7.5.4.15 PCS_TP_ERR_COUNT (register = 0x002B) (default = 0x0000) (device address: 0x03)

- 7.5.4.16 PCS_VS_CONTROL (register = 0x8000) (default = 0x00B0) (device address: 0x03)

- 7.5.4.17 PCS_VS_STATUS (register = 0x8010) (default = 0x00FD) (device address: 0x03)

- 7.5.5

Auto-Negotiation Registers

- 7.5.5.1 AN_CONTROL (register = 0x0000) (default = 0x3000) (device address: 0x07)

- 7.5.5.2 AN_STATUS (register = 0x0001) (default = 0x0088) (device address: 0x07)

- 7.5.5.3 AN_DEV_PACKAGE (register = 0x0005) (default = 0x0080) (device address: 0x07)

- 7.5.5.4 AN_ADVERTISEMENT_1 (register = 0x0010) (default = 0x1001) (device address: 0x07)

- 7.5.5.5 AN_ADVERTISEMENT_2 (register = 0x0011) (default = 0x0080) (device address: 0x07)

- 7.5.5.6 AN_ADVERTISEMENT_3 (register = 0x0012) (default = 0x4000) (device address: 0x07)

- 7.5.5.7 AN_LP_ADVERTISEMENT_1 (register = 0x0013) (default = 0x0001) (device address: 0x07)

- 7.5.5.8 AN_LP_ADVERTISEMENT_2 (register = 0x0014) (default = 0x0000) (device address: 0x07)

- 7.5.5.9 AN_LP_ADVERTISEMENT_3 (register = 0x0015) (default = 0x0000) (device address: 0x07)

- 7.5.5.10 AN_XNP_TRANSMIT_1 (register = 0x0016) (default = 0x2000) (device address: 0x07)

- 7.5.5.11 AN_XNP_TRANSMIT_2 (register = 0x0017) (default = 0x0000) (device address: 0x07)

- 7.5.5.12 AN_XNP_TRANSMIT_3 (register = 0x0018) (default = 0x0000) (device address: 0x07)

- 7.5.5.13 AN_LP_XNP_ABILITY_1 (register = 0x0019) (default = 0x0000) (device address: 0x07)

- 7.5.5.14 AN_LP_XNP_ABILITY_2 (register = 0x001A) (default = 0x0000) (device address: 0x07)

- 7.5.5.15 AN_LP_XNP_ABILITY_3 (register = 0x001B) (default = 0x0000) (device address: 0x07)

- 7.5.5.16 AN_BP_STATUS (register = 0x0030) (default = 0x0001) (device address: 0x07)

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical Packaging and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- CTR|144

Thermal pad, mechanical data (Package|Pins)

Orderable Information

5 Specifications

5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)| VALUE | UNIT | |||

|---|---|---|---|---|

| MIN | MAX | |||

| Supply voltage | DVDD, VDD_LS/HS, VDDT_LS/HS, VPP, VDDD | –0.3 | 1.4 | V |

| VDDR_LS/HS, VDDO[1:0] | –0.3 | 2.2 | V | |

| Input Voltage, VI | LVCMOS, CML, Analog | –0.3 | Supply + 0.3 | V |

| Operating Junction Temperature | 105 | °C | ||

| Characterized free-air operating temperature range | –40 | 85 | °C | |

| Storage temperature, Tstg | -65 | 150 | °C | |

(1) Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to ground (VSS).

5.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS001(1) | ±1000 | V | |

| Charged Device Model (CDM), per JESD22-C101(2) |

±500 | V | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

5.3 Recommended Operating Conditions

5.4 Thermal Information

| NAME | DESCRIPTION | VALUE | UNIT |

|---|---|---|---|

| RθJA | Junction-to-free air | 25.5 | °C/W |

| ωJT | Junction-to-package top | 1.8 | |

| ωJB | Junction-to-board | 13.7 | |

| Custom Typical Application Board(1) | |||

| RθJA | Junction-to-free air | 24.5 | °C/W |

| ωJT | Junction-to-package top | 0.9 | |

| ωJB | Junction-to-board | 11 | |

(1) Custom Typical Application Board Characteristics:

SPACER

ΨJB = (TJ – TB)/(Total Device Power Dissipation)

ΨJB = (TJ TJ = Device Junction Temperature

ΨJB = (TJ TB = Temperature of PCB 1 mm from device edge.

SPACER

ΨJT = (TJ – TC)/(Total Device Power Dissipation)

ΨJB = (TJ TJ = Device Junction Temperature

ΨJB = (TJ TC = Hottest temperature on the case of the package.

- 10x15 inches

- 12 layer

- 8 power/ground layers – 95% copper (1oz)

- 4 signal layers – 20% copper (1oz)

SPACER

ΨJB = (TJ – TB)/(Total Device Power Dissipation)

ΨJB = (TJ TJ = Device Junction Temperature

ΨJB = (TJ TB = Temperature of PCB 1 mm from device edge.

SPACER

ΨJT = (TJ – TC)/(Total Device Power Dissipation)

ΨJB = (TJ TJ = Device Junction Temperature

ΨJB = (TJ TC = Hottest temperature on the case of the package.

5.5 Electrical Characteristics: High Speed Side Serial Transmitter

| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOD(p-p) | TX Output differential peak-to-peak voltage swing, transmitter enabled | SWING = 0000 | 50 | 130 | 220 | mVpp |

| SWING = 0001 | 110 | 220 | 320 | |||

| SWING = 0010 | 180 | 300 | 430 | |||

| SWING = 0011 | 250 | 390 | 540 | |||

| SWING = 0100 | 320 | 480 | 650 | |||

| SWING = 0101 | 390 | 570 | 770 | |||

| SWING = 0110 | 460 | 660 | 880 | |||

| SWING = 0111 | 530 | 750 | 1000 | |||

| SWING = 1000 | 590 | 830 | 1100 | |||

| SWING = 1001 | 660 | 930 | 1220 | |||

| SWING = 1010 | 740 | 1020 | 1320 | |||

| SWING = 1011 | 820 | 1110 | 1430 | |||

| SWING = 1100 | 890 | 1180 | 1520 | |||

| SWING = 1101 | 970 | 1270 | 1610 | |||

| SWING = 1110 | 1060 | 1340 | 1680 | |||

| SWING = 1111 | 1090 | 1400 | 1740 | |||

| Transmitter disabled | 30 | |||||

| Vpre/post | TX Output pre/post cursor emphasis voltage | See register bits TWPOST1, TWPOST2, and TWPRE for de-emphasis settings. See Figure 6-2 |

–17.5/ –37.5% |

+17.5/ +37.5% |

||

| VCMT | TX Output common mode voltage | 100-Ω differential termination. DC-coupled. | VDDT - 0.25 * VOD(p-p) | mV | ||

| tskew | Intra-pair output skew | Serial Rate = 9.8304 Gbps | 0.045 | UI | ||

| Tr, Tf | Differential output signal rise, fall time (20% to 80%), Differential Load = 100Ω |

24 | ps | |||

| JT1 | Serial output total jitter (CPRI LV/LV-II/LV-III, OBSAI and 10GBASE-KR Rates) | Serial Rate ≤ 3.072Gbps | 0.35 | UIpp | ||

| Serial Rate > 3.072Gbps | 0.28 | |||||

| JD1 | Serial output deterministic jitter (CPRI LV/LV-II/LV-III, OBSAI and 10GBASE-KR Rates) | Serial Rate ≤ 3.072Gbps | 0.17 | UIpp | ||

| Serial Rate > 3.072Gbps | 0.15 | |||||

| JR1 | Serial output random jitter (CPRI LV/LV-II/LV-III, OBSAI and 10GBASE-KR Rates) | Serial Rate > 3.072Gbps | 0.15 | UIpp | ||

| JT2 | Serial output total jitter (CPRI E.12.HV) | Serial Rate = 1.2288Gbps | 0.279 | UIpp | ||

| JD2 | Serial output deterministic jitter (CPRI E.12.HV) | 0.14 | ||||

| SDD22 | Differential output return loss | 50 MHz < f < 2.5 GHz | 9 | dB | ||

| 2.5 GHz < f < 7.5 GHz | See (1) | dB | ||||

| SCC22 | Common-mode output return loss | 50 MHz < f < 2.5 GHz | 6 | dB | ||

| 2.5 GHz < f < 7.5 GHz | See (2) | dB | ||||

| T(LATENCY) | Transmit path latency | 10GBASE-KR mode | see Figure 7-6 | |||

| 1GBASE-KX mode | see Figure 7-9 | |||||

| General Purpose mode | see Figure 7-13 | |||||

(1) Differential input return loss, SDD22 = 9 – 12 log10(f / 2500MHz)) dB

(2) Common-mode output return loss, SDD22 = 6 – 12 log10(f / 2500MHz)) dB

5.6 Electrical Characteristics: High Speed Side Serial Receiver

| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VID | RX Input differential voltage, |RXP – RXN| | Full Rate, AC Coupled | 50 | 600 | mV | |

| Half/Quarter/Eighth Rate, AC Coupled | 50 | 800 | ||||

| VID(pp) | RX Input differential peak-to-peak voltage swing, 2×|RXP – RXN| | Full Rate, AC Coupled | 100 | 1200 | mVpp | |

| Half/Quarter/Eighth Rate, AC Coupled | 100 | 1600 | ||||

| CI | RX Input capacitance | 2 | pF | |||

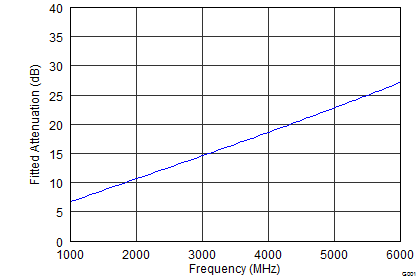

| JTOL | 10GBASE-KR Jitter tolerance, test channel with mTC =1 (see Figure 5-1 for attenuation curve), PRBS31 test pattern at 10.3125 Gbps | Applied sinusoidal jitter | 0.115 | UIpp | ||

| Applied random jitter | 0.130 | |||||

| Applied duty cycle distortion | 0.035 | |||||

| Broadband noise amplitude (RMS) | 5.2 | |||||

| SDD11 | Differential input return loss | 50 MHz < f < 2.5 GHz | 9 | dB | ||

| 2.5 GHz < f < 7.5 GHz | See (1) | |||||

| tskew | Intra-pair input skew | 0.23 | UI | |||

| t(LATENCY) | Receive path latency | 10GBASE-KR mode | see Figure 7-6 | |||

| 1GBASE-KX mode | see Figure 7-9 | |||||

| General Purpose mode | see Figure 7-13 | |||||

(1) Differential input return loss, SDD11 = 9 – 12 log10(f / 2.5GHz)) dB

5.7 Electrical Characteristics: Low Speed Side Serial Transmitter

| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOD(pp) | Transmitter output differential peak-to-peak voltage swing | SWING = 000 | 110 | 190 | 280 | mVpp |

| SWING = 001 | 280 | 380 | 490 | |||

| SWING = 010 | 420 | 560 | 700 | |||

| SWING = 011 | 560 | 710 | 870 | |||

| SWING = 100 | 690 | 850 | 1020 | |||

| SWING = 101 | 760 | 950 | 1150 | |||

| SWING = 110 | 800 | 1010 | 1230 | |||

| SWING = 111 | 830 | 1050 | 1270 | |||

| DE | Transmitter output de-emphasis voltage swing reduction | DE = 0000 | 0 | dB | ||

| DE = 0001 | 0.42 | |||||

| DE = 0010 | 0.87 | |||||

| DE = 0011 | 1.34 | |||||

| DE = 0100 | 1.83 | |||||

| DE = 0101 | 2.36 | |||||

| DE = 0110 | 2.92 | |||||

| DE = 0111 | 3.52 | |||||

| DE = 1000 | 4.16 | |||||

| DE = 1001 | 4.86 | |||||

| DE = 1010 | 5.61 | |||||

| DE = 1011 | 6.44 | |||||

| DE = 1100 | 7.35 | |||||

| DE = 1101 | 8.38 | |||||

| DE = 1110 | 9.54 | |||||

| DE = 1111 | 10.87 | |||||

| VCMT | Transmitter output common mode voltage | 100-Ω differential termination. DC-coupled. | VDDT - 0.5 * VOD(p-p) | mV | ||

| tskew | Intra-pair output skew | 0.045 | UI | |||

| tR, tF | Differential output signal rise, fall time (20% to 80%) Differential Load = 100Ω | 30 | ps | |||

| JT | Serial output total jitter | 0.35 | UI | |||

| JD | Serial output deterministic jitter | 0.17 | UI | |||

| tskew | Lane-to-lane output skew | 50 | ps | |||

5.8 Electrical Characteristics: Low Speed Side Serial Receiver

| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VID | Receiver input differential voltage, |INP – INN| | Full Rate, AC Coupled | 50 | 600 | mV | |

| Half/Quarter Rate, AC Coupled | 50 | 800 | ||||

| VID(pp) | Receiver input differential peak-to-peak voltage swing 2×|INP – INN| | Full Rate, AC Coupled | 100 | 1200 | mVdfpp | |

| Half/Quarter Rate, AC Coupled | 100 | 1600 | ||||

| CI | Receiver input capacitance | 2 | pF | |||

| JTOL | Jitter tolerance, total jitter at serial input (DJ + RJ) (BER 10-15) | Zero crossing, Half/Quarter Rate | 0.66 | UIp-p | ||

| Zero crossing, Full Rate | 0.65 | |||||

| JDR | Serial input deterministic jitter (BER 10-15) | Zero crossing, Half/Quarter Rate | 0.50 | UIp-p | ||

| Zero crossing, Full Rate | 0.35 | |||||

| tskew | Intra-pair input skew | 0.23 | UI | |||

| tlane-skew | Lane-to-lane input skew | 30 | UI | |||

5.9 Electrical Characteristics: LVCMOS (VDDO):

| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOH | High-level output voltage | IOH = 2 mA, Driver Enabled (1.8V) | VDDO – 0.45 | VDDO | V | |

| IOH = 2 mA, Driver Enabled (1.5V) | 0.75 × VDDO | VDDO | ||||

| VOL | Low-level output voltage | IOL = –2 mA, Driver Enabled (1.8V) | 0 | 0.45 | V | |

| IOL = –2 mA, Driver Enabled (1.5V) | 0 | 0.25 × VDDO | ||||

| VIH | High-level input voltage | 0.65 × VDDO | VDDO + 0.3 | V | ||

| VIL | Low-level input voltage | –0.3 | 0.35 × VDDO | V | ||

| IIH, IIL | Receiver only | Low/High Input Current | ±170 | µA | ||

| IOZ | Driver only | Driver Disabled | ±25 | µA | ||

| Driver/Receiver With Pullup/Pulldown | Driver disabled With Pull Up/Down Enabled | ±195 | ||||

| CIN | Input capacitance | 3 | pF | |||

5.10 Electrical Characteristics: Clocks

| PARAMETER | TEST CONDITIONS | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|---|

| Reference Clock (REFCLK0P/N, REFCLK1P/N) | ||||||

| F | Frequency | 122.88 | 425 | MHz | ||

| FHSoffset | Accuracy | Relative to Nominal HS Serial Data Rate | –100 | 100 | ppm | |

| Relative to Incoming HS Serial Data Rate | –200 | 200 | ||||

| DC | Duty cycle | High Time | 45% | 50% | 55% | |

| VID | Differential input voltage | 250 | 2000 | mVpp | ||

| CIN | Input capacitance | 1 | pF | |||

| RIN | Differential input impedance | 100 | Ω | |||

| tRISE | Rise/fall time | 10% to 90% | 50 | 350 | ps | |

| Differential Output Clock (CLKOUTA/N) | ||||||

| F | Output frequency | 0 | 500 | MHz | ||

| VOD | Differential output voltage | Peak to peak | 1000 | 2000 | mVdfpp | |

| tRISE | Output rise time | 10% to 90%, 2pF lumped capacitive load, AC-Coupled | 350 | ps | ||

| RTERM | Output termination | CLKOUTAP/N × P/N to DVDD | 50 | Ω | ||

5.11 Timing Requirements

over recommended operating conditions (unless otherwise noted)| TEST CONDITIONS | MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| MDIO | ||||||

| tperiod | MDC period | See Figure 6-3 | 100 | ns | ||

| tsetup | MDIO setup to ↑ MDC | 10 | ns | |||

| thold | MDIO hold to ↑ MDC | 10 | ns | |||

| tvalid | MDIO valid from MDC ↑ | 0 | 40 | ns | ||

| JTAG | ||||||

| tperiod | TCK period | See Figure 6-4 | 66.67 | ns | ||

| tsetup | TDI/TMS/TRST_N setup to ↑ TCK | 3 | ns | |||

| thold | TDI/TMS/TRST_N hold from ↑ TCK | 5 | ns | |||

| tvalid | TDO delay from TCK Falling | 0 | 10 | ns | ||

5.12 Typical Characteristics