SLVSCG4C January 2016 – August 2020 TPD3S714-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 AEC-Q100 Qualified

- 8.3.2 Short-to-Battery and Short-to-Ground Protection on VBUS_CON

- 8.3.3 Short-to-Battery and Short-to-VBUS Protection on VD+, VD–

- 8.3.4 ESD Protection on VBUS_CON, VD+, VD–

- 8.3.5 Low RON nFET VBUS Switch

- 8.3.6 High Speed Data Switches

- 8.3.7 Hiccup Current Limit

- 8.3.8 Fast Overvoltage Response Time

- 8.3.9 Integrated Input Enable

- 8.3.10 Fault Output Signal

- 8.3.11 Thermal Shutdown Feature

- 8.3.12 16-pin SSOP Package

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DBQ|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6.9 Typical Characteristics

Figure 6-1 8-kV IEC Contact Waveform

Figure 6-1 8-kV IEC Contact Waveform Figure 6-3 Data Line I-V Curve

Figure 6-3 Data Line I-V Curve Figure 6-5 VD± Short-to-5 V (while Enabled) Across Temperature

Figure 6-5 VD± Short-to-5 V (while Enabled) Across Temperature Figure 6-7 VD± Short-to-18 V Across Temperature

Figure 6-7 VD± Short-to-18 V Across Temperature Figure 6-9 Overcurrent tBLANK Response Waveform

Figure 6-9 Overcurrent tBLANK Response Waveform Figure 6-11 VBUS Short-to-Ground Response Waveform

Figure 6-11 VBUS Short-to-Ground Response Waveform Figure 6-13 Data Switch Short-to-5 V Response Waveform

Figure 6-13 Data Switch Short-to-5 V Response Waveform Figure 6-15 USB2.0 Eye Diagram (No TPD3S714-Q1)

Figure 6-15 USB2.0 Eye Diagram (No TPD3S714-Q1) Figure 6-17 Data Switch Differential Bandwidth

Figure 6-17 Data Switch Differential Bandwidth Figure 6-19 Data Switch Crosstalk

Figure 6-19 Data Switch Crosstalk Figure 6-2 –8-kV IEC Contact Waveform

Figure 6-2 –8-kV IEC Contact Waveform Figure 6-4 VBUS tON Time

Figure 6-4 VBUS tON Time Figure 6-6 VD± Short-to-5 V (while Unpowered) Across Temperature

Figure 6-6 VD± Short-to-5 V (while Unpowered) Across Temperature Figure 6-8 Data Switch RON vs Bias Voltage

Figure 6-8 Data Switch RON vs Bias Voltage Figure 6-10 Overcurrent tBLANK_RETRY Response Waveform

Figure 6-10 Overcurrent tBLANK_RETRY Response Waveform Figure 6-12 VBUS Short-to-18 V Response Waveform

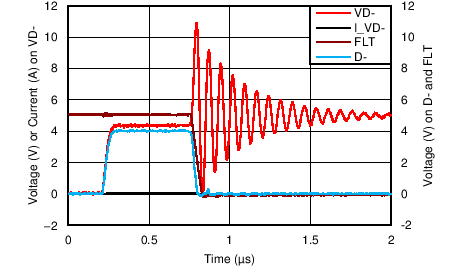

Figure 6-12 VBUS Short-to-18 V Response Waveform Figure 6-14 Data Switch Short-to-18 V Response Waveform

Figure 6-14 Data Switch Short-to-18 V Response Waveform Figure 6-16 USB2.0 Eye Diagram (With TPD3S714-Q1)

Figure 6-16 USB2.0 Eye Diagram (With TPD3S714-Q1) Figure 6-18 Data Switch Single-Ended Bandwidth

Figure 6-18 Data Switch Single-Ended Bandwidth