SLVSBQ8E December 2012 – October 2024 TPD4E1B06

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

5.6 Typical Characteristics

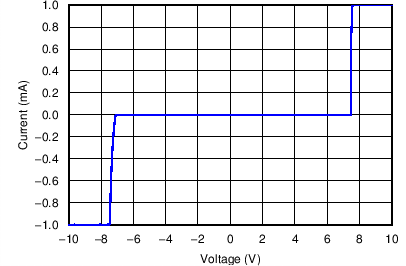

Figure 5-1 DC Voltage Sweep I-V Curve

Figure 5-1 DC Voltage Sweep I-V Curve Figure 5-3 TLP Plot IO to GND

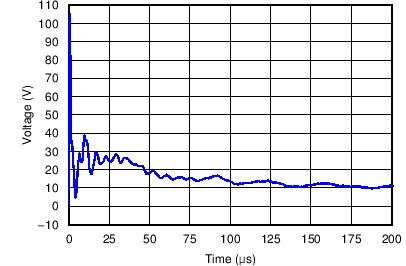

Figure 5-3 TLP Plot IO to GND Figure 5-5 +8 kV IEC Waveform

Figure 5-5 +8 kV IEC Waveform Figure 5-7 Insertion Loss

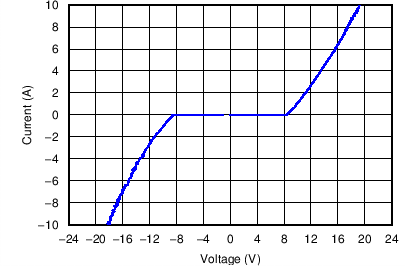

Figure 5-7 Insertion Loss Figure 5-2 Surge Curve (tp = 8/20 μs), Pin IO to GND

Figure 5-2 Surge Curve (tp = 8/20 μs), Pin IO to GND Figure 5-4 Leakage vs Temperature

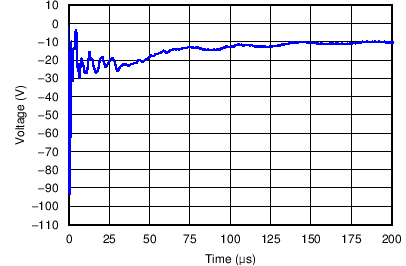

Figure 5-4 Leakage vs Temperature Figure 5-6 –8 kV IEC Waveform

Figure 5-6 –8 kV IEC Waveform Figure 5-8 Capacitance vs VBIAS

Figure 5-8 Capacitance vs VBIAS