SLVSCN2B June 2014 – July 2015 TPS22959

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Simplified Schematic

- 5 Revision History

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DNY|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9 Applications and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

9.1 Application Information

This section will highlight some of the design considerations when implementing this device in various applications. A PSPICE model for this device is also available in the product page of this device.

9.2 Typical Application

This application demonstrates how the TPS22959 can be used to power downstream modules with large capacitances. The example below is powering a 100-µF capacitive output load.

Figure 30. Typical Application Schematic for Powering a Downstream Module

Figure 30. Typical Application Schematic for Powering a Downstream Module

9.2.1 Design Requirements

For this design example, use the input parameters located in Table 2.

Table 2. Design Parameters

| DESIGN PARAMETER | EXAMPLE VALUE |

|---|---|

| VIN | 5.0 V |

| VBIAS | 5.0 V |

| Load current | 15 A |

9.2.2 Detailed Design Procedure

To begin the design process, the designer needs to know the following:

- VIN voltage

- VBIAS voltage

- Load current

9.2.2.1 VIN to VOUT Voltage Drop

The VIN to VOUT voltage drop in the device is determined by the RON of the device and the load current. The RON of the device depends upon the VIN and VBIAS conditions of the device. Refer to the RON specification of the device in the Electrical Characteristics table of this datasheet. Once the RON of the device is determined based upon the VIN and VBIAS conditions, use Equation 1 to calculate the VIN to VOUT voltage drop:

where

- ΔV = voltage drop from VIN to VOUT

- ILOAD = load current

- RON = on-resistance of the device for a specific VIN and VBIAS combination

An appropriate ILOAD must be chosen such that the IMAX specification of the device is not violated.

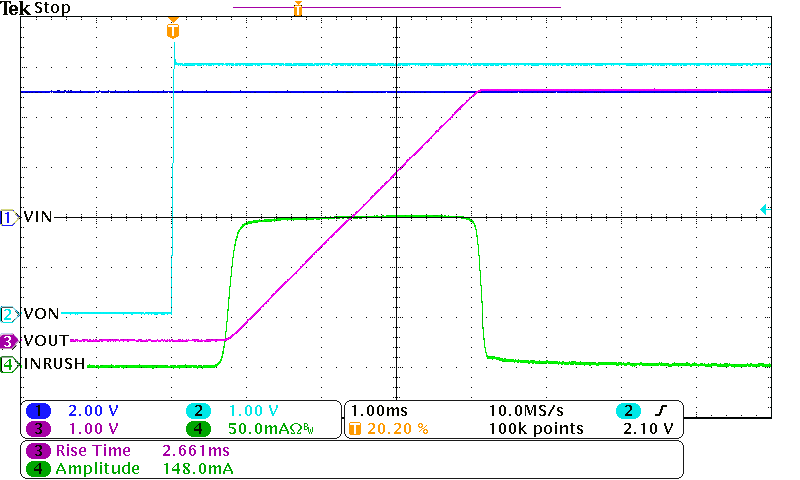

9.2.2.2 Inrush Current

To determine how much inrush current will be caused by the CL capacitor, use Equation 2:

where

- IINRUSH = amount of inrush caused by CL

- CL = capacitance on VOUT

- dt = time it takes for change in VOUT during the ramp up of VOUT when the device is enabled

- dVOUT = change in VOUT during the ramp up of VOUT when the device is enabled

An appropriate CL value should be placed on VOUT such that the IMAX and IPLS specifications of the device are not violated.

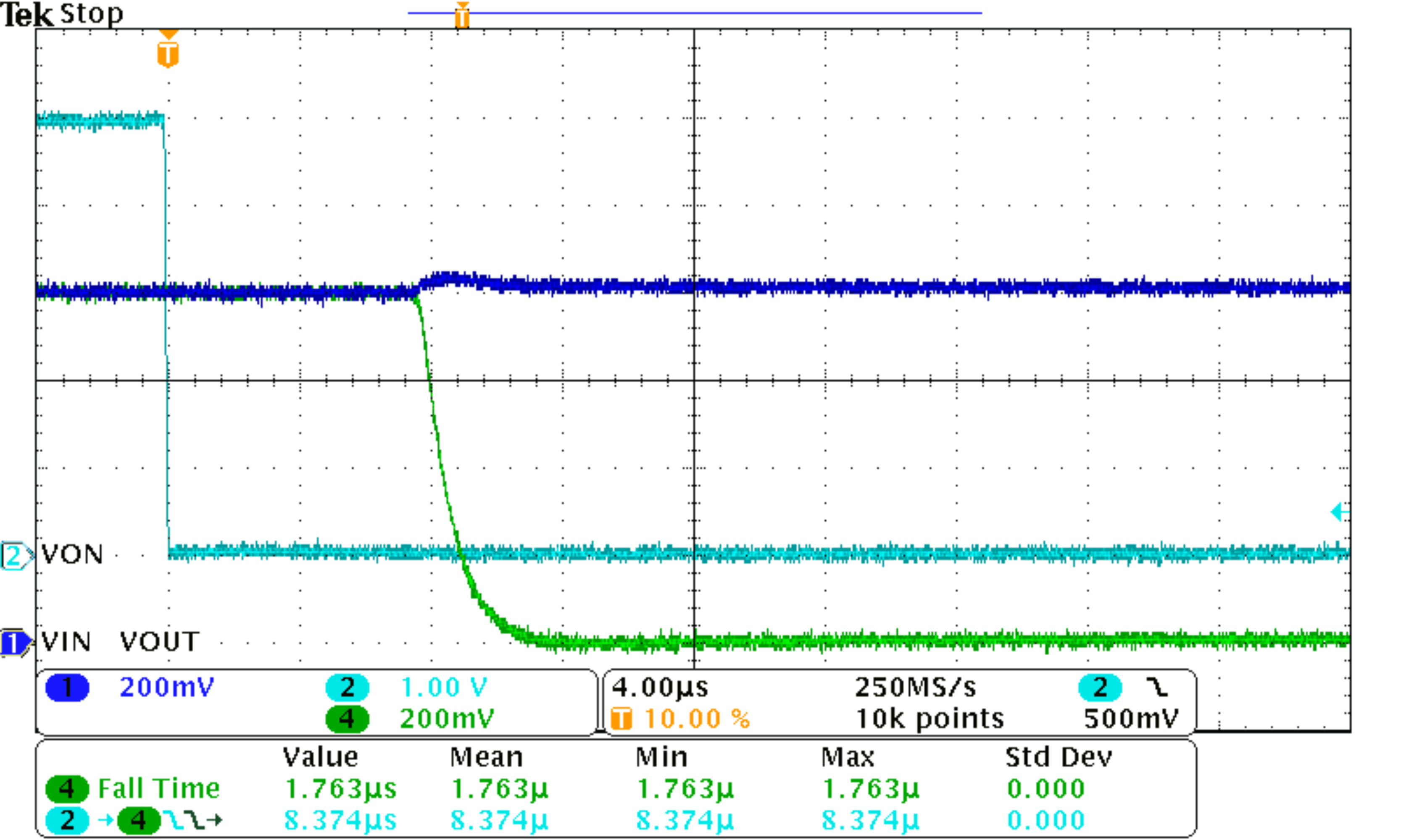

Figure 31. Inrush Current (VBIAS = 5 V, VIN = 5 V, CL = 100 µF)

Figure 31. Inrush Current (VBIAS = 5 V, VIN = 5 V, CL = 100 µF)

9.2.2.3 Thermal Considerations

The maximum IC junction temperature should be restricted to 125°C under normal operating conditions. To calculate the maximum allowable dissipation, PD(max) for a given output current and ambient temperature, use Equation 3.

where

- PD(max) = maximum allowable power dissipation

- TJ(max) = maximum allowable junction temperature (125°C for the TPS22959)

- TA = ambient temperature of the device

- θJA = junction to air thermal impedance. See Thermal Information section. This parameter is highly dependent upon board layout.

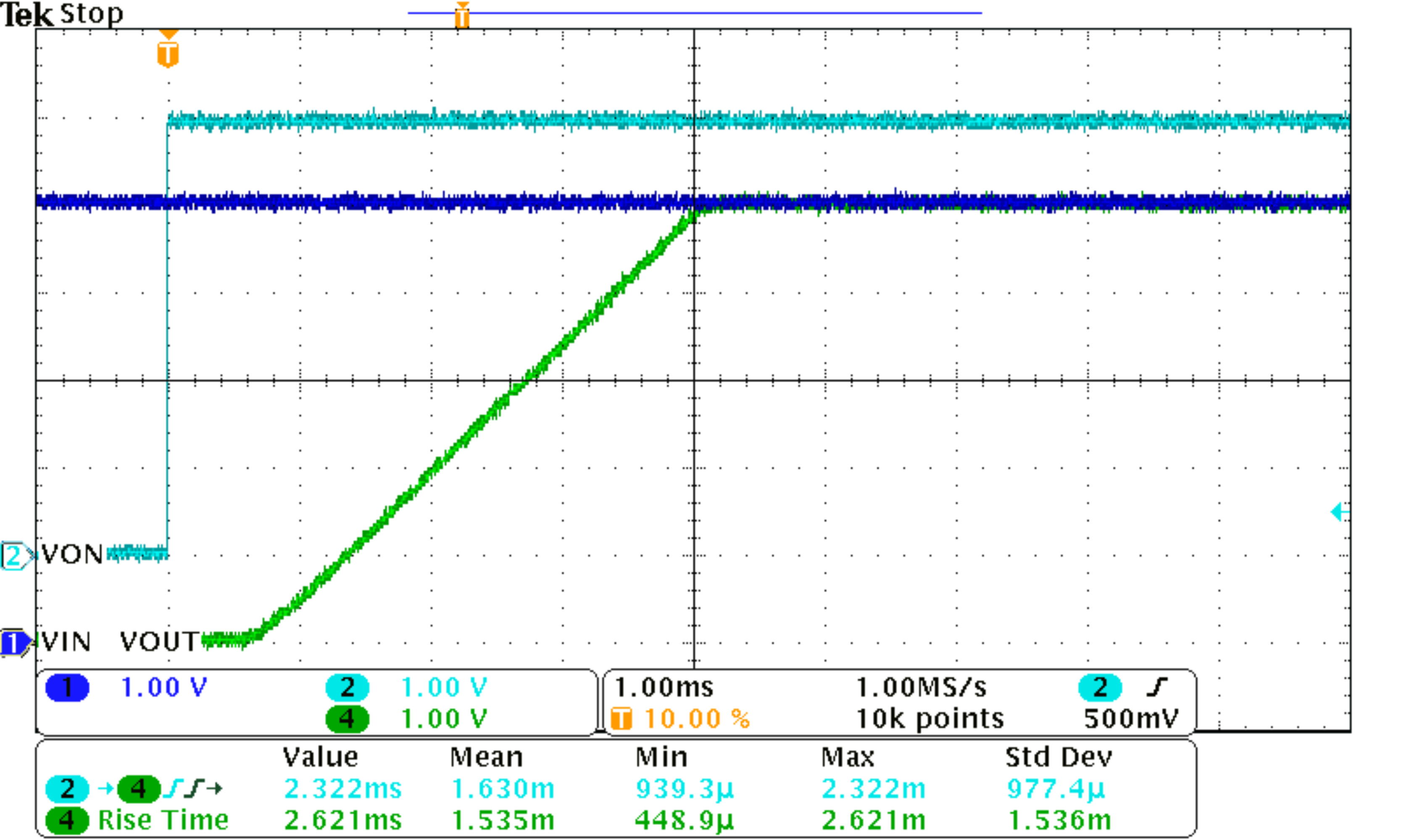

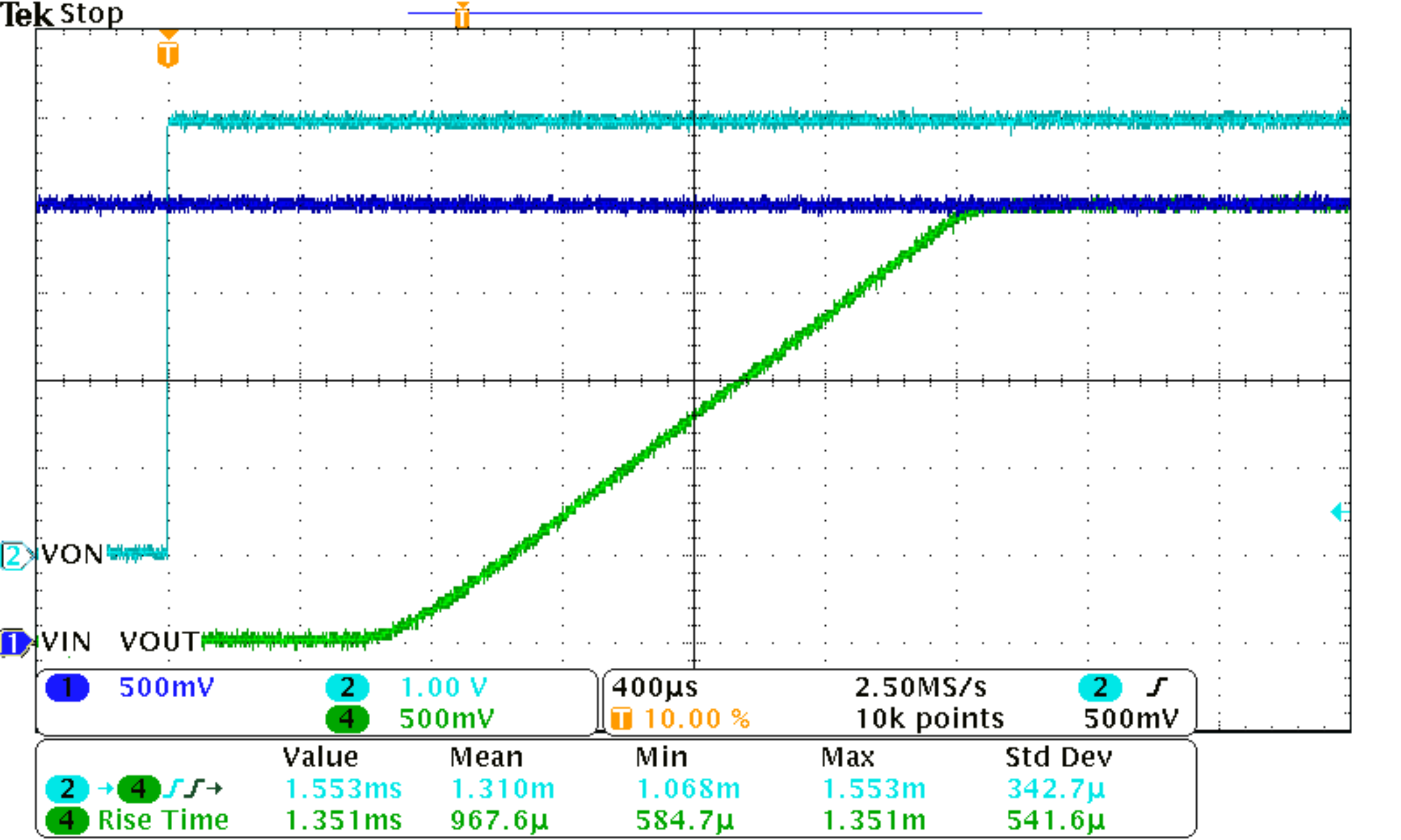

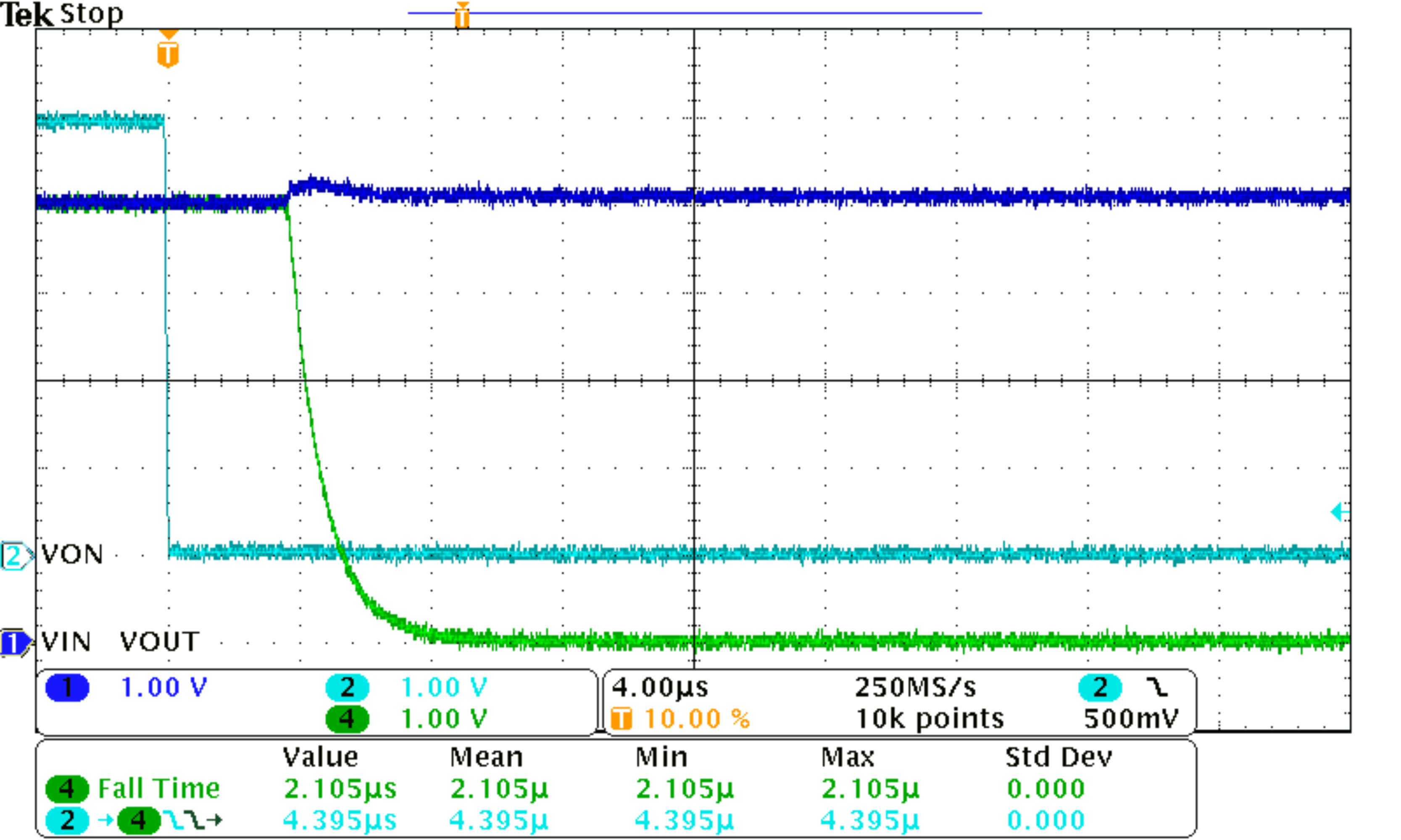

9.2.3 Application Curves

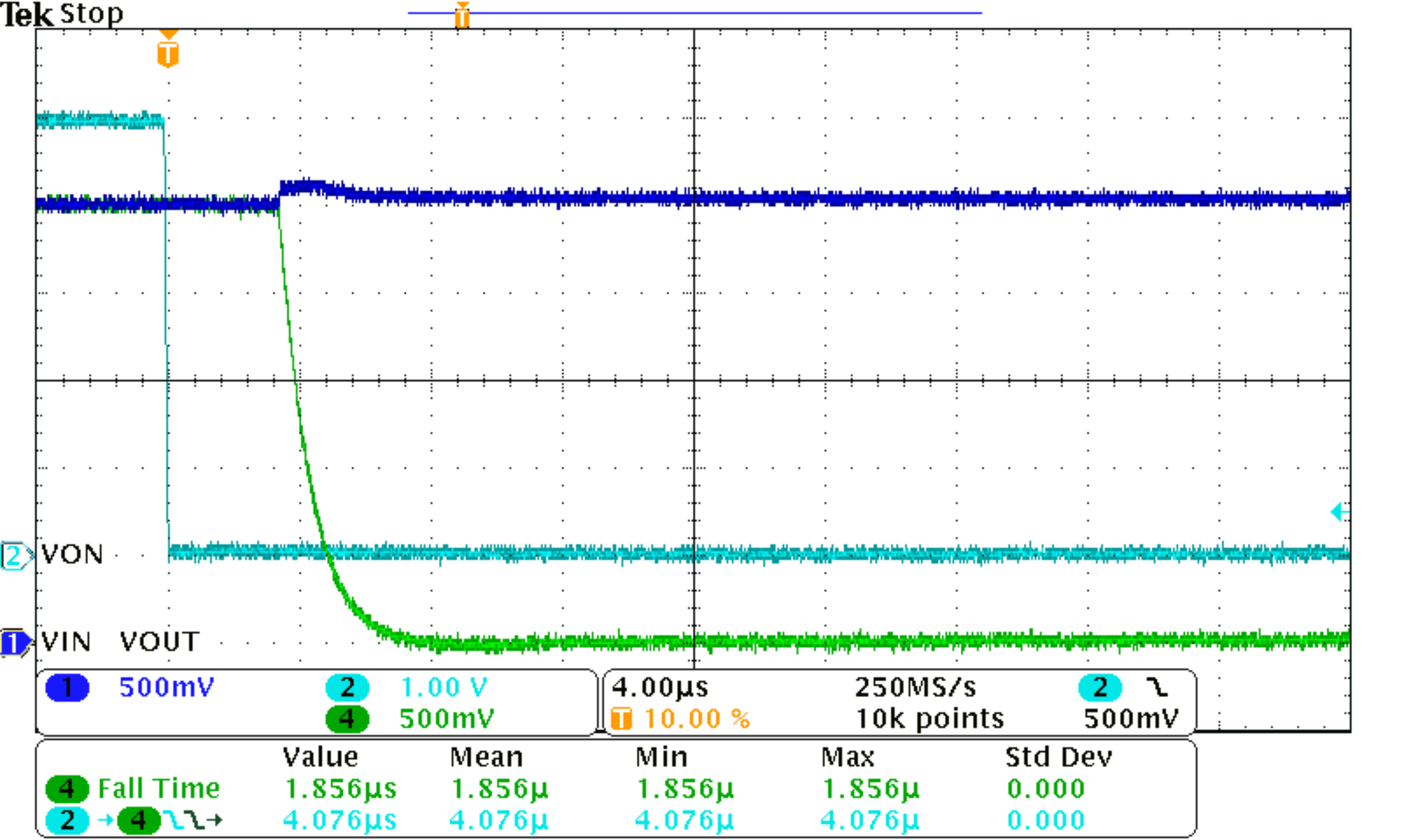

| VBIAS = 5 V | VIN = 5 V | CIN = 1 µF |

| CL = 0.1 µF |

| VBIAS = 2.5 V | VIN = 2.5 V | CIN = 1 µF |

| CL = 0.1 µF |

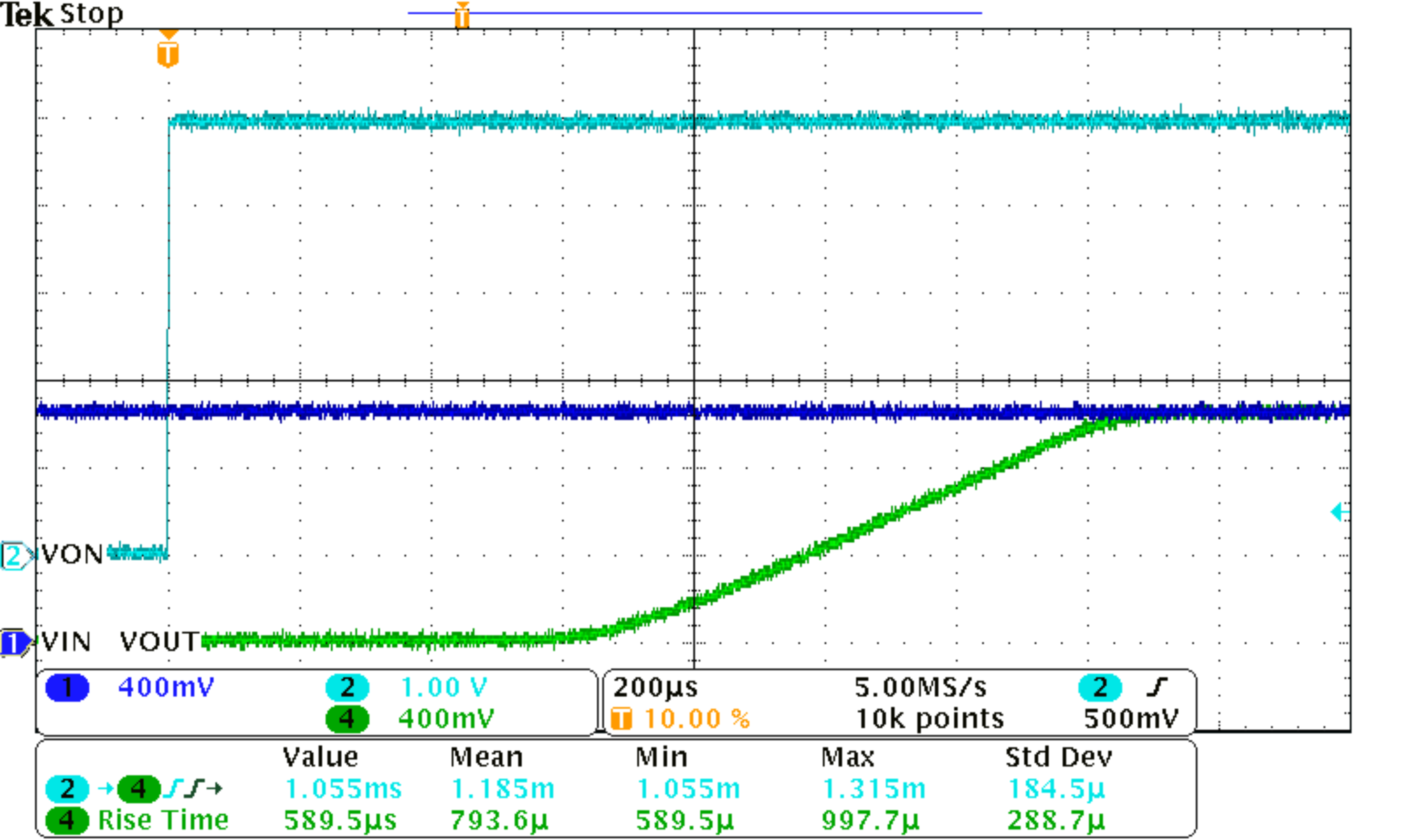

| VBIAS = 5 V | VIN = 5 V | CIN = 1 µF |

| CL = 0.1 µF |

| VBIAS = 2.5 V | VIN = 2.5 V | CIN = 1 µF |

| CL = 0.1 µF |

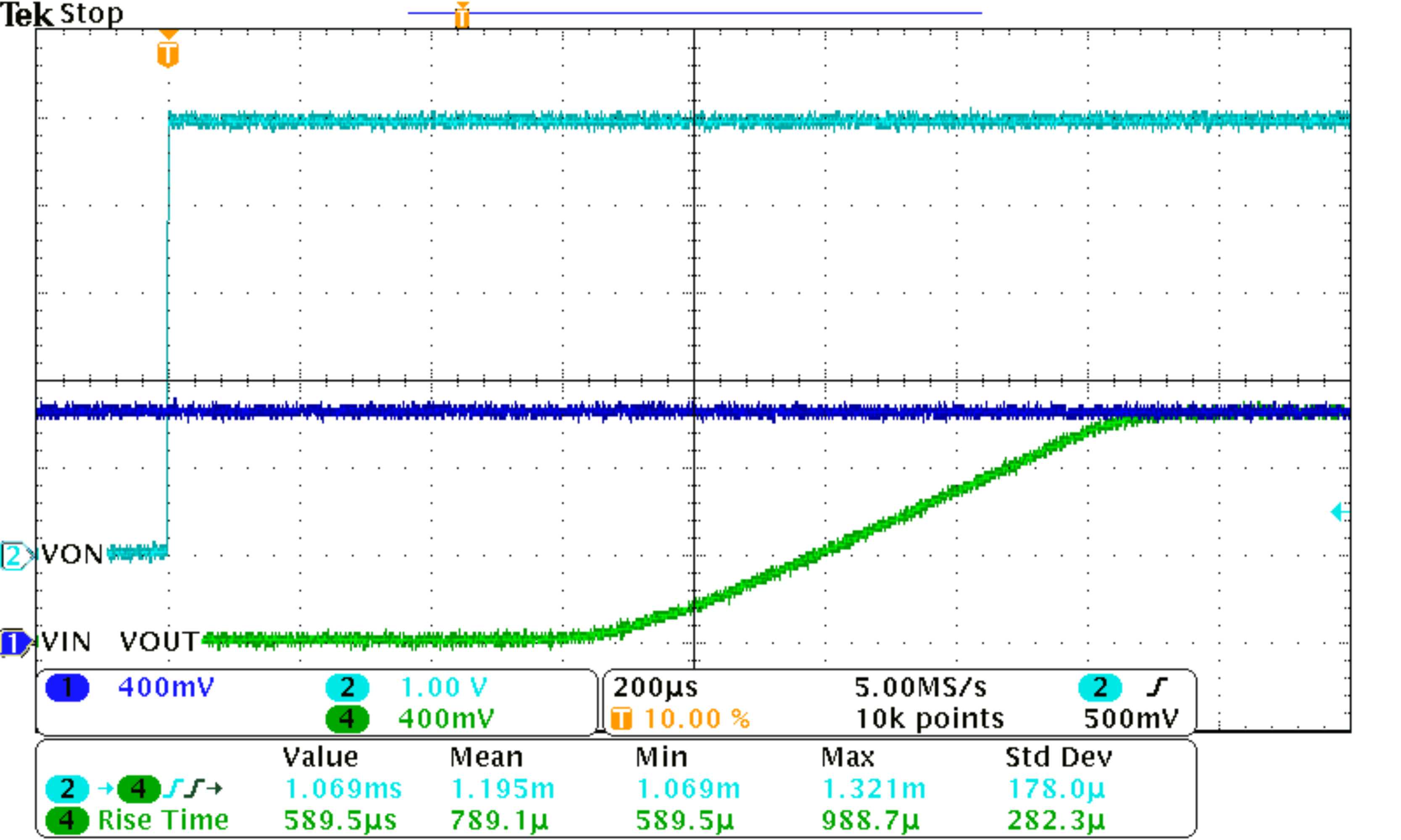

| VBIAS = 5 V | VIN = 1.05 V | CIN = 1 µF |

| CL = 0.1 µF |

| VBIAS = 2.5 V | VIN = 1.05 V | CIN = 1 µF |

| CL = 0.1 µF |

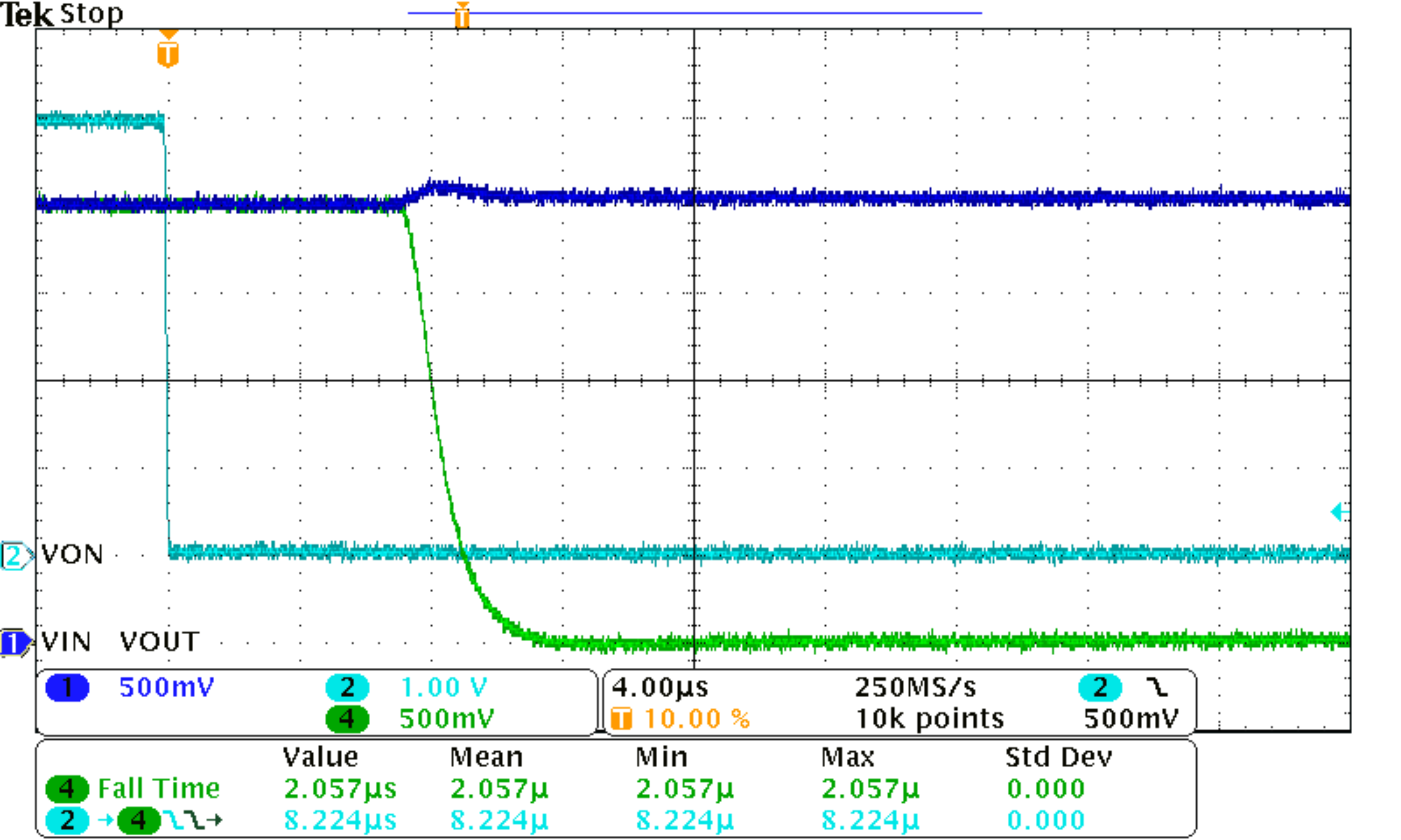

| VBIAS = 5 V | VIN = 2.5 V | CIN = 1 µF |

| CL = 0.1 µF |

| VBIAS = 2.5 V | VIN = 0.8 V | CIN = 1 µF |

| CL = 0.1 µF |