SLVSA76G March 2010 – January 2016 TPS65180B , TPS65181 , TPS65181B

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5

Register Maps

- 9.5.1 Thermistor Readout (TMST_VALUE) Register (Offset = 0x00h)

- 9.5.2 Enable (ENABLE) Register (Offset = 0x01h)

- 9.5.3 Positive Voltage Rail Adjustment (VP_ADJUST) Register (Offset = 0x02h)

- 9.5.4 Negative Voltage Rail Adjustment (VN_ADJUST) Register (Offset = 0x03h)

- 9.5.5 VCOM Adjustment (VCOM_ADJUST) Register (Offset = 0x04h)

- 9.5.6 Interrupt Enable 1 (INT_ENABLE1) Register (Offset = 0x05h)

- 9.5.7 Interrupt Enable 2 (INT_ENABLE2) Register (Offset = 0x06h)

- 9.5.8 Interrupt INT_STATUS1 (INT_STATUS1) Register (Offset = 0x07h)

- 9.5.9 Interrupt Status 2 (INT_STATUS2) Register (Offset = 0x08h)

- 9.5.10 Power Sequence Register 0 (PWR_SEQ0) Register (Offset = 0x09h)

- 9.5.11 Power Sequence Register 1 (PWR_SEQ1) Register (Offset = 0x0Ah)

- 9.5.12 Power Sequence Register 2 (PWR_SEQ2) Register (Offset = 0x0Bh)

- 9.5.13 Thermistor Configuration Register (TMST_CONFIG) (Offset = 0x0Ch)

- 9.5.14 Thermistor Hot Threshold (TMST_OS) Register (Offset = 0x0Dh)

- 9.5.15 Thermistor Cool Threshold (TMST_HYST) Register (Offset = 0x0Eh)

- 9.5.16 Power-Good Status (PG_STATUS) Register (Offset = 0x0Fh)

- 9.5.17 Revision and Version Control (REVID) Register (Offset = 0x10h)

- 9.5.18 I2C Read Pointer Control (FIX_READ_POINTER) Register (Offset = 0x11h) (TPS65181 and TPS65181B ONLY)

-

10Application and Implementation

- 10.1

Application Information

- 10.1.1 Dependencies Between Rails

- 10.1.2 Soft-Start

- 10.1.3 VCOM Adjustment

- 10.1.4 VCOM Adjustment Through Register Control

- 10.1.5 VCOM Adjustment Through External Potentiometer

- 10.1.6 VPOS and VNEG Supply Tracking

- 10.1.7 Fault Handling and Recovery

- 10.1.8 TPS65180 and TPS65180B Fault Handling

- 10.1.9 TPS65181 and TPS65181B Fault Handling

- 10.1.10 Power-Good Pin

- 10.1.11 Interrupt Pin

- 10.1.12 Panel Temperature Monitoring

- 10.1.13 NTC Bias Circuit

- 10.1.14 TPS65180 and TPS65180B Temperature Acquisition

- 10.1.15 TPS65181 and TPS65181B Temperature Acquisition

- 10.1.16 Overtemperature Reporting

- 10.1.17 Overtemperature Fault Queuing

- 10.1.18 TPS65181 and TPS65181B Temperature Sensor

- 10.1.19 I2C Bus Operation

- 10.2 Typical Application

- 10.1

Application Information

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGZ|48

Thermal pad, mechanical data (Package|Pins)

- RGZ|48

Orderable Information

8 Specifications

8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Input voltage at VIN, VINP, VIN3P3 | –0.3 | 7 | V | ||

| Ground pins to system ground | –0.3 | 0.3 | V | ||

| Voltage range at SDA, SCL, WAKEUP, PWR3, PWR2, PWR1, PWR0, VCOM_CTRL, VDDH_FB, VEE_FB, PWR_GOOD, nINT | –0.3 | 3.6 | V | ||

| VCOM_XADJ | –3.6 | 0.3 | V | ||

| Voltage on VB, VB_SW, VPOS_IN, VDDH_IN | –0.3 | 20 | V | ||

| Voltage on VN, VNEG_IN, VEE_IN, VCOM_PWR | –20 | 0.3 | V | ||

| Voltage from VINP to VN_SW | –0.3 | 30 | V | ||

| Peak output current | Internally limited | mA | |||

| Continuous total power dissipation | 2 | W | |||

| TJ | Operating junction temperature | –10 | 125 | °C | |

| TA | Operating ambient temperature(3) | –10 | 85 | °C | |

| Tstg | Storage temperature | –65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

(3) TI recommends that copper plane in proper size on board be in contact with die thermal pad to dissipate heat efficiently. Thermal pad is electrically connected to PBKG, which is supposed to be tied to the output of buck-boost converter. Thus wide copper trace in the buck-boost output helps heat dissipated efficiently.

8.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| Input voltage at VIN, VINP, VIN3P3 | 3 | 3.7 | 6 | V | |

| Voltage at SDA, SCL, WAKEUP, PWR3, PWR2, PWR1, PWR0, VCOM_CTRL, VDDH_FB, VEE_FB, VCOM_XADJ, PWR_GOOD, nINT | 0 | 3.6 | V | ||

| TA | Operating ambient temperature | –10 | 85 | °C | |

| TJ | Operating junction temperature | –10 | 125 | °C | |

8.4 Thermal Information

| THERMAL METRIC(1) | TPS6518x TPS6518xB |

UNIT | |

|---|---|---|---|

| RGZ (VQFN) | |||

| 48 PINS | |||

| RθJA | Junction-to-ambient thermal resistance (2) | 30.5 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 16.2 | °C/W |

| RθJB | Junction-to-board thermal resistance | 7.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.2 | °C/W |

| ψJB | Junction-to-board characterization parameter | 7.1 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | N/A | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) Estimated when mounted on high K JEDEC board per JESD 51-7 with thickness of 1.6 mm, 4 layers, size of 76.2 mm × 114.3 mm, and 2-oz. copper for top and bottom plane. Actual thermal impedance depends on PCB used in the application.

8.5 Electrical Characteristics

VIN = 3.7 V, TA = –10°C to 85ºC, Typical values are at TA = 25ºC (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| INPUT VOLTAGE | |||||||

| VIN | Input voltage range | 3 | 3.7 | 6 | V | ||

| VUVLO | Undervoltage lockout threshold | VIN falling | 2.9 | V | |||

| VHYS | Undervoltage lockout hysteresis | VIN rising | 400 | mV | |||

| INPUT CURRENT | |||||||

| IQ | Operating quiescent current into VIN | Device switching, no load | 5.5 | mA | |||

| ISTD | Operating quiescent current into VIN | Device in standby mode | 130 | µA | |||

| ISLEEP | Shutdown current | Device in sleep mode | 2.8 | 10 | µA | ||

| INTERNAL SUPPLIES | |||||||

| VINT_LDO1 | Internal supply | 2.7 | V | ||||

| VINT_LDO2 | Internal supply | 2.7 | V | ||||

| VREF | Internal supply | 2.25 | V | ||||

| DCDC1 (POSITIVE BOOST REGULATOR) | |||||||

| VIN | Input voltage range | 3 | 3.7 | 6 | V | ||

| VOUT | Output voltage range | 17 | V | ||||

| DC set tolerance | –5% | 5% | |||||

| IOUT | Output current | 160 | mA | ||||

| RDS(ON) | MOSFET on resistance | VIN = 3.7 V | 350 | mΩ | |||

| ILIMIT | Switch current limit | 1.5 | A | ||||

| Switch current accuracy | –30% | 30% | |||||

| fSW | Switching frequency | 1 | MHz | ||||

| L | Inductor | 2.2 | µH | ||||

| C | Capacitor | 2 × 4.7 | µF | ||||

| ESR | Capacitor ESR | 20 | mΩ | ||||

| DCDC2 (INVERTING BUCK-BOOST REGULATOR) | |||||||

| VIN | Input voltage range | 3 | 3.7 | 6 | V | ||

| VOUT | Output voltage range | –17 | V | ||||

| DC set tolerance | –5% | 5% | |||||

| IOUT | Output current | 160 | mA | ||||

| RDS(ON) | MOSFET on resistance | VIN = 3.7 V | 350 | mΩ | |||

| ILIMIT | Switch current limit | 1.5 | A | ||||

| Switch current accuracy | –30% | 30% | |||||

| L | Inductor | 4.7 | µH | ||||

| C | Capacitor | 2 × 4.7 | µF | ||||

| ESR | Capacitor ESR | 20 | mΩ | ||||

| LDO1 (VPOS) | |||||||

| VPOS_IN | Input voltage range | 16.15 | 17 | 17.85 | V | ||

| VSET | Output voltage set value | VIN = 17 V, VPOS_SET[2:0] = 0x0h to 0x7h |

14.25 | 15 | 15.75 | V | |

| VINTERVAL | Output voltage set resolution | VIN = 17 V | 250 | mV | |||

| VPOS_OUT | Output voltage range | VSET = 15 V, ILOAD = 20 mA | 14.85 | 15 | 15.15 | V | |

| VOUTTOL | Output tolerance | VSET = 15 V, ILOAD = 20 mA | –1% | 1% | |||

| VDROPOUT | Dropout voltage | ILOAD = 120 mA | 250 | mV | |||

| VLOADREG | Load regulation – DC | ILOAD = 10% to 90% | 1% | ||||

| ILOAD | Load current range | 120 | mA | ||||

| ILIMIT | Output current limit | 200 | mA | ||||

| TSS | Soft-start time | 1 | ms | ||||

| C | Recommended output capacitor | 4.7 | µF | ||||

| LDO2 (VNEG) | |||||||

| VNEG_IN | Input voltage range | –17.85 | –17 | –16.15 | V | ||

| VSET | Output voltage set value | VIN = –17 V, VNEG_SET[2:0] = 0x0h to 0x7h |

–15.75 | –15 | –14.25 | V | |

| VINTERVAL | Output voltage set resolution | VIN = –17 V | 250 | mV | |||

| VNEG_OUT | Output voltage range | VSET = –15 V, ILOAD = –20 mA | –15.15 | –15 | –14.85 | V | |

| VOUTTOL | Output tolerance | VSET = –15 V, ILOAD = –20 mA | –1% | 1% | |||

| VDROPOUT | Dropout voltage | ILOAD = 120 mA | 250 | mV | |||

| VLOADREG | Load regulation – DC | ILOAD = 10% to 90% | 1% | ||||

| ILOAD | Load current range | 120 | mA | ||||

| ILIMIT | Output current limit | 200 | mA | ||||

| TSS | Soft-start time | 1 | ms | ||||

| C | Recommended output capacitor | 4.7 | µF | ||||

| LD01 (POS) AND LDO2 (VNEG) TRACKING | |||||||

| VDIFF | Difference between VPOS and VNEG | VSET = ±15 V, ILOAD = ±20 mA, 0°C to 60°C |

–50 | 50 | mV | ||

| VCOM DRIVER | |||||||

| VCOM | Accuracy | VCOM_SET[7:0] = 0x74h (–1.25 V) VIN = 3.4 V to 4.2 V, no load |

–0.8% | 0.8% | |||

| VCOM_SET[7:0] = 0x74h (–1.25 V) VIN = 3.0 V to 6.0 V, no load |

–1.5% | 1.5% | |||||

| Output voltage range | –2.5 | –0.3 | V | ||||

| Resolution | VCOM_ADJ = 1 V, 1 LSB | 11 | 17 | mV | |||

| G | VCOM gain (VCOM_XADJ/VCOM) | VCOM_ADJ = 0 V | 1 | V/V | |||

| VCOM SWITCH | |||||||

| TON | Switch ON-time | VCOM = –1.25 V, VCOM_PANEL = 0 V CVCOM = 4.7 µF, CVCOM_PANEL = 4.7 µF |

1 | ms | |||

| RDS(ON) | MOSFET ON-resistance | VCOM = –1.245 V, ICOM = 30 mA | 20 | 35 | Ω | ||

| ILIMIT | MOSFET current limit | Not tested in production | 200 | mA | |||

| ISWLEAK | Switch leakage current | VCOM = 0 V, VCOM_PANEL = –2.5 V |

8.3 | nA | |||

| VIN3P3 TO V3P3 SWITCH | |||||||

| RDS(ON) | MOSFET ON-resistance | VIN3P3 = 3.3 V, ID = 2 mA | 50 | Ω | |||

| CP1 (VDDH) CHARGE PUMP | |||||||

| VDDH_IN | Input voltage range | 16.15 | 17 | 17.85 | V | ||

| VFB | Feedback voltage | 1 | V | ||||

| Accuracy | –3% | 3% | |||||

| VDDH_OUT | Output voltage range | VSET = 22 V, ILOAD = 2 mA | 21 | 22 | 23 | V | |

| ILOAD | Load current range | 10 | mA | ||||

| fSW | Switching frequency | 560 | KHz | ||||

| CD | Recommended driver capacitor | 10 | nF | ||||

| CO | Recommended output capacitor | 4.7 | µF | ||||

| CP2 (VEE) NEGATIVE CHARGE PUMP | |||||||

| VEE_IN | Input voltage range | –17.75 | –17 | –16.15 | V | ||

| VFB | Feedback voltage | –1 | V | ||||

| Accuracy | –3% | 3% | |||||

| VEE_OUT | Output voltage range | VSET = –20 V, ILOAD = 3 mA | –21 | –20 | –19 | V | |

| ILOAD | Load current range | 12 | mA | ||||

| fSW | Switching frequency | 560 | KHz | ||||

| CD | Recommended driver capacitor | 10 | nF | ||||

| CO | Recommended output capacitor | 4.7 | µF | ||||

| THERMISTOR MONITOR(1) | |||||||

| ATMS | Temperature to voltage ratio | Not tested in production | –0.0158 | V/°C | |||

| OffsetTMS | Offset | Temperature = 0°C | 1.575 | V | |||

| VTMS_HOT | Temp hot trip voltage (T = 50°C) | TEMP_HOT_SET = 0x8C | 0.768 | V | |||

| VTMS_COOL | Temp hot escape voltage (T = 45°C) | TEMP_COOL_SET = 0x82 | 0.845 | V | |||

| VTMS_MAX | Maximum input level | 2.25 | V | ||||

| RNTC_PU | Internal pullup resistor | 7.307 | KΩ | ||||

| RLINEAR | External linearization resistor | 43 | KΩ | ||||

| ADCRES | ADC resolution | Not tested in production, 1 bit | 8.75 | mV | |||

| ADCDEL | ADC conversion time | Not tested in production | 19 | µs | |||

| TMSTTOL | Accuracy | Not tested in production | –2 | 2 | LSB | ||

| LOGIC LEVELS AND TIMING CHARTERISTICS (SCL, SDA, nINT, PWR_GOOD, PWRx, WAKEUP) | |||||||

| VOL | Output low threshold level | IO = 3 mA, sink current (SDA, nINT, PWR_GOOD) |

0.4 | V | |||

| VIL | Input low threshold level | 0.4 | V | ||||

| VIH | Input high threshold level | 1.2 | V | ||||

| I(bias) | Input bias current | VIO = 1.8 V | 1 | µA | |||

| tlow,WAKEUP | WAKEUP low time | minimum low time for WAKEUP pin | 150 | ms | |||

| fSCL | SCL clock frequency | 400 | KHz | ||||

| OSCILLATOR | |||||||

| fOSC | Oscillator frequency | 9 | MHz | ||||

| Frequency accuracy | TA = –40°C to 85°C | –10% | 10% | ||||

| THERMAL SHUTDOWN | |||||||

| TSHTDWN | Thermal trip point | 150 | °C | ||||

| Thermal hysteresis | 20 | °C | |||||

(1) 10-kΩ Murata NCP18XH103F03RB thermistor (1%) in parallel with a linearization resistor (43 kΩ, 1%) are used at TS pin for panel temperature measurement.

8.6 Data Transmission Timing

VBAT = 3.6 V ±5%, TA = 25ºC, CL = 100 pF (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| f(SCL) | Serial clock frequency | 100 | 400 | KHz | ||

| tHD;STA | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | SCL = 100 KHz | 4 | µs | ||

| SCL = 400 KHz | 600 | ns | ||||

| tLOW | LOW period of the SCL clock | SCL = 100 KHz | 4.7 | µs | ||

| SCL = 400 KHz | 1.3 | |||||

| tHIGH | HIGH period of the SCL clock | SCL = 100 KHz | 4 | µs | ||

| SCL = 400 KHz | 600 | ns | ||||

| tSU;STA | Set-up time for a repeated START condition | SCL = 100 KHz | 4.7 | µs | ||

| SCL = 400 KHz | 600 | ns | ||||

| tHD;DAT | Data hold time | SCL = 100 KHz | 0 | 3.45 | µs | |

| SCL = 400 KHz | 0 | 900 | ns | |||

| tSU;DAT | Data set-up time | SCL = 100 KHz | 250 | ns | ||

| SCL = 400 KHz | 100 | |||||

| tr | Rise time of both SDA and SCL signals | SCL = 100 KHz | 1000 | ns | ||

| SCL = 400 KHz | 300 | |||||

| tf | Fall time of both SDA and SCL signals | SCL = 100 KHz | 300 | ns | ||

| SCL = 400 KHz | 300 | |||||

| tSU;STO | Set-up time for STOP condition | SCL = 100 KHz | 4 | µs | ||

| SCL = 400 KHz | 600 | ns | ||||

| tBUF | Bus free time between stop and start condition | SCL = 100 KHz | 4.7 | µs | ||

| SCL = 400 KHz | 1.3 | |||||

| tSP | Pulse width of spikes which mst be suppressed by the input filter | SCL = 100 KHz | n/a | n/a | ns | |

| SCL = 400 KHz | 0 | 50 | ||||

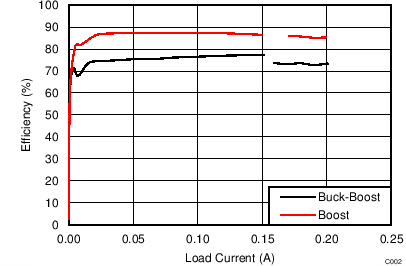

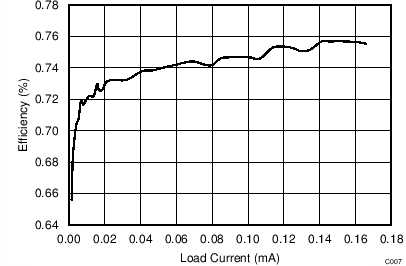

8.7 Typical Characteristics

Figure 1. Efficiency vs Load Current

Figure 1. Efficiency vs Load Current

Figure 2. Load Current vs Efficiency

Figure 2. Load Current vs Efficiency