SLVSD66 September 2015 TPS65233-1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RTE|16

Thermal pad, mechanical data (Package|Pins)

- RTE|16

Orderable Information

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

TPS65233-1 is a monolithic voltage regulator, specifically to provide the 13-V/18-V power supply and the 22-kHz tone signaling to the LNB down-converter, with I2C interface. I2C GUI software is shared with TPS65233 which is available on ti.com.

8.2 Typical Application

Figure 15. Application Schematic

Figure 15. Application Schematic

8.2.1 Detailed Design Procedure

8.2.1.1 Capacitor Selection

In TPS65233-1, a 1-MHz non-synchronous boost converter is integrated and the boost converter features the internal compensation network. 4.7 µH and 10 µH boost inductor are recommended. TPS65233-1 works fine with both ceramic capacitor and electrolytic capacitor. The ceramic capacitors rated at least X7R, 1206 size are preferred for the lower LNB output ripple. Table 8 shows the recommended ceramic capacitors list for both 4.7 µH and 10 µH boost inductors. Minimum output capacitor at the output of the boost converter is 2 × 10-µF/25-V ceramic capacitor when 4.7-µH inductor is selected.

Boost converter is stable with both ceramic capacitor and electrolytic capacitor. If lower cost is demanded, a 100-µF electrolytic and a 1-µF/35-V ceramic capacitor work well, this solution provides lower system cost.

Table 8. Boost Inductor and Capacitor Selections

| BOOST INDUCTOR | BOOST OUTPUT CAPACITOR (CERAMIC) |

|---|---|

| 10 µH | 2 × 22 µF, 25 V, 1206 |

| 2 × 10 µF, 35 V, 1206 | |

| 1 × 22 µF, 35 V, 1206 | |

| 2 × 22 µF, 35 V, 1206 | |

| 4.7 µH | 2 × 10 µF, 25 V, 1206 |

| 2 × 22 µF, 25 V, 1206 | |

| 1 × 22 µF, 35 V, 1206 | |

| 2 × 10 µF, 35 V, 1206 | |

| 2 × 22 µF, 35 V, 1206 |

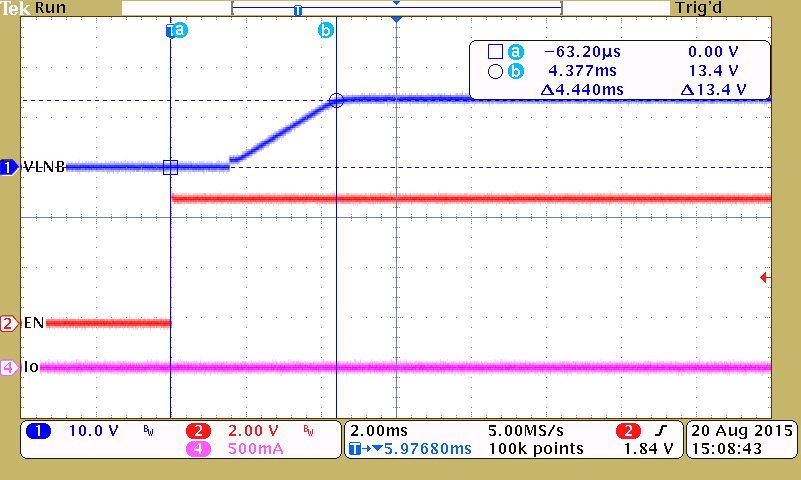

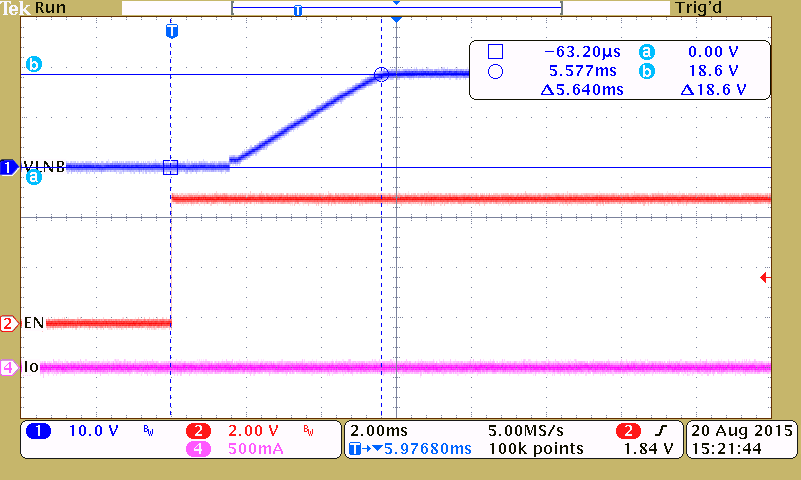

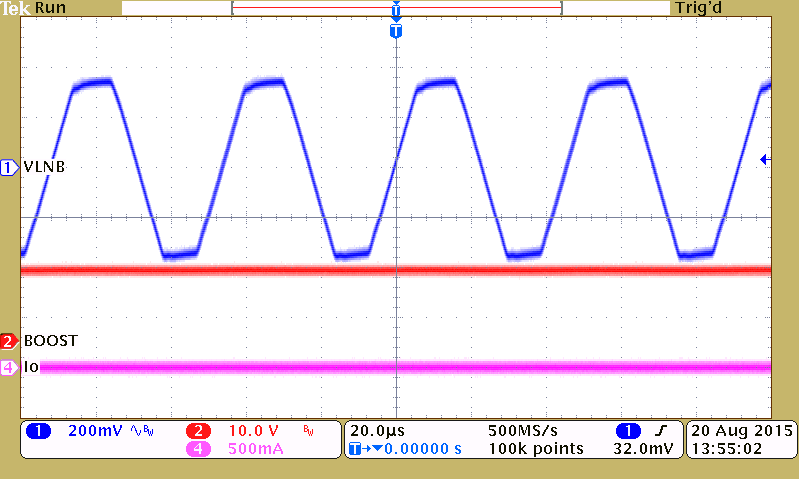

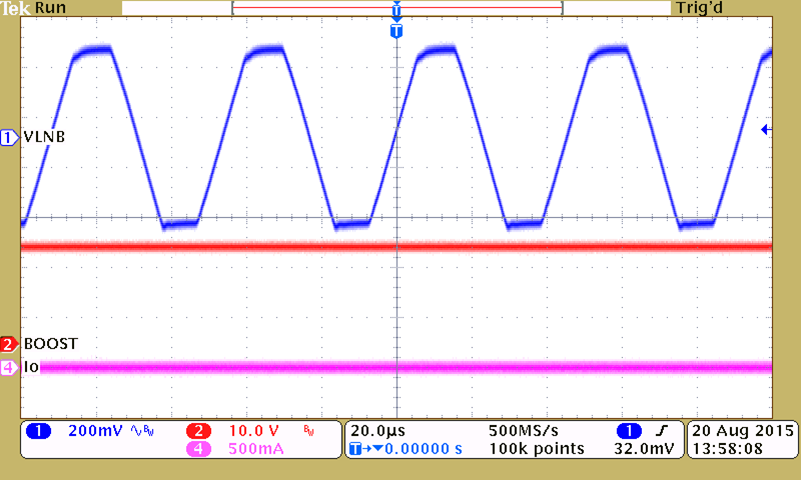

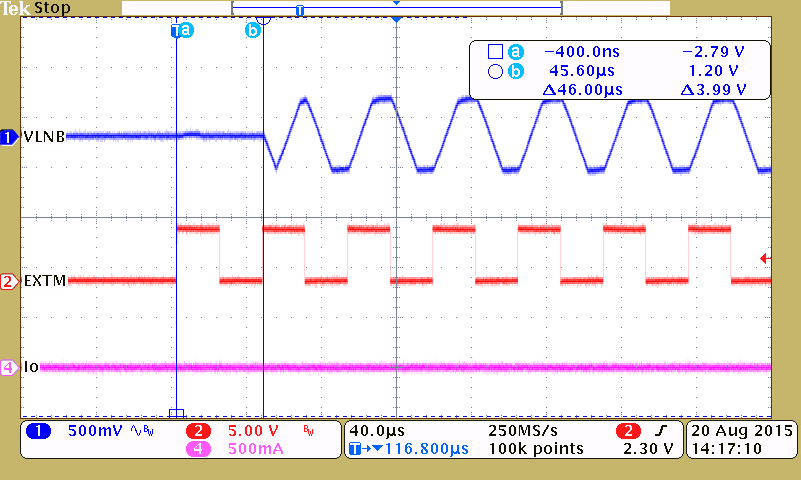

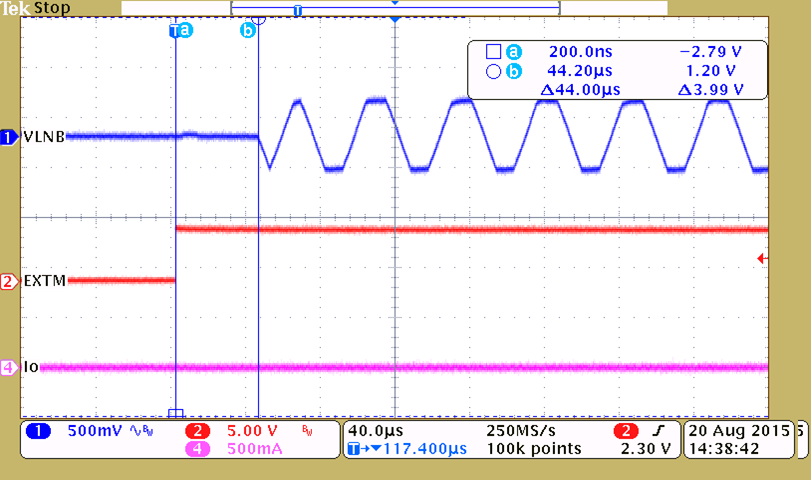

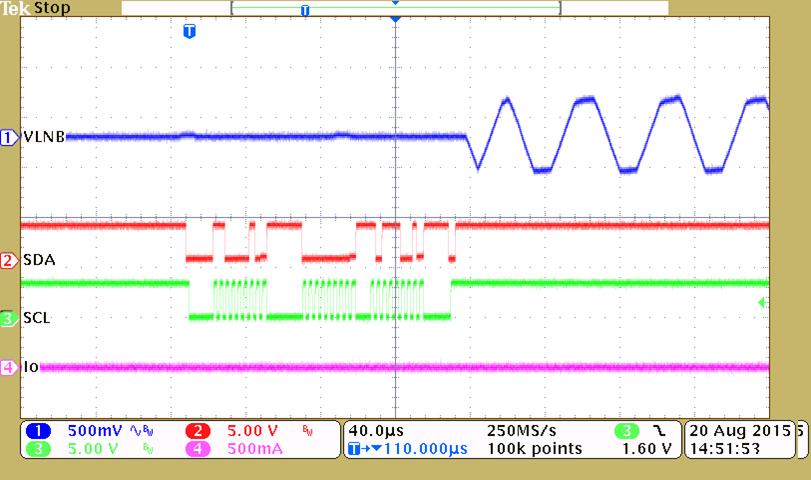

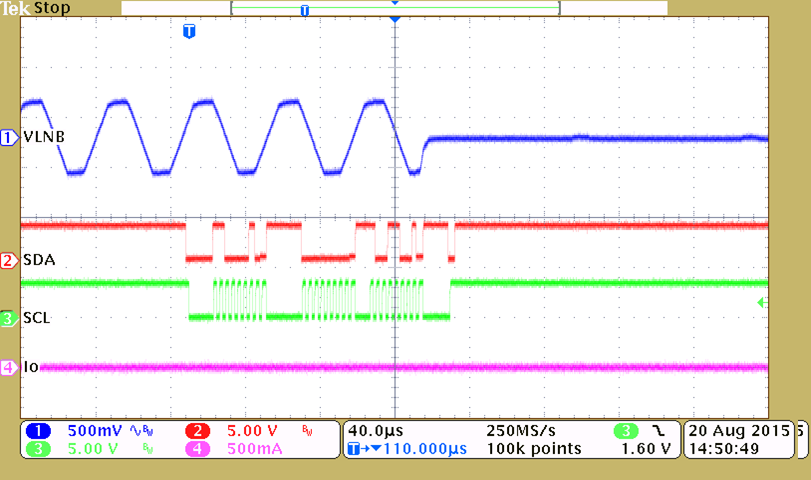

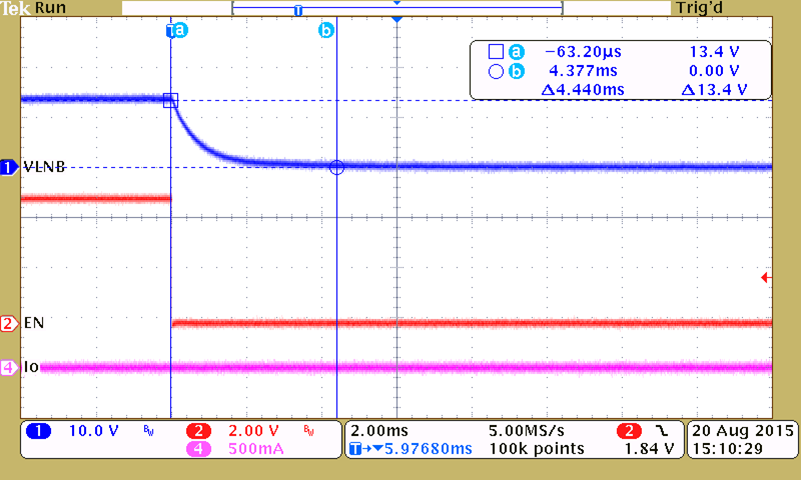

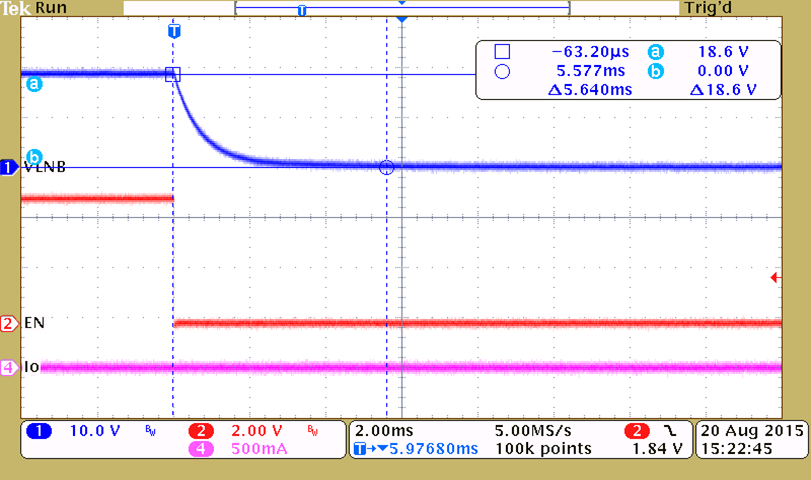

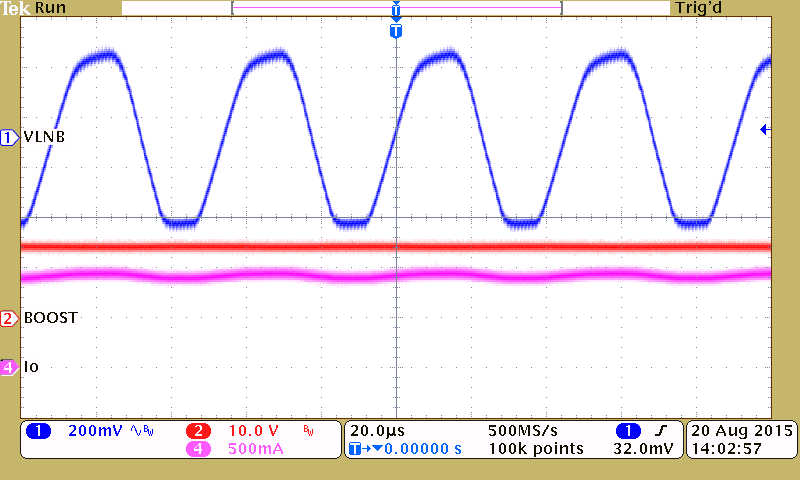

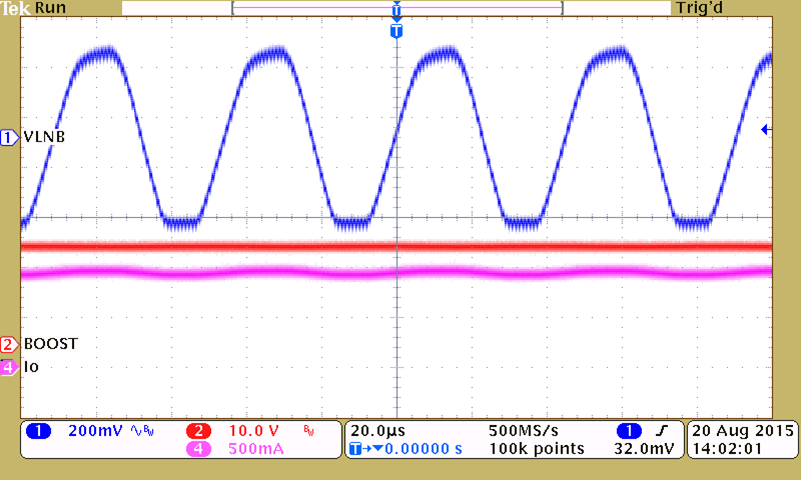

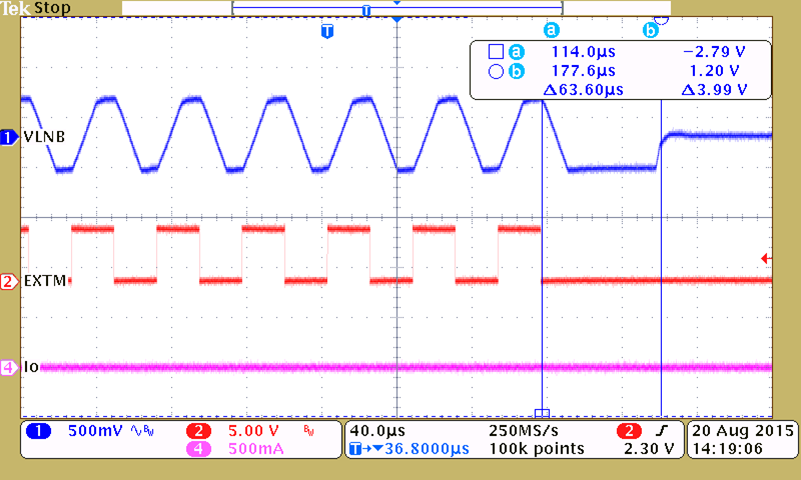

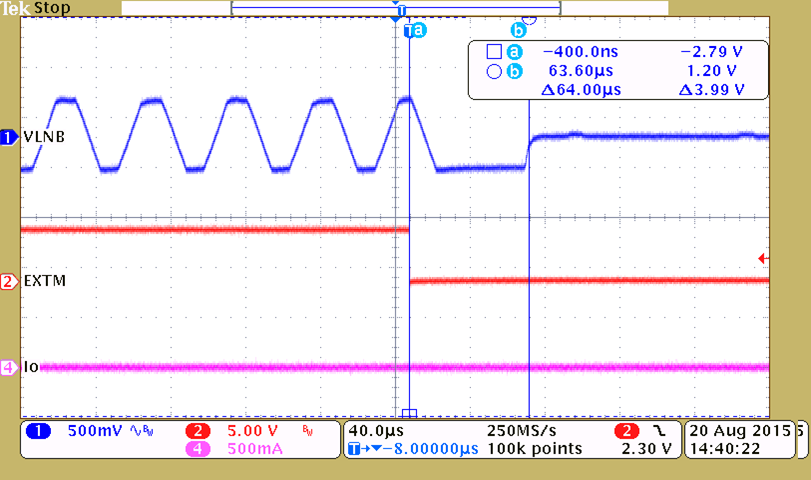

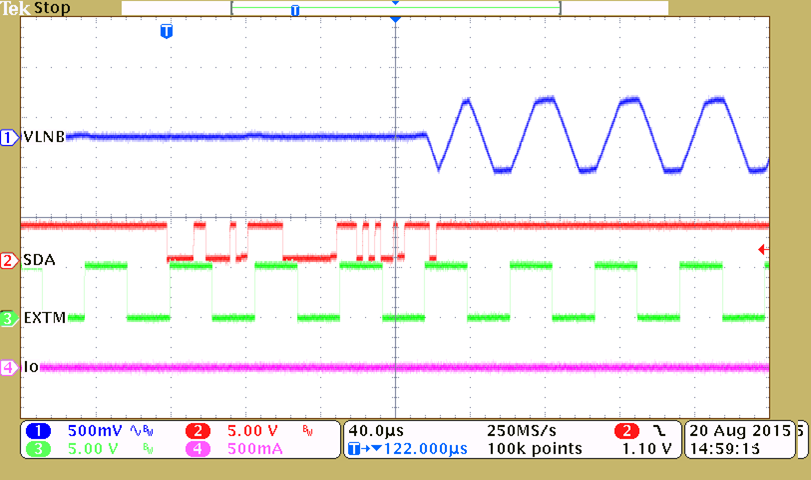

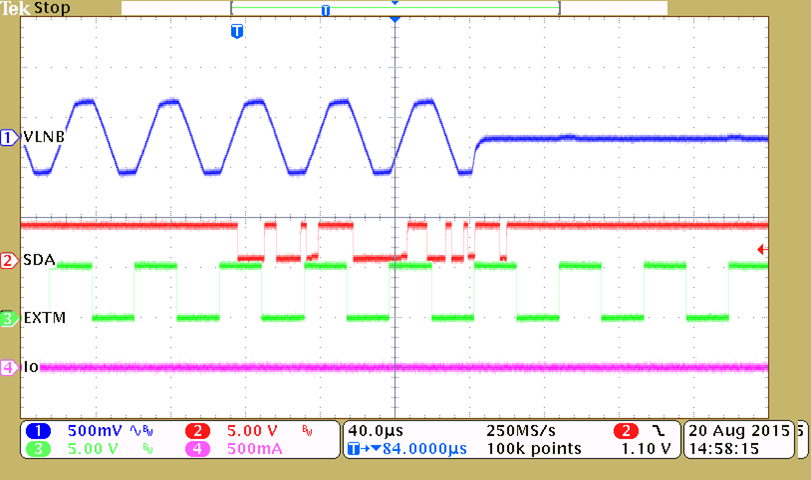

8.2.2 Application Curves