SWCS106F March 2013 – July 2016 TPS659119-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Characteristics

- 7.5 External Component Recommendation

- 7.6 I/O Pullup and Pulldown Characteristics

- 7.7 Digital I/O Voltage Electrical Characteristics

- 7.8 I2C Interface and Control Signals

- 7.9 Switching Characteristics—I2C Interface and Control Signals

- 7.10 Power Consumption

- 7.11 Power References and Thresholds

- 7.12 Thermal Monitoring and Shutdown

- 7.13 32-kHz RTC Clock

- 7.14 VRTC LDO

- 7.15 VIO SMPS

- 7.16 VDD1 SMPS

- 7.17 VDD2 SMPS

- 7.18 EXTCTRL

- 7.19 LDO1 AND LDO2

- 7.20 LDO3 and LDO4

- 7.21 LDO5

- 7.22 LDO6 and LDO7

- 7.23 LDO8

- 7.24 Timing Requirements for Boot Sequence Example

- 7.25 Power Control Timing Requirements

- 7.26 Device SLEEP State Control Timing Requirements

- 7.27 Supplies State Control Through EN1 and EN2 Timing Characteristics

- 7.28 VDD1 Supply Voltage Control Through EN1 Timing Requirements

- 7.29 Typical Characteristics

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PFP|80

Thermal pad, mechanical data (Package|Pins)

- PFP|80

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||||

|---|---|---|---|---|---|---|

| Voltage | VCC1, VCC2, VCCIO, VCC3, VCC4, VCC5, VCC7, VCC8 | –0.3 | 7 | V | ||

| VCC6, VDDIO | –0.3 | 3.6 | V | |||

| SW1, SW2, SWIO | –0.3 | 7 | V | |||

| 10 ns Transient | –2 | 7 | V | |||

| VFB1,VFB2,VFBIO | –0.3 | 3.6 | V | |||

| VOUT, VSENSE | –0.3 | 7 | V | |||

| BOOT1 | –0.3 | VRTCMAX + 0.3 | V | |||

| SDA_SDI, SCL_SCK, EN2, EN1, SLEEP, INT1, CLK32KOUT, NRESPWRON | –0.3 | VDDIOMAX + 0.3 | V | |||

| PWRON | –0.3 | 7 | V | |||

| PWRHOLD, GPIO0 | –0.3 | 7 | V | |||

| OSCEXT32K, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, GPIO7, GPIO8(2) | –0.3 | 7 | V | |||

| HDRST | –0.3 | VRTCMAX + 0.3 | V | |||

| OSC16MIN, OSC16MOUT | –0.3 | 5.7 | V | |||

| NRESPWRON2(2) | –0.3 | 7 | V | |||

| PWRDN(3) | –0.3 | 7 | V | |||

| VCCS | –0.3 | 7 | V | |||

| Peak output current | All other pins than power resources | –5 | 5 | mA | ||

| Functional junction temperature | –45 | 150 | °C | |||

| Storage temperature, Tstg | –55 | 150 | °C | |||

7.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | ±2000 | V | |

| Charged-device model (CDM), per AEC Q100-011 | All pins | ±500 | |||

| Corner pins (1, 20, 21, 40, 41, 60, 61, and 80) | ±750 | ||||

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)Note: VCC7 should be connected to highest supply that is connected to device VCCx pin.

Exception: The VCC4, VCC5, VIN, and AVIN inputs can be higher than VCC7. VCCS can be higher than VCC7 if VMBBUF_BYPASS = 0 (buffer is enabled).

| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| Input voltage | VCC5, VCCS | 2.7 | 5.5 | V | ||

| VCC3, VCC4, VCC8 | 1.7 | 5.5 | V | |||

| VCC1, VCC2, VCCIO, VCC7 | 4 | 5 | 5.5 | V | ||

| VCC6, VDDIO | 1.4 | 3.3 | 3.6 | V | ||

| VSENSE | –0.1 | 6.5 | V | |||

| PWRON | 0 | 3.8 | 5.5 | V | ||

| SDA_SDI, SCL_SCK, EN2, EN1, SLEEP, INT1, CLK32KOUT | 1.65 | VDDIO | 3.45 | V | ||

| PWRHOLD, HDRTS | 1.65 | VRTC | 5.5 | V | ||

| GPIO0, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, GPIO7, GPIO8, PWRDN | 1.65 | VRTC | 5.5 | V | ||

| VCCS | 0 | 5.5 | V | |||

| OSCEXT32K | 0 | 5.5 | V | |||

7.4 Thermal Characteristics

over operating free-air temperature range (unless otherwise noted)| THERMAL METRIC(1) | TPS659119-Q1 | UNIT | |

|---|---|---|---|

| PFP (HTQFP) | |||

| 80 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 34.1 | °C/W |

| RθJC(top) | Junction-to-case(top) thermal resistance | 9.6 | °C/W |

| RθJB | Junction-to-board thermal resistance | 10.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.3 | °C/W |

| ψJB | Junction-to-board characterization parameter | 9.9 | °C/W |

| RθJC(bot) | Junction-to-case(bottom) thermal resistance | 0.9 | °C/W |

7.5 External Component Recommendation

For crystal oscillator components, see the 32-kHz RTC Clock section. Note: The VCC7 supply must have enough capacitance to specify that when the supply is switched off, voltage does not fall at a rate faster than 10 mV/ms. This ensures that RTC domain data is maintained.| MIN | NOM | MAX | UNIT | ||||

|---|---|---|---|---|---|---|---|

| POWER REFERENCES | |||||||

| CO(VREF) | VREF filtering capacitor | Connected from VREF to REFGND | 100 | nF | |||

| VDD1 SMPS | |||||||

| CI(VCC1) | Input capacitor | X5R or X7R dielectric | 10 | µF | |||

| CO(VDD1) | Output filter capacitor | X5R or X7R dielectric | 4 | 10 | 12 | µF | |

| CO filter capacitor ESR | f = 3 MHz | 10 | 300 | mΩ | |||

| LO(VDD1) | Inductor | 2.2 | µH | ||||

| DCRL | LO inductor dc resistor | 125 | mΩ | ||||

| VDD2 SMPS | |||||||

| CI(VCC2) | Input capacitor | X5R or X7R dielectric | 10 | µF | |||

| CO(VDD2) | Output filter capacitor | X5R or X7R dielectric | 4 | 10 | 12 | µF | |

| CO filter capacitor ESR | f = 3 MHz | 10 | 300 | mΩ | |||

| LO(VDD2) | Inductor | 2.2 | µH | ||||

| DCRL | LO inductor dc resistor | 125 | mΩ | ||||

| VIO SMPS | |||||||

| CI(VCCIO) | Input capacitor | X5R or X7R dielectric | 10 | µF | |||

| CO(VIO) | Output filter capacitor | X5R or X7R dielectric | 4 | 10 | 12 | µF | |

| CO filter capacitor ESR | f = 3 MHz | 10 | 300 | mΩ | |||

| LO(VIO) | Inductor | 2.2 | µH | ||||

| DCRL | LO inductor dc resistor | 125 | mΩ | ||||

| LDO1 | |||||||

| CI(VCC6) | Input capacitor | X5R or X7R dielectric | 4.7 | µF | |||

| CO(LDO1) | Output filtering capacitor | 0.8 | 2.2 | 2.64 | µF | ||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| LDO2 | |||||||

| CO(LDO2) | Output filtering capacitor | 0.8 | 2.2 | 2.64 | µF | ||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| LDO3 | |||||||

| CI(VCC5) | Input capacitor | X5R or X7R dielectric | 4.7 | µF | |||

| CO(LDO3) | Output filtering capacitor | 0.8 | 2.2 | 2.64 | µF | ||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| LDO4 | |||||||

| CO(LDO4) | Output filtering capacitor | 0.8 | 2.2 | 2.64 | µF | ||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| LDO5 | |||||||

| CI(VCC4) | Input capacitor | X5R or X7R dielectric | 4.7 | µF | |||

| CO(LDO5) | Output filtering capacitor | VOUT(LDOx) > 1.2 V | 0.8 | 2.2 | 2.64 | µF | |

| VOUT(LDOx) ≤ 1.2 V | 0.8 | 2 | 2.2 | ||||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| LDO6 | |||||||

| CI(VCC3) | Input capacitor | X5R or X7R dielectric | 4.7 | µF | |||

| CO(LDO6) | Output filtering capacitor | VOUT(LDOx) > 1.2 V | 0.8 | 2.2 | 2.64 | µF | |

| VOUT(LDOx) ≤ 1.2 V | 0.8 | 2 | 2.2 | ||||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| LDO7 | |||||||

| CO(LDO7) | Output filtering capacitor | VOUT(LDOx) > 1.2 V | 0.8 | 2.2 | 2.64 | µF | |

| VOUT(LDOx) ≤ 1.2 V | 0.8 | 2 | 2.2 | ||||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| LDO8 | |||||||

| CI(VCC8) | Input capacitor | X5R or X7R dielectric | 4.7 | µF | |||

| CO(LDO8) | Output filtering capacitor | VOUT(LDOx) > 1.2 V | 0.8 | 2.2 | 2.64 | µF | |

| VOUT(LDOx) ≤ 1.2 V | 0.8 | 2 | 2.2 | ||||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

| VRTC LDO | |||||||

| CI(VCC7) | Input capacitor | X5R or X7R dielectric | 4.7 | µF | |||

| CO(VRTC) | Output filtering capacitor | 0.8 | 2.2 | 2.64 | µF | ||

| CO filtering capacitor ESR | 0 | 500 | mΩ | ||||

7.6 I/O Pullup and Pulldown Characteristics

over operating free-air temperature range (unless otherwise noted) (1)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| GPIO0-8 external pullup resistor | Connected to VDDIO | –20% | 120 | 20% | kΩ | ||

| GPIO0-8 programmable pulldown (default active except GPIO0) | at 1.8 V, VRTC = 1.8 V, OFF state | 2 | 4.5 | 15 | µA | ||

| SDA_SDI, SCL_SCK, SDASR_EN2, SCLSR_EN1 external pullup resistor | Connected to VDDIO | 1.2 | kΩ | ||||

| SDA_SDI, SCL_SCK, SDASR_EN2, SCLSR_EN1 programmable pullup (DFT, default inactive) | Grounded, VDDIO = 1.8 V | –45% | 8 | 45% | kΩ | ||

| SLEEP, PWRHOLD, programmable pulldown (default active) | at 1.8 V, VRTC = 1.8 V; TA = 25°C for PWRHOLD | 2 | 4.5 | 10 | µA | ||

| NRESPWRON, NRESPWRON2 pulldown | at 1.8 V, VCC7 = 5.5 V, OFF state | 2 | 4.5 | 10 | µA | ||

| 32KCLKOUT pulldown (disabled in ACTIVE-SLEEP state) | at 1.8 V, VRTC = 1.8 V, OFF state | 2 | 4.5 | 10 | µA | ||

| PWRON programmable pullup (default active) | Grounded, VCC7 = 5.5 V | –43 | –31 | –15 | µA | ||

| HDRST programmable pulldown (default active) | at 1.8 V, VRTC = 1.8 V | 2 | 4.5 | 10 | µA | ||

7.7 Digital I/O Voltage Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)| PARAMETER | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|

| RELATED I/O: PWRON |

|||||||

| VIL | Low-level input voltage | 0.3 x VBAT | V | ||||

| VIH | High-level input voltage | 0.7 x VBAT | V | ||||

| RELATED I/O: PWRHOLD, GPIO0-8, PWRDN |

|||||||

| VIL | Low-level input voltage | 0.45 | V | ||||

| VIH | High-level input voltage | 1.3 | VBAT | V | |||

| RELATED I/O: BOOT1 |

|||||||

| Low level input – Impedance between BOOT1 and GND | 10 | kΩ | |||||

| High level input – Impedance between BOOT1 and VRTC | 10 | kΩ | |||||

| Hi-Z level input – Impedance between BOOT1 and GND | 500 | kΩ | |||||

| RELATED I/O: SLEEP |

|||||||

| VIL | Low-level input voltage | 0.35 x VDDIO | V | ||||

| VIH | High-level input voltage | 0.65 x VDDIO | V | ||||

| RELATED I/O: HDRST |

|||||||

| VIL | Low-level input voltage | 0.35 x VRTC | V | ||||

| VIH | High-level input voltage | 0.65 x VRTC | V | ||||

| RELATED I/O: NRESPWRON, INT1, 32KCLKOUT |

|||||||

| VOL | Low-level output voltage | IOL = 100 µA | 0.2 | V | |||

| IOL = 2 mA | 0.45 | V | |||||

| VOH | High-level output voltage | IOH = 100 µA | VDDIO – 0.2 | V | |||

| IOH = 2 mA | VDDIO – 0.45 | V | |||||

| Related I/O: EN |

|||||||

| VOL | Low-level output voltage | IOL = 100 µA | 0.2 | V | |||

| IOL = 2 mA | 0.9 | V | |||||

| VOH | High-level output voltage | IOH = 100 µA | VCC7– 0.2 | V | |||

| IOH = 2 mA | VCC7 – 0.45 | V | |||||

| RELATED I/O: GPIO0 (PUSH-PULL MODE) |

|||||||

| VOL | Low-level output voltage | IOL = 100 µA | 0.2 | V | |||

| IOL = 2 mA | 0.45 | V | |||||

| VOH | High-level output voltage | IOH = 100 µA | VCC7 – 0.2 | V | |||

| IOH = 2 mA | VCC7 – 0.45 | V | |||||

| RELATED OPEN-DRAIN I/O: GPIO0, GPIO2, GPIO4-8, NRESPWRON2 |

|||||||

| VOL | Low-level output voltage | IOL = 100 µA | 0.2 | V | |||

| IOL = 2 mA | 0.45 | V | |||||

| RELATED OPEN-DRAIN I/O: GPIO1, GPIO3 |

|||||||

| VOL | Low-level output voltage | IOL = 100 µA | 0.2 | V | |||

| IOL = 2 mA | 0.4 | V | |||||

| I | |||||||

| VIL | Low-level input voltage | –0.5 | 0.3 x VDDIO | V | |||

| VIH | High-level input voltage | 0.7 x VDDIO | V | ||||

| Hysteresis | 0.1 x VDDIO | V | |||||

| VOL | Low-level output voltage at 3 mA (sink current), VDDIO = 1.8 V | 0.2 × VDDIO | V | ||||

| VOL | Low-level output voltage at 3 mA (sink current), VDDIO = 3.3 V | 0.4 x VDDIO | V | ||||

7.8 I2C Interface and Control Signals

over operating free-air temperature range (unless otherwise noted)| NO. | PARAMETER | TEST CONDITIONS(1) (2) | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|---|

| GENERAL REQUIREMENTS | |||||||

| INT1 rise and fall times | CL = 5 to 35 pF | 5 | 10 | ns | |||

| NRESPWRON rise and fall times | CL = 5 to 35 pF | 5 | 10 | ns | |||

| SLAVE HIGH-SPEED MODE | |||||||

| SCL/EN1 and SDA/EN2 rise and fall time | CL = 10 to 100 pF | 10 | 80 | ns | |||

| Data rate | 3.4 | Mbps | |||||

| I3 | tsu(SDA-SCLH) | Setup time, SDA valid to SCL high | 10 | ns | |||

| I4 | th(SCLL-SDA) | Hold time, SDA valid from SCL low | 0 | 70 | ns | ||

| I7 | tsu(SCLH-SDAL) | Setup time, SCL high to SDA low | 160 | ns | |||

| I8 | th(SDAL-SCLL) | Hold time, SCL low from SDA low | 160 | ns | |||

| I9 | tsu(SDAH-SCLH) | Setup time, SDA high to SCL high | 160 | ns | |||

| SLAVE FAST MODE |

|||||||

| SCL/EN1 and SDA/EN2 rise and fall time | CL = 10 to 400 pF | 20 + 0.1 × CL |

250 | ns | |||

| Data rate | 400 | Kbps | |||||

| I3 | tsu(SDA-SCLH) | Setup time, SDA valid to SCL high | 100 | ns | |||

| I4 | th(SCLL-SDA) | Hold time, SDA valid from SCL low | 0 | 0.9 | µs | ||

| I7 | tsu(SCLH-SDAL) | Setup time, SCL high to SDA low | 0.6 | µs | |||

| I8 | th(SDAL-SCLL) | Hold time, SCL low from SDA low | 0.6 | µs | |||

| I9 | tsu(SDAH-SCLH) | Setup time, SDA high to SCL high | 0.6 | µs | |||

| SLAVE STANDARD MODE | |||||||

| SCL/EN1 and SDA/EN2 rise and fall time | CL = 10 to 400 pF | 250 | ns | ||||

| Data rate | 100 | Kbps | |||||

| I3 | tsu(SDA-SCLH) | Setup time, SDA valid to SCL high | 250 | ns | |||

| I4 | th(SCLL-SDA) | Hold time, SDA valid from SCL low | 0 | µs | |||

| I7 | tsu(SCLH-SDAL) | Setup time, SCL high to SDA low | 4.7 | µs | |||

| I8 | th(SDAL-SCLL) | Hold time, SCL low from SDA low | 4 | µs | |||

| I9 | tsu(SDAH-SCLH) | Setup time, SDA high to SCL high | 4 | µs | |||

7.9 Switching Characteristics—I2C Interface and Control Signals

over operating free-air temperature range (unless otherwise noted)| NO. | PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|---|

| SLAVE HIGH-SPEED MODE | |||||||

| I1 | tw(SCLL) | Pulse duration, SCL low | 160 | ns | |||

| I2 | tw(SCLH) | Pulse duration, SCL high | 60 | ns | |||

| SLAVE FAST MODE | |||||||

| I1 | tw(SCLL) | Pulse duration, SCL low | 1.3 | µs | |||

| I2 | tw(SCLH) | Pulse duration, SCL high | 0.6 | µs | |||

| SLAVE STANDARD MODE | |||||||

| I1 | tw(SCLL) | Pulse duration, SCL low | 4.7 | µs | |||

| I2 | tw(SCLH) | Pulse duration, SCL high | 4 | µs | |||

7.10 Power Consumption

over operating free-air temperature range (unless otherwise noted)All current consumption measurements are relative to the FULL chip, all VCC inputs set to VBAT voltage, COMP2 is off.

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| Device OFF state | VBAT = 5 V, XTAL oscillator running | 2.5 | mA | ||||

| VBAT = 5 V, Bypass clock used | 22 | µA | |||||

| Device SLEEP state | VBAT = 5 V, 3 DCDCs on in PFM mode, 5 LDOs on, no load, XTAL oscillator running | 2.8 | mA | ||||

| Device ACTIVE state | VBAT = 5 V, 3 DCDCs on in PWM mode, 5 LDOs on, no load, XTAL oscillator running | 26.6 | mA | ||||

7.11 Power References and Thresholds

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| Output reference voltage (VREF pin) | Device in active or low-power mode | –1% | 0.85 | 1% | V | ||

| Main battery not present falling threshold VBNPR | Measured on pin VCC7, falling (Triggering monitored on pin VRTC) |

1.8 | 2.1 | 2.3 | V | ||

| PORXTAL | The POR threshold for rising VCC7 voltages | 3.58 | 3.77 | 3.96 | V | ||

| The POR threshold for falling VCC7 voltages | 3.50 | 3.68 | 3.87 | V | |||

| Difference between rising and falling thresholds | 62.55 | 89.35 | 200 | mV | |||

7.12 Thermal Monitoring and Shutdown

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| Hot-die temperature rising threshold | THERM_HDSEL[1:0] = 00 | 117 | °C | ||||

| THERM_HDSEL[1:0] = 01 | 121 | ||||||

| THERM_HDSEL[1:0] = 10 | 113 | 125 | 136 | ||||

| THERM_HDSEL[1:0] = 11 | 130 | ||||||

| Hot-die temperature hysteresis | 10 | °C | |||||

| Thermal shutdown temperature rising threshold | 150 | 165 | 180 | °C | |||

| Thermal shutdown temperature recovery threshold | THERM_HDSEL[1:0] = 00 | 107 | °C | ||||

| THERM_HDSEL[1:0] = 01 | 111 | ||||||

| THERM_HDSEL[1:0] = 10 | 115 | ||||||

| THERM_HDSEL[1:0] = 11 | 120 | ||||||

| Ground current | Device in ACTIVE state, Temp = 27°C, VCC7 = 3.8 V | 6 | µA | ||||

7.13 32-kHz RTC Clock

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| GENERAL CLK32KOUT REQUIREMENTS |

|||||||

| CLK32KOUT rise and fall time | CL = 35 pF | 10 | ns | ||||

| EXTERNAL CLOCK (OSC16MIN GROUNDED, OSC16MOUT FLOATING, AND OSCEXT32K INPUT) |

|||||||

| Input bypass clock frequency | OSCKIN input | 32 | kHz | ||||

| Input bypass clock duty cycle | OSCKIN input | 40% | 60% | ||||

| Input bypass clock rise and fall time | 10% – 90%, OSCEXT32K input | 10 | 20 | ns | |||

| CLK32KOUT duty cycle | Logic output signal | 40% | 60% | ||||

| Bypass clock setup time | 32KCLKOUT output | 1 | ms | ||||

| Ground current | Bypass mode | 1.5 | µA | ||||

| CRYSTAL OSCILLATOR (CRYSTAL BETWEEN OSC16MIN AND OSC16MOUT, OSCEXT32K GROUNDED) |

|||||||

| Crystal frequency | at specified load cap value | 16.384 | MHz | ||||

| Crystal tolerance | at 27°C | –20 | 0 | 20 | ppm | ||

| Oscillator frequency drift | TJ from –40°C to 125°C, VCC7 from 4 V to 5.5 V; excluding crystal drift | –50 | 50 | ppm | |||

| Max crystal series resistor | at fundamental frequency | 90 | Ω | ||||

| Oscillator startup time | Power on until first time slot | 13.2 | ms | ||||

| Drive level power | Steady state operation | 15 | 120 | µW | |||

| Ground current | 2.5 | mA | |||||

| Overall frequency tolerance | CLK32KOUT output | –1% | 1% | ||||

| Output frequency | CLK32KOUT output | 32.768 | kHz | ||||

| Crystal motional inductance | According to crystal data sheet | 23 | 33 | 43 | µH | ||

| Crystal shunt capacitance | According to crystal data sheet | 0.5 | 4 | pF | |||

| Crystal load capacitance | According to crystal data sheet; including PCB parasitic capacitance |

9 | 10 | 11 | pF | ||

| RC OSCILLATOR (OSC16MIN AND OSCEXT32K GROUNDED, OSC16MOUT FLOATING) |

|||||||

| Output frequency | CK32KOUT output | 32 | kHz | ||||

| Output frequency accuracy | at 25°C | –15% | 0 | 15% | |||

| Cycle jitter (RMS) | Oscillator contribution | 10% | |||||

| Output duty cycle | 40% | 50% | 60% | ||||

| Settling time | 150 | µs | |||||

| Ground current | Active at fundamental frequency | 4 | µA | ||||

7.14 VRTC LDO

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| Input voltage VIN | On mode | 2.5 | 5.5 | V | |||

| Backup mode | 1.9 | 3 | |||||

| DC output voltage VOUT | On mode, 3 V < VIN < 5.5 V | 1.78 | 1.83 | 1.9 | V | ||

| Backup mode, 2.3 V ≤ VIN ≤ 2.6 V | 1.72 | 1.78 | 1.9 | ||||

| Rated output current IOUTmax | On mode | 20 | mA | ||||

| Backup mode | 0.1 | ||||||

| DC load regulation | On mode, IOUT = IOUTmax to 0 | 100 | mV | ||||

| Backup mode, IOUT = IOUTmax to 0 | 100 | ||||||

| DC line regulation | On mode, VIN = 3 V to VINmax at IOUT = IOUTmax | 2.5 | mV | ||||

| Backup mode, VIN = 2.3 V to 5.5 V at IOUT = IOUTmax | 100 | ||||||

| Transient load regulation | On mode, VIN = VINmin + 0.2 V to VINmax

IOUT = IOUTmax/2 to IOUTmax in 5 µs and IOUT = IOUTmax to IOUTmax / 2 in 5 µs |

50 (1) | mV | ||||

| Transient line regulation | On mode, VIN = VINmin + 0.5 V to VINmin in 30 µs and VIN = VINmin to VINmin + 0.5 V in 30 µs, IOUT = IOUTmax / 2 |

25 (1) | mV | ||||

| Turn-on time | IOUT = 0, VIN rising from 0 up to 3.6 V, at VOUT = 0.1 V up to VOUTmin | 2.2 | ms | ||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+ = VINmin + 0.1 V to VINmax at IOUT = IOUTmax / 2 |

f = 217 Hz | 55 | dB | |||

| f = 50 kHz | 35 | ||||||

| Ground current | Device in ACTIVE state | 23 | µA | ||||

| Device in BACKUP or OFF state | 3 | ||||||

7.15 VIO SMPS

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| Input voltage (VCCIO and VCC7) VIN | VOUT = 1.5 V, 1.8 V, 2.5 or 3.3 V | 4 | 5.5 | V | ||||

| DC output voltage (VOUT) | PWM mode (VIO_PSKIP = 0) IOUT = 0 | VSEL = 00 | –1.5% | 1.5 | 3% | V | ||

| VSEL = 01 | –1.5% | 1.8 | 3% | |||||

| VSEL = 10 | –1.5% | 2.5 | 3% | |||||

| VSEL = 11 | –1.5% | 3.3 | 3% | |||||

| Power down | 0 | |||||||

| Rated output current IOUTmax | TPS659119xAIPFPRQ1 | 1500 | mA | |||||

| P-channel MOSFET | VIN = VINmin | 300 | mΩ | |||||

| On-resistance RDS(ON)_PMOS | VIN = 4 V | 250 | 400 | |||||

| P-channel leakage current ILK_PMOS | VIN = VINMAX, SWIO = 0 V | 2 | µA | |||||

| N-channel MOSFET | VIN = VMIN | 300 | mΩ | |||||

| On-resistance RDS(ON)_NMOS | VIN = 4 V | 250 | 400 | |||||

| N-channel leakage current ILK_NMOS | VIN = VINmax, SWIO = VINmax | 2 | µA | |||||

| PMOS and NMOS current limit (high side and low side) TPS659119xAIPFPRQ1 | VIN = VINmin to VINmax source current load; when ILIM[1:0] = 00 | 700 | mA | |||||

| when ILIM[1:0] = 01 | 1200 | mA | ||||||

| when ILIM[1:0] = 10 | 1700 | mA | ||||||

| when ILIM[1:0] = 11 | > 1700 | mA | ||||||

| DC load regulation | On mode, IOUT = 0 to IOUTmax | 60 | mV/A | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax

at IOUT = 0 |

30 | mV | |||||

| Transient load regulation | VOUT = 1.8 V IOUT = 0 to 500 mA , Max slew = 100 mA/µs IOUT = 700 to 1200 mA , Max slew = 100 mA/µs |

50 | mV | |||||

| ton, off to on | IOUT = 200 mA | 350 | µs | |||||

| Overshoot | SMPS turned on | 3% | ||||||

| Power-save mode ripple voltage | PFM (pulse skip mode) mode, IOUT = 1 mA | 0.025 × VOUT | VPP | |||||

| Switching frequency | 2.7 | 3 | 3.3 | MHz | ||||

| Duty cycle | 100% | |||||||

| Minimum on time TON(MIN) P-channel MOSFET | 35 | ns | ||||||

| VFBIO internal resistance | 0.5 | 1 | MΩ | |||||

| Ground current (IQ) | Off | 1 | µA | |||||

| PWM mode, IOUT = 0 mA, VIN = 3.8 V, VIO_PSKIP = 0 | 7500 | |||||||

| PFM (pulse skipping) mode, no switching, 3-MHz clock on | 250 | |||||||

| Low-power (pulse skipping) mode, no switching | ST[1:0] = 11 | 63 | ||||||

| Conversion efficiency | PWM mode, DCRL < 50 mΩ, VOUT = 1.8 V, VIN = 3.6 V: | IOUT = 10 mA | 40% | |||||

| IOUT = 100 mA | 83% | |||||||

| IOUT = 400 mA | 85% | |||||||

| IOUT = 600 mA | 80% | |||||||

| PFM mode, DCRL < 50 mΩ, VOUT = 1.8 V, VIN = 3.6 V: | IOUT = 1 mA | 68% | ||||||

| IOUT = 10 mA | 80% | |||||||

| IOUT = 400 mA | 85% | |||||||

7.16 VDD1 SMPS

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| Input voltage (VCC1 and VCC7) VIN | VOUT ≤ 2.7 V | 4 | 5.5 | V | ||||

| VOUT > 2.7 V | 4 | 5.5 | ||||||

| DC output voltage (VOUT) | IOUT = 0 mA, PWM; VIN = 4 V to 5.5 V; VOUT > 1 V; ON MODE: | –1.5% | 3% | V | ||||

| DC output voltage programmable step (VOUTSTEP) | VGAIN_SEL = 00, 72 steps | 12.5 | mV | |||||

| Rated output current IOUTmax | 1500 | mA | ||||||

| P-channel MOSFET on-resistance RDS(ON)_PMOS | VIN = 4 V | 250 | 400 | mΩ | ||||

| P-channel leakage current ILK_PMOS | VIN = VINmax, SW1 = 0 V | 2 | µA | |||||

| N-channel MOSFET on-resistance RDS(ON)_NMOS | VIN = 4 V | 250 | 400 | mΩ | ||||

| N-channel leakage current ILK_NMOS | VIN = VINmax, SW1 = VINmax | 2 | µA | |||||

| PMOS current limit (high side) | VIN = VINmin to VINmax | 1700 | mA | |||||

| NMOS current limit (low side) | VIN = VINmin to VINmax, source current load | 1700 | mA | |||||

| VIN = VINmin to VINmax, sink current load | 1700 | |||||||

| DC load regulation | On mode, IOUT = 0 to IOUTmax | 60 | mV/A | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax

at IOUT = 0 |

30 | mV | |||||

| Transient load regulation | VOUT = 1.2 V IOUT = 0 to 500 mA , Max slew = 100 mA/µs IOUT = 700 mA to 1.2 A , Max slew = 100 mA/µs |

50 | mV | |||||

| ton, off to on | IOUT = 200 mA | 350 | µs | |||||

| Output voltage transition rate | From VOUT = 0.6 V to 1.5 V and VOUT = 1.5 V to 0.6 V IOUT = 500 mA | TSTEP[2:0] = 001 | 12.5 | mV/µs | ||||

| TSTEP[2:0] = 011 (default) | 7.5 | |||||||

| TSTEP[2:0] = 111 | 2.5 | |||||||

| Overshoot | SMPS turned on | 3% | ||||||

| Power-save mode ripple voltage | PFM (pulse skip mode), IOUT = 1 mA | 0.025 × VOUT | VPP | |||||

| Switching frequency | 2.7 | 3 | 3.3 | MHz | ||||

| Duty cycle | 100% | |||||||

| Minimum on time tON(MIN) P-channel MOSFET | 35 | ns | ||||||

| VFB1 internal resistance | 0.5 | 1 | MΩ | |||||

| Ground current (IQ) | Off | 1 | µA | |||||

| PWM mode, IOUT = 0 mA, VIN = 3.8 V, VDD1_PSKIP = 0 | 7500 | |||||||

| Pulse skipping mode, no switching | 78 | |||||||

| Low-power (pulse skipping) mode, no switching | ST[1:0] = 11 | 63 | ||||||

| Conversion efficiency | PWM mode, DCRL < 0.1 Ω, VOUT = 1.2 V, VIN = 4 V: | IOUT = 10 mA | 35% | |||||

| IOUT = 100 mA | 78% | |||||||

| IOUT = 400 mA | 80% | |||||||

| IOUT = 800 mA | 74% | |||||||

| IOUT = 1500 mA | 62% | |||||||

| PFM mode, DCRL < 0.1 Ω, VOUT = 1.2 V, VIN = 4 V: | IOUT = 1 mA | 59% | ||||||

| IOUT = 10 mA | 70% | |||||||

| IOUT = 400 mA | 80% | |||||||

7.17 VDD2 SMPS

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| Input voltage (VCC2 and VCC7) VIN | VOUT ≤ 2.7 V | 4 | 5.5 | V | ||||

| VOUT > 2.7 V | 4 | 5.5 | ||||||

| DC output voltage (VOUT) | VOUT = 0 mA, PWM; VIN = 4 V to 5.5 V; VOUT > 1 V; ON MODE: | –1.5% | 3% | V | ||||

| DC output voltage programmable step (VOUTSTEP) | VGAIN_SEL = 00, 72 steps | 12.5 | mV | |||||

| Rated output current IOUTmax | 1500 | mA | ||||||

| P-channel MOSFET on-resistance RDS(ON)_PMOS | VIN = 4 V | 250 | 400 | mΩ | ||||

| P-channel leakage current ILK_PMOS | VIN = VINmax, SW2 = 0 V | 2 | µA | |||||

| N-channel MOSFET on-resistance RDS(ON)_NMOS | VIN = 4 V | 250 | 400 | mΩ | ||||

| N-channel leakage current ILK_NMOS | VIN = VINmax, SW2 = VINmax | 2 | µA | |||||

| PMOS current limit (high side) | VIN = VINmin to VINmax, source current load | 1700 | mA | |||||

| NMOS current limit (low side) | VIN = VINmin to VINmax, source current load | 1700 | mA | |||||

| VIN = VINmin to VINmax, sink current load | 1700 | |||||||

| DC load regulation | On mode, IOUT = 0 to IOUTmax | 60 | mV/A | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = 0 | 30 | mV | |||||

| Transient load regulation | VOUT = 1.2 V IOUT = 0 to 500 mA , Max slew = 100 mA/µs IOUT = 700 mA to 1.2 A , Max slew = 100 mA/µs |

50 | mV | |||||

| ton, Off to on | IOUT = 200 mA | 350 | µs | |||||

| Output voltage transition rate | From VOUT = 0.6 V to 1.5 V and VOUT = 1.5 V to 0.6 V IOUT = 500 mA | TSTEP[2:0] = 001 | 12.5 | mV/µs | ||||

| TSTEP[2:0] = 011 (default) | 7.5 | |||||||

| TSTEP[2:0] = 111 | 2.5 | |||||||

| Overshoot | SMPS turned on | 3% | ||||||

| Power-save mode ripple voltage | PFM (pulse skip mode), IOUT = 1 mA | 0.025 × VOUT | VPP | |||||

| Switching frequency | 2.7 | 3 | 3.3 | MHz | ||||

| Duty cycle | 100% | |||||||

| Minimum on time | 35 | ns | ||||||

| P-Channel MOSFET | ||||||||

| VFB2 internal resistance | 0.5 | 1 | MΩ | |||||

| Ground current (IQ) | Off | 1 | µA | |||||

| PWM mode, IOUT = 0 mA, VIN = 3.8 V, VDD2_PSKIP = 0 | 7500 | |||||||

| PFM (pulse skipping) mode, no switching | 78 | |||||||

| Low-power (pulse skipping) mode, no switching | ST[1:0] = 11 | 63 | ||||||

| Conversion efficiency | PWM mode, DCRL < 50 mΩ, VOUT = 1.2 V, VIN = 4 V: | IOUT = 10 mA | 35% | |||||

| IOUT = 100 mA | 78% | |||||||

| IOUT = 400 mA | 80% | |||||||

| IOUT = 800 mA | 74% | |||||||

| IOUT = 1200 mA | 66% | |||||||

| IOUT = 1500 mA | 62% | |||||||

| PFM mode, DCRL < 50 mΩ, VOUT = 1.2 V, VIN = 4 V: | IOUT = 1 mA | 59% | ||||||

| IOUT = 10 mA | 70% | |||||||

| IOUT = 400 mA | 80% | |||||||

| PWM mode, DCRL < 50 mΩ, VOUT = 3.3 V, VIN = 5 V: | IOUT = 10 mA | 39% | ||||||

| IOUT = 100 mA | 85% | |||||||

| IOUT = 400 mA | 91% | |||||||

| IOUT = 800 mA | 90% | |||||||

| IOUT = 1200 mA | 86% | |||||||

| IOUT = 1500 mA | 84% | |||||||

| PFM mode, DCRL < 50 mΩ, VOUT = 3.3 V, VIN = 5 V: | IOUT = 1 mA | 80% | ||||||

| IOUT = 10 mA | 82% | |||||||

| IOUT = 400 mA | 92% | |||||||

7.18 EXTCTRL

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| Ratio of VSENSE to VOUT (Selectable voltage divider) | SEL[6:0] = 0 (EN signal low) | 1 | V/V | ||||

| SEL[6:0] = 1 to 3 | 1 | ||||||

| For SEL[6:0] = 3 to 67 | |||||||

| Ratio = 48 / (45 + SEL[6:0]) | |||||||

| SEL[6:0] = 4 | –0.7% | 48:49 | 0.7% | ||||

| SEL[6:0] = 5 | –0.7% | 24:25 | 0.7% | ||||

| ... | |||||||

| SEL[6:0] = 35 | –0.7% | 3:5 | 0.7% | ||||

| ... | |||||||

| SEL[6:0] = 66 | –0.7% | 16:37 | 0.7% | ||||

| SEL[6:0] = 67 to 127 | –0.7% | 3:7 | 0.7% | ||||

| Programmable voltage step size (with a 0.8 V reference) | 16.7 | mV | |||||

| Output voltage transition rate (with 0.8 V reference) | From VOUT = 0.8 V to 1.87 V and VOUT = 1.87 V to 0.8 V | 100(1) | mV / 20 µs | ||||

7.19 LDO1 AND LDO2

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| GENERAL LDO1 AND LDO2 CHARACTERISTICS |

||||||||

| VIN | Input voltage (VCC6) | VOUT(LDO1) = 1.05 V at 320 mA and VOUT(LDO2) = 1.05 V at 160 mA | 1.4 | 3.6 | V | |||

| VOUT(LDO1) = 1.2 V / 1.5 V at 100 mA and VOUT(LDO2) = 1.2 V / 1.1 V / 1 V | 1.7 | 3.6 | ||||||

| VOUT(LDO1) = 1.5 V and VOUT (LDO1, LDO2) = 1.8 V at 200 mA | 2.1 | 3.6 | ||||||

| VOUT(LDO1) = 1.8 V and VOUT(LDO2) = 1.8 V | 2.7 | 3.6 | ||||||

| VOUT(LDO1) = 2.7 V | 3.2 | 3.6 | ||||||

| VOUT (LDO1) = VOUT(LDO2) = 3.3 V | 3.5 | 3.6 | ||||||

| LDO1 | ||||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | 1 | 3.3 | V | |||

| Step size | 50 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 320 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 330 | 600 | 1000 | mA | |||

| VDO | Dropout voltage | ON mode, VDO = VIN – VOUT, VIN = 1.4 V, IOUT = IOUTmax |

350 | mV | ||||

| DC load regulation | On mode, IOUT = IOUTmax | 17 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = IOUTmax | 1 | mV | |||||

| Transient load regulation | ON mode, VIN = 1.5 V, VOUT = 1.05 V IOUT = 0.1 × IOUTmax to 0.9 × IOUTmax in 5 µs and IOUT = 0.9 × IOUTmax to 0.1 × IOUTmax in 5 µs |

20 | mV | |||||

| Transient line regulation | On mode, VIN = 2.7 + 0.5 V to 2.7 in 30 µs, and VIN = 2.7 to 2.7 + 0.5 V in 30 µs, IOUT = IOUTmax |

5 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 50 | 75 | 100 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 200 | 300 | 420 | |||||

| Turn-on inrush current | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | 300 | 600 | mA | ||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+= 1.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 20 kHz | 40 | |||||||

| LDO1 internal resistance | LDO off | 600 | Ω | |||||

| Ground current | On mode, IOUT = 0 | 63 | 75 | µA | ||||

| On mode, IOUT = IOUTmax | 2000 | |||||||

| Low-power mode | 22 | 20 | ||||||

| Off mode (max 85°C) | 2.7 | |||||||

| LDO2 | ||||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | 1 | 3.3 | V | |||

| Step size | 50 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 320 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 330 | 600 | 1000 | mA | |||

| VDO | Dropout voltage | ON mode, VDO = VIN – VOUT, VIN = 1.4 V, IOUT = IOUTmax |

350 | mV | ||||

| DC load regulation | On mode, IOUT = IOUTmax | 17 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = IOUTmax | 1 | mV | |||||

| Transient load regulation | ON mode, VIN = 1.5 V, VOUT = 1.05 V IOUT = 0.1 × IOUTmax to 0.9 × IOUTmax in 5 µs and IOUT = 0.9 × IOUTmax to 0.1 × IOUTmax in 5 µs |

20 | mV | |||||

| Transient line regulation | On mode, VIN = 2.7 + 0.5 V to 2.7 in 30 µs, and VIN = 2.7 to 2.7 + 0.5 V in 30 µs, IOUT = IOUTmax |

5 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 40 | 75 | 100 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 200 | 300 | 420 | |||||

| Turn-on inrush current | 300 | 600 | mA | |||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+= 1.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 20 kHz | 40 | |||||||

| LDO2 internal resistance | LDO off | 600 | Ω | |||||

| Ground current | On mode, IOUT = 0 | 63 | 75 | µA | ||||

| On mode, IOUT = IOUTmax | 2000 | |||||||

| Low-power mode | 22 | 20 | ||||||

| Off mode (max 85°C) | 2.7 | |||||||

7.20 LDO3 and LDO4

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| GENERAL LDO3 AND LDO4 CHARACTERISTICS | ||||||||

| VIN | Input voltage (VCC5) | VOUT (LDO3) = 1.8 V and VOUT (LDO4) = 1.8 V / 1.1 V / 1 V | 2.7 | 5.5 | V | |||

| VOUT (LDO3) = 2.6 V and VOUT (LDO4) = 2.5 V | 3 | 5.5 | ||||||

| VOUT (LDO3) = 2.8 V | 3.2 | 5.5 | ||||||

| LDO3 | ||||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | 1 | 3.3 | V | |||

| Step size | 100 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 200 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 330 | 550 | 650 | mA | |||

| VDO | Dropout voltage | On mode, VOUTtyp = 3.3 V, VDO = VIN – VOUT, VIN = 3.3 V, IOUT = IOUTmax |

150 | 270 | mV | |||

| DC load regulation | On mode, IOUT = IOUTmax | 28 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = IOUTmax | 1 | mV | |||||

| Transient load regulation | On mode, VIN = 2.7 V, VOUTtyp = 1.8 V IOUT = 0.1 × IOUTmax to 0.9 × IOUTmax in 5 µs and IOUT = 0.9 × IOUTmax to 0.1 × IOUTmax in 5 µs |

15 | mV | |||||

| Transient line regulation | On mode, VOUTtyp = 1.8 V, IOUT = IOUTmax,VIN = VINmin + 0.5 V to VINmin in 30 µs and VIN = VINmin to VINmin + 0.5 V in 30 µs, IOUT = IOUTmax |

0.5 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 25 | 50 | 70 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 120 | 180 | 230 | |||||

| Turn-on inrush current | 200 | 450 | mA | |||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+ = 3.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 50 kHz | 40 | |||||||

| LDO3 internal resistance | LDO off | 500 | kΩ | |||||

| Ground current | On mode, IOUT = 0 | 65 | 76 | µA | ||||

| On mode, IOUT = IOUTmax | 2000 | |||||||

| Low-power mode | 14 | 22 | ||||||

| Off mode | 1 | |||||||

| LDO4 | ||||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | 1 | 3.3 | V | |||

| Step size | 100 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA, | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 50 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 200 | 400 | 500 | mA | |||

| VDO | Dropout voltage | On mode, VOUTtyp = 3.3 V, VDO = VIN – VOUT

VIN = 3.3 V, IOUT = IOUTmax |

100 | 160 | mV | |||

| DC load regulation | On mode, IOUT = IOUTmax | 6 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = IOUTmax | 1 | mV | |||||

| Transient load regulation | On mode, VIN = 2.7 V, VOUTtyp = 1.8 V IOUT = 0.1 × IOUTmax to 0.9 × IOUTmax in 5 µs and IOUT = 0.9 × IOUTmax to 0.1 × IOUTmax in 5 µs |

6 | mV | |||||

| Transient line regulation | On mode, VIN = VINmin + 0.5 V to VINmin in 30 µs and VIN = VINmin to VINmin + 0.5 V in 30 µs, IOUT = IOUTmax / 2 |

0.2 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 25 | 50 | 70 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 120 | 180 | 230 | |||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+= 3.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 50 kHz | 40 | |||||||

| LDO4 internal resistance | LDO Off | 500 | kΩ | |||||

| Ground current | On mode, IOUT = 0 | 55 | 65 | µA | ||||

| On mode, IOUT = IOUTmax | 900 | |||||||

| Low-power mode | 14 | 17 | ||||||

| Off mode | 1 | |||||||

7.21 LDO5

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| GENERAL CHARACTERISTICS | ||||||||

| VIN | Input voltage (VCC4) | VOUT (LDO5) ≤ 1.2 V | 1.7 | 1.9 | V | |||

| VOUT (LDO5) > 1.2 V (See Dropout Voltage parameter for additional constraints) | 1.7 | 5.5 | ||||||

| VOUT (LDO5) = 2.5 V | 3.2 | 5.5 | ||||||

| VOUT (LDO5) = 2.8 V at Iload = 200 mA | 3.2 | 5.5 | ||||||

| LDO5 | ||||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | 1 | 3.3 | V | |||

| Step size | 100 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 300 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 330 | 550 | 650 | mA | |||

| VDO | Dropout voltage | On mode, VDO = VIN – VOUT | VIN = 2.7 V, IOUT = IOUTmax |

500 | mV | |||

| VIN = 2.7 V, IOUT = 250 mA |

400 | |||||||

| VIN = 2.7 V, IOUT = 200 mA |

300 | |||||||

| VIN = 1.7 V, IOUT = 180 mA |

700 | |||||||

| VIN = 1.7 V, IOUT = 150 mA |

500 | |||||||

| VIN = 1.7 V, IOUT = 100 mA |

300 | |||||||

| DC load regulation | On mode, IOUT = IOUTmax | 16 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUTmax | 1 | mV | |||||

| Transient load regulation | On mode, VIN = 3.2 V, VOUTtyp = 2.8 V IOUT = 0.1 × IOUTmax to 0.9 × IOUTmax in 5 µs and IOUT = 0.9 × IOUTmax to 0.1 × IOUTmax in 5 µs |

16 | mV | |||||

| Transient line regulation | On mode, VIN = VINmin + 0.5 V to VINmin in 30 µs and VIN = VINmin to VINmin + 0.5 V in 30 µs, IOUT = IOUTmax |

4 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 20 | 50 | 70 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 120 | 180 | 250 | |||||

| Turn-on inrush current | 200 | 450 | mA | |||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+ = 3.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 20 kHz | 40 | |||||||

| LDO5 internal resistance | LDO Off | 60 | Ω | |||||

| Ground current | On mode, IOUT = 0 | 65 | 76 | µA | ||||

| On mode, IOUT = IOUTmax | 2000 | |||||||

| Low-power mode | 14 | 22 | ||||||

| Off mode | 1 | |||||||

7.22 LDO6 and LDO7

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| GENERAL LDO6 AND LDO7 CHARACTERISTICS | ||||||||

| VIN | Input voltage (VCC3 for LDO6 & LDO7) | VOUT (LDO6/7) ≤ 1.2 V | 1.7 | 1.9 | V | |||

| VOUT (LDO6/7) > 1.2 V (See Dropout Voltage parameter for additional constraints) | 1.7 | 5.5 | ||||||

| VOUT(LDO7) = 2.8 V | 3.2 | 5.5 | ||||||

| VOUT(LDO7) = 3.3 V | 3.6 | 5.5 | ||||||

| VOUT(LDO7) = 2.8 V at 250 mA | 3.2 | 5.5 | ||||||

| VOUT(LDO7) = 3 V | 3.6 | 5.5 | ||||||

| VOUT(LDO7) = 3.3 V at 250 mA | 3.6 | 5.5 | ||||||

| LDO6 | ||||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | 1 | 3.3 | V | |||

| Step size | 100 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 300 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 330 | 550 | 650 | mA | |||

| VDO | Dropout voltage | On mode, VDO = VIN – VOUT, | VIN = 2.7 V, IOUT = IOUTmax |

500 | mV | |||

| VIN = 2.7 V, IOUT = 250 mA |

400 | |||||||

| VIN = 2.7 V, IOUT = 200 mA |

300 | |||||||

| VIN = 1.7 V, IOUT = 180 mA |

700 | |||||||

| VIN = 1.7 V, IOUT = 150 mA |

500 | |||||||

| VIN = 1.7 V, IOUT = 100 mA |

300 | |||||||

| DC load regulation | On mode, IOUT = IOUTmin | 16 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = IOUTmax | 1 | mV | |||||

| Transient load regulation | On mode, VIN = 3.2 V, VOUTtyp = 2.8 V IOUT = 0.1 × IOUTmax to 0.9 × IOUTmax in 5 µs and IOUT = 0.9 × IOUTmax to 0.1 × IOUTmax in 5 µs |

20 | mV | |||||

| Transient line regulation | On mode, VIN = 2.7 V + 0.5 V to 2.7 V in 30 µs and VIN = 2.7 V to 2.7 V + 0.5 V in 30 µs, IOUT = IOUTmax |

5 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 20 | 50 | 70 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 120 | 180 | 250 | |||||

| Turn-on inrush current | 200 | 450 | mA | |||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+ = 3.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 20 kHz | 40 | |||||||

| LDO6 internal resistance | LDO off | 60 | Ω | |||||

| Ground current | On mode, IOUT = 0 | 65 | 76 | µA | ||||

| On mode, IOUT = IOUTmax | 2000 | |||||||

| Low-power mode | 14 | 22 | ||||||

| Off mode | 1 | |||||||

| LDO7 | ||||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | 1 | 3.3 | V | |||

| Step size | 100 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 300 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 330 | 550 | 650 | mA | |||

| VDO | Dropout voltage | On mode, VDO = VIN – VOUT, | VIN = 2.7 V, IOUT = IOUTmax |

500 | mV | |||

| VIN = 2.7 V, IOUT = 250 mA |

400 | |||||||

| VIN = 2.7 V, IOUT = 200 mA |

300 | |||||||

| VIN = 1.7 V, IOUT = 180 mA |

700 | |||||||

| VIN = 1.7 V, IOUT = 150 mA |

500 | |||||||

| VIN = 1.7 V, IOUT = 100 mA |

300 | |||||||

| DC load regulation | On mode, IOUT = IOUTmax | 24 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = IOUTmax | 1 | mV | |||||

| Transient load regulation | On mode, VIN = 3.6 V, VOUTtyp = 3.3 V IOUT = 0.1 × IOUTmax to 0.9 × IOUTmax in 5 µs and IOUT = 0.9 × IOUTmax to 0.1 × IOUTmax in 5 µs |

16 | mV | |||||

| Transient line regulation | On mode, IOUT = IOUTmax / 2, VIN = 2.7 + 0.5 V to 2.7 in 30 µs and VIN = 2.7 V + 0.5 V in 30 µs, IOUT = IOUTmax / 2 |

5 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 20 | 50 | 70 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 120 | 180 | 250 | |||||

| Turn-on inrush current | 200 | 450 | mA | |||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+ = 3.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 20 kHz | 40 | |||||||

| LDO7 internal resistance | LDO off | 60 | Ω | |||||

| Ground current | On mode, IOUT = 0 | 65 | 76 | µA | ||||

| On mode, IOUT = IOUTmax | 2000 | |||||||

| Low-power mode | 14 | 22 | ||||||

| Off mode | 1 | |||||||

7.23 LDO8

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| VIN | Input voltage (VCC8) | VOUT(VLDO8) ≤ 1.2 V | 1.7 | 1.9 | V | |||

| VOUT(VLDO8) > 1.2 V (See Dropout Voltage parameter for additional constraints) | 1.7 | 5.5 | ||||||

| VOUT | DC output voltage | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | 1 | 3.3 | V | |||

| Step size | 100 | mV | ||||||

| DC output voltage accuracy | ON and low-power mode, VOUT < VIN – VDO , IOUT = 0 mA | –2.5% | 3% | |||||

| IOUTmax | Rated output current | On mode | 300 | mA | ||||

| Low-power mode | 1 | |||||||

| Load current limitation (short-circuit protection) | On mode, VOUT = VOUTmin – 100 mV | 330 | 550 | 650 | mA | |||

| VDO | Dropout voltage | On mode, VDO = VIN – VOUT | VIN = 3.3 V, IOUT = 70 mA |

100 | mV | |||

| VIN = 3.3 V, IOUT = 10 mA |

25 | |||||||

| VIN = 2.7 V, IOUT = IOUTmax |

500 | |||||||

| VIN = 2.7 V, IOUT = 250 mA |

400 | |||||||

| VIN = 2.7 V, IOUT = 200 mA |

300 | |||||||

| VIN = 1.7 V, IOUT = 180 mA |

700 | |||||||

| VIN = 1.7 V, IOUT = 150 mA |

500 | |||||||

| VIN = 1.7 V, IOUT = 100 mA |

300 | |||||||

| DC load regulation | On mode, IOUT = IOUTmax | 26 | mV | |||||

| DC line regulation | On mode, VIN = VINmin to VINmax at IOUT = IOUTmax | 1 | mV | |||||

| Transient load regulation | On mode, VIN = 1.7 V, VOUTtyp = 1.2 V IOUT = 10 mA to 90 mA in 5 µs and IOUT = 90 mA to 10 mA in 5 µs |

7 | mV | |||||

| Transient line regulation | On mode, IOUT = 100 mA, VIN = 2.7 V + 0.2 V to 2.7 V in 30 µs and VIN = 2.7 V to 2.7 V + 0.2 V in 30 µs, IOUT = 100 mA |

5 | mV | |||||

| Turn-on time | IOUT = 0, at VOUT = 0.1 V up to VOUTmin | 20 | 50 | 70 | µs | |||

| IOUT = 0, at VOUT = 0.1 V up to VOUTmax | 120 | 180 | 250 | |||||

| Turn-on inrush current | 200 | 450 | mA | |||||

| Ripple rejection | VIN = VINDC + 100 mVpp tone, VINDC+ = 3.8 V, IOUT = IOUTmax / 2 | f = 217 Hz | 70 | dB | ||||

| f = 20 kHz | 40 | |||||||

| LDO8 internal resistance | LDO off | 60 | Ω | |||||

| Ground current | On mode, IOUT = 0 | 65 | 76 | µA | ||||

| On mode, IOUT = IOUTmax | 2000 | |||||||

| Low-power mode | 14 | 22 | ||||||

| Off mode | 1 | |||||||

7.24 Timing Requirements for Boot Sequence Example

See Figure 1.| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| tdsON1 | PWRHOLD rising edge to VIO, LDO5 enable delay | 66 × tCK32k = 2060 | µs | ||

| tdsON2 | VIO to VDD2 enable delay | 64 × tCK32k = 2000 | µs | ||

| tdsON3 | VDD2 to VDD1 enable delay | 64 × tCK32k = 2000 | µs | ||

| tdsON4 | VDD1 to LDO4 enable delay | 64 × tCK32k = 2000 | µs | ||

| tdsON5 | LDO4 to LDO3, LDO8 enable delay | 64 × tCK32k = 2000 | µs | ||

| tdsON6 | LDO3 to LDO6 enable delay | 64 × tCK32k = 2000 | µs | ||

| tdsON7 | LDO6 to CLK32KOUT rising-edge delay | 9 × 64 × tCK32k = 18000 | µs | ||

| tdsON8 | CLK32KOUT to NRESPWON, NRESPWON2 rising-edge delay | 64 × tCK32k = 2000 | µs | ||

| tdsONT | Total switch-on delay | 32 | ms | ||

| tdsOFF1 | PWRHOLD falling-edge to NRESPWON, NRESPWON2 falling-edge delay | 2 × tCK32k = 62.5 | µs | ||

| tdsOFF1B | NRESPWON falling-edge to CLK32KOUT low delay | 3 × tCK32k = 92 | µs | ||

| tdsOFF2 | PWRHOLD falling-edge to supplies and reference disable delay | 5 × tCK32k = 154 | µs | ||

7.25 Power Control Timing Requirements

See Figure 2.| PARAMETER | MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| tdbPWRONF | PWRON falling-edge debouncing delay | 100 | µs | |||

| tdbPWRONR | PWRON rising-edge debouncing delay | 3 × tCK32k = 94 | µs | |||

| tdbPWRHOLD | PWRON rising-edge debouncing delay | 2 × tCK32k = 63 | µs | |||

| tdOINT1 | INT1 (internal) power-on pulse duration after PWRON low-level (debounced) event | 1 | s | |||

| tdONPWHOLD | delay to set high PWRHOLD signal or DEV_ON control bit after NRESPWON released to keep on the supplies | tdOINT1 – tDSONT = 970(1) | ms | |||

| tdPWRONLP | PWRON long-press delay | PWRON falling-edge to PWRON_LP_IT | 4 | s | ||

| tdPWRONLPTO | PWROW long-press interrupt (PWRON_LP_IT) to supplies switch-off | PWRON_LP_IT to NRESPWRON falling-edge | 1 | s | ||

7.26 Device SLEEP State Control Timing Requirements

See Figure 4.| PARAMETER | MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| tACT2SLP | SLEEP falling-edge to supply n low-power mode (SLEEP resynchronization delay) | 2 × tCK32k = 62 | 3 × tCK32k = 94 | µs | ||

| tACT2SLP | SLEEP falling-edge to CLK32KOUT low | 156 | tACT2SLP + 3 × tCK32k | 188 | µs | |

| tSLP2ACT | SLEEP rising edge to supply in high-power mode | 8 × tCK32k = 250 | 9 × tCK32k = 281 | µs | ||

| tSLP2ACTCK32K | SLEEP rising edge to CLK32KOUT running | 344 | tSLP2ACT + 3 × tCK32k | 375 | µs | |

| tdSLPON1 | SLEEP rising edge to time step 1 of the turn-on sequence from SLEEP state | 281 | tSLP2ACT + 1 × tCK32k | 312 | µs | |

| tdSLPONST | turn-on sequence step duration, from SLEEP state | TSLOT_LENGTH[1:0] = 00 | 0 | µs | ||

| TSLOT_LENGTH[1:0] = 01 | 200 | |||||

| TSLOT_LENGTH[1:0] = 10 | 500 | |||||

| TSLOT_LENGTH[1:0] = 11 | 2000 | |||||

| tdSLPONDCDC | VDD1, VDD2, or VIO turn-on delay from turn-on sequence time step | 2 × tCK32k = 62 | µs | |||

7.27 Supplies State Control Through EN1 and EN2 Timing Characteristics

See Figure 5 and Figure 6| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| tdEN | NRESPWRON to to supply state change delay, EN1 or EN2 driven | 0 | ms | ||

| tdOEN | EN1 or EN2 edge to supply state change delay | 1 × tCK32k = 31 | µs | ||

| tdVDDEN | EN1 or EN2 edge to VDD1 or VDD2 DCDC turn on delay | 3 × tCK32k = 63 | µs | ||

7.28 VDD1 Supply Voltage Control Through EN1 Timing Requirements

See Figure 7| PARAMETER | MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| tdDVSEN | EN1 (or EN2) edge to VDD1 (or VDD2) voltage change delay | 2 × tCK32k = 62 | µs | |||

| tdDVSENL | VDD1 (or VDD2) voltage settling delay | TSTEP[2:0] = 001 | 32 | µs | ||

| TSTEP[2:0] = 011 (default) | 0.4 / 7.5 = 53 | |||||

| TSTEP[2:0] = 111 | 160 | |||||

The TPS659119-Q1 device supports one fixed boot sequence and one EEPROM-programmable boot sequence. The Timing Requirements for Boot Sequence Example section lists and Figure 1 shows an example boot sequence. See the Boot Configuration and Switch-On and Switch-Off Sequences section for additional information on boot-mode selection.

Figure 1. Boot Sequence Example With 2-ms Time Slot and Simultaneous Switch-Off of Resources

Figure 1. Boot Sequence Example With 2-ms Time Slot and Simultaneous Switch-Off of Resources

Figure 2 shows the device-state control through the PWRON signal (see the Power Control Timing Requirements section).

NOTE:

DEV_ON or AUTODEV_ON control bits can be used instead of PWRHOLD signal to maintain supplies on after switch-on sequence.NOTE:

Internal POWER ON enable condition pulse TdOINT1 keeps device active until PWRHOLD acknowledge. Figure 3. PWRON Long-Press Turn-Off

Figure 3. PWRON Long-Press Turn-OffThe Power Control Timing Requirements Section Lists the Power Control Timing Characteristics

NOTE:

Registers programming: VIO_PSKIP = 0, VDD1_PSKIP = 0, VDD1_SETOFF = 1, LDO3_SETOFF = 1, LDO4_SETOFF = 1, LDO8_KEEPON = 1.See the Device SLEEP State Control Timing Requirements Section

Figure 5 and Figure 6 show the state control of the power supplies through the EN1 and EN2 signals (see the Supplies State Control Through EN1 and EN2 Timing Characteristics section).

NOTE:

Register setting: LDO1_EN1 = 1, LDO4_EN2 = 1, and LDO4_KEEPON = 1.

NOTE:

Register setting: VDD2_EN2 = 1, VDD1_EN1 = 1, VDD1_KEEPON = 1, VDD1_PSKIP = 0, and SEL[6:0] = hex00 in VDD2_SR_REG.

NOTE:

Register setting: VDD1_EN1 = 1, SEL[6:0] = hex13 in VDD1_SR_REGSee the VDD1 Supply Voltage Control Through EN1 Timing Requirements Section

7.29 Typical Characteristics

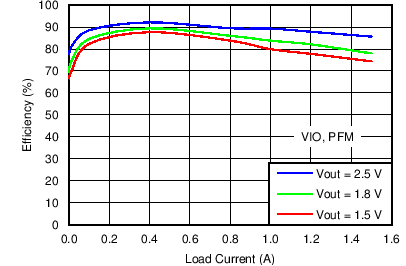

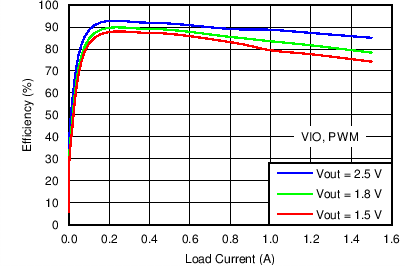

7.29.1 VIO SMPS Curves

Figure 8. VIO Efficiency vs Load Current,

Figure 8. VIO Efficiency vs Load Current, 25°C VIN = 4 V, PFM

Figure 9. VIO Efficiency vs Load Current,

Figure 9. VIO Efficiency vs Load Current, 25°C, VOUT = 2.5 V, VIN = 4 V, PWM

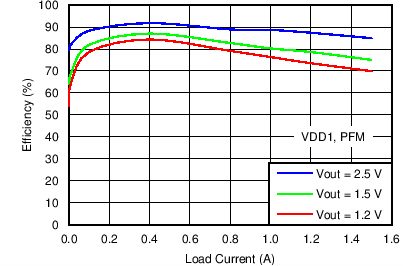

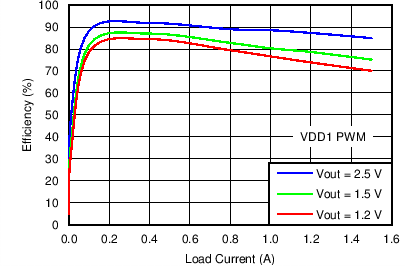

7.29.2 VDD1 SMPS Curves

Figure 10. VDD1 Efficiency vs Load Current,

Figure 10. VDD1 Efficiency vs Load Current, 25°C, VIN = 4 V, PFM

Figure 11. VDD1 Efficiency vs Load Current,

Figure 11. VDD1 Efficiency vs Load Current, 25°C, VIN = 4 V, PWM

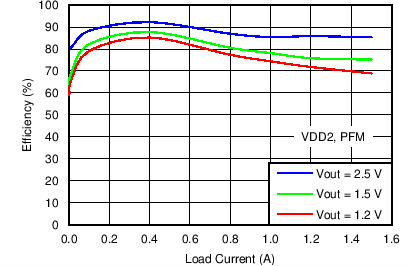

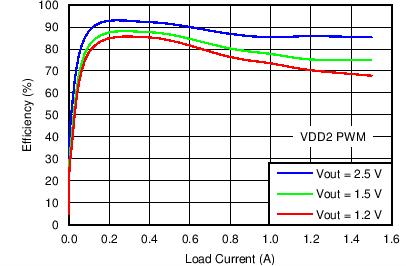

7.29.3 VDD2 SMPS Curves

Figure 12. VDD2 Efficiency vs Load Current,

Figure 12. VDD2 Efficiency vs Load Current, 25°C, VIN = 4 V, PFM

Figure 13. VDD2 Efficiency vs Load Current,

Figure 13. VDD2 Efficiency vs Load Current, 25°C, VIN = 4 V, PWM