SBVS037Q August 2003 – September 2024 TPS732

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- DRB|8

Orderable Information

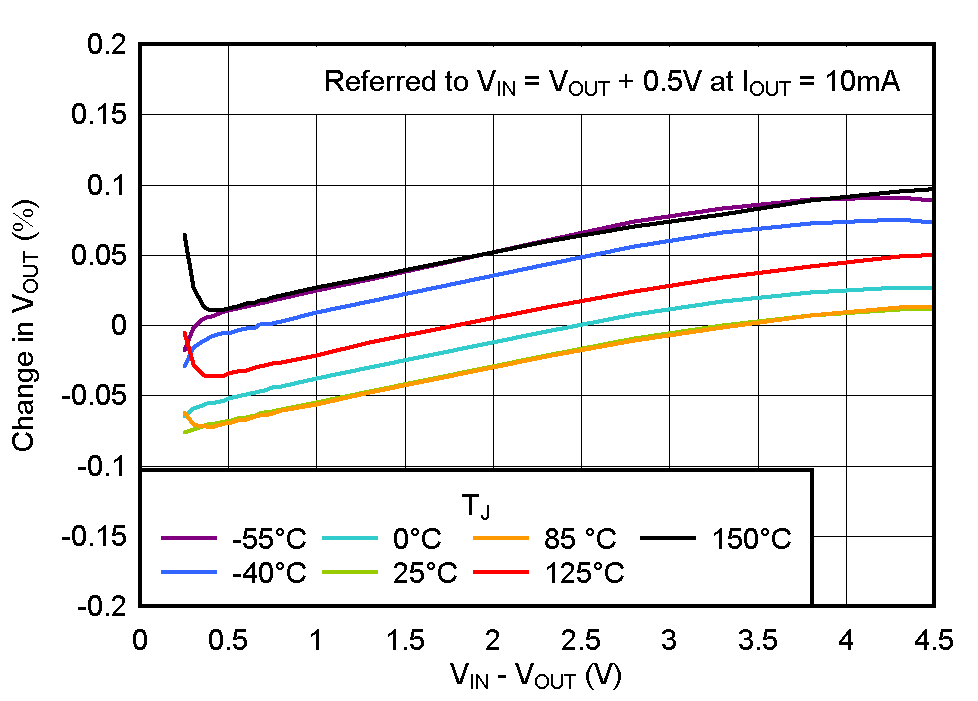

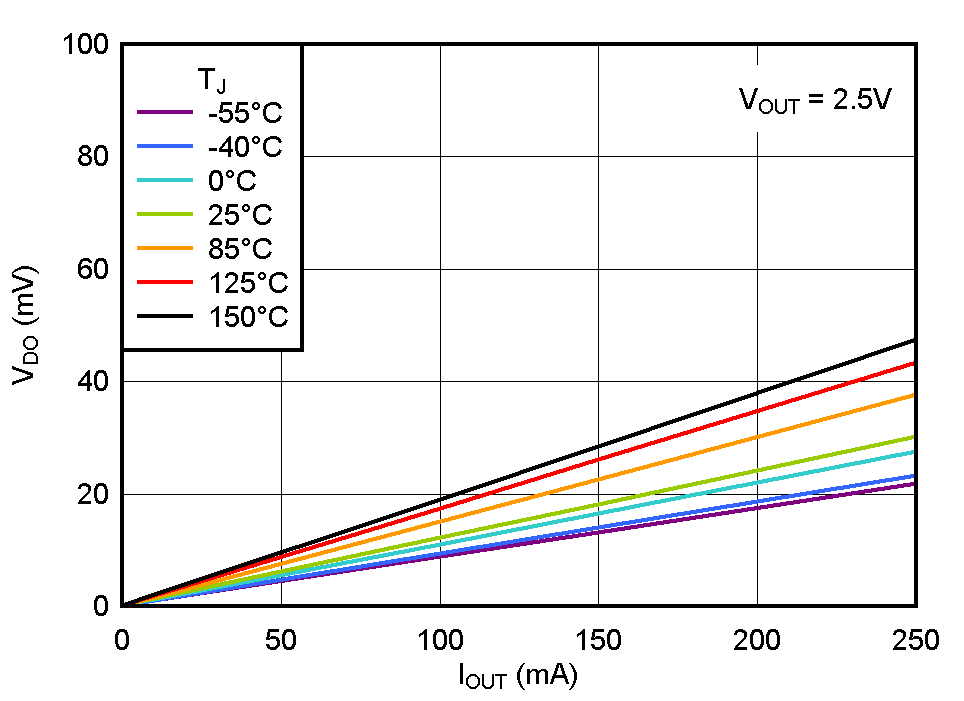

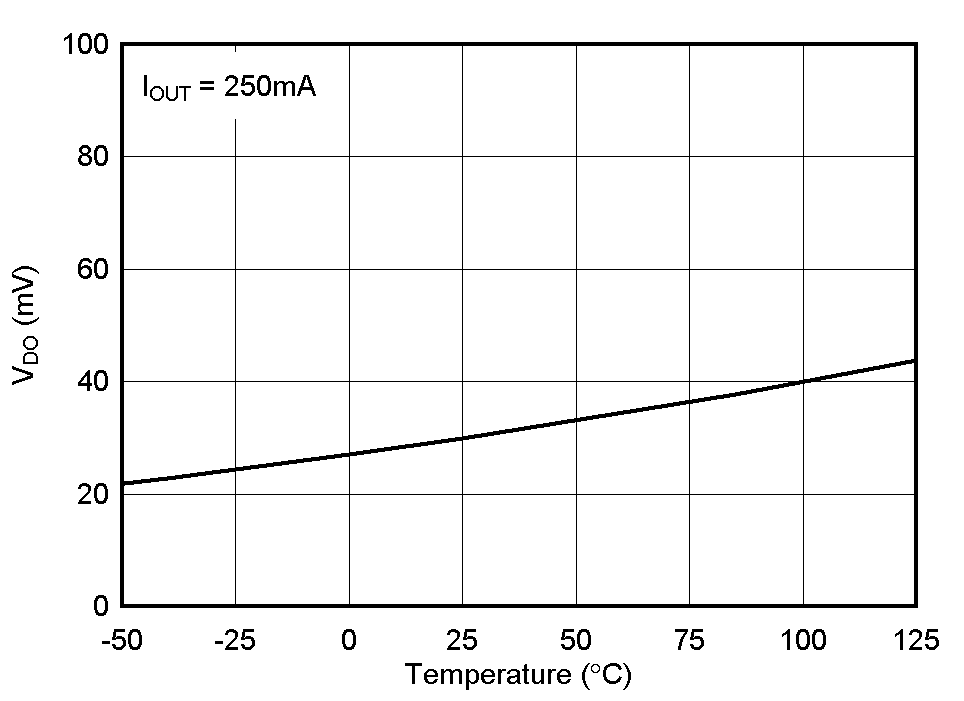

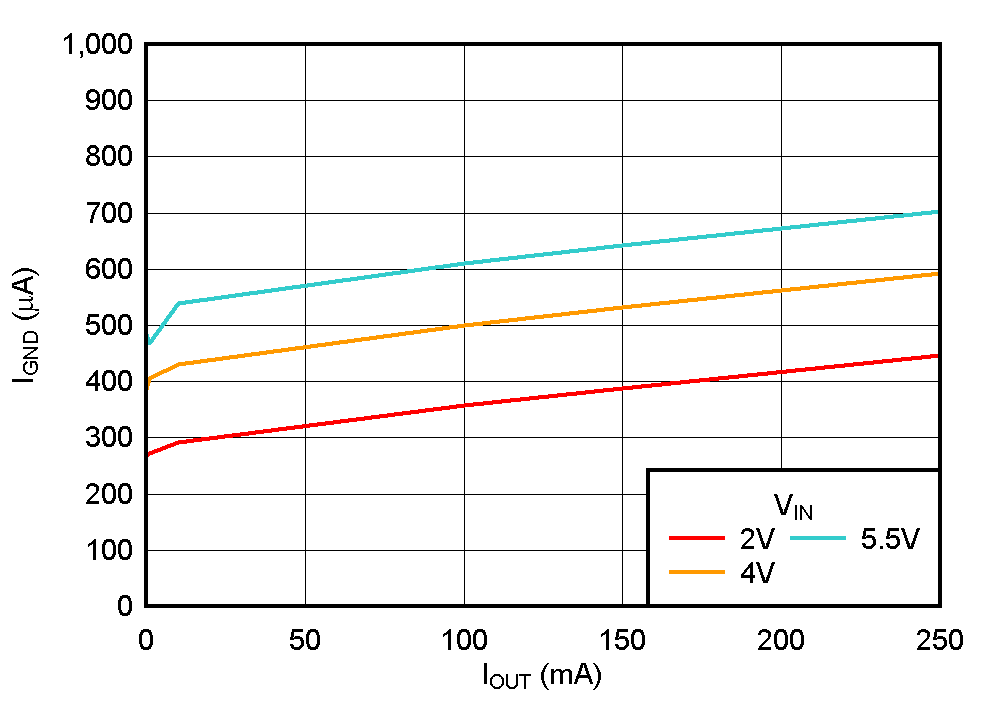

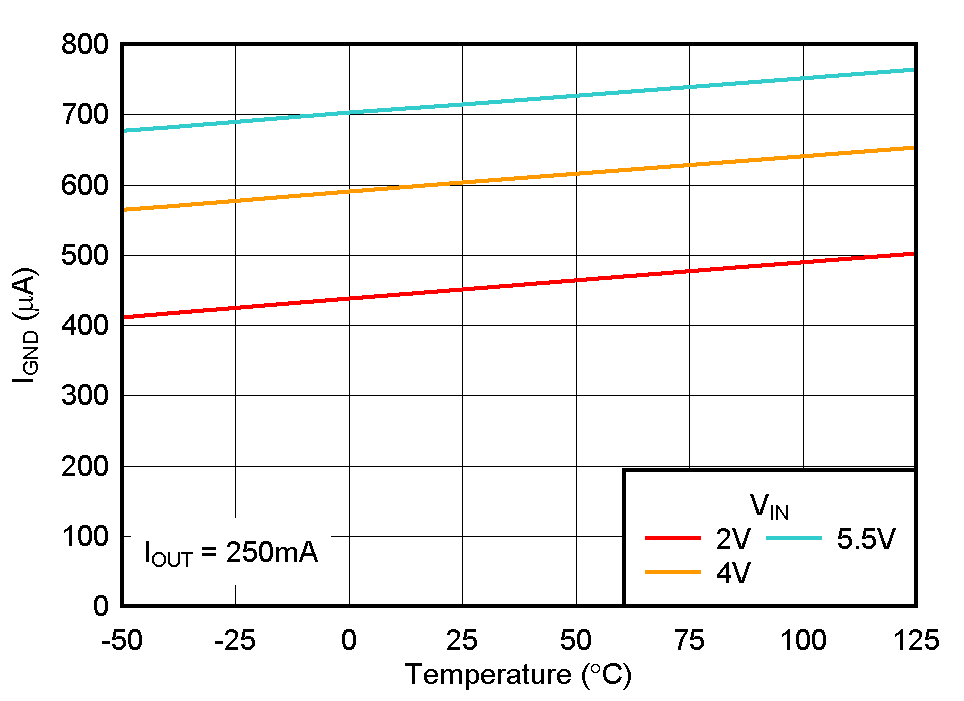

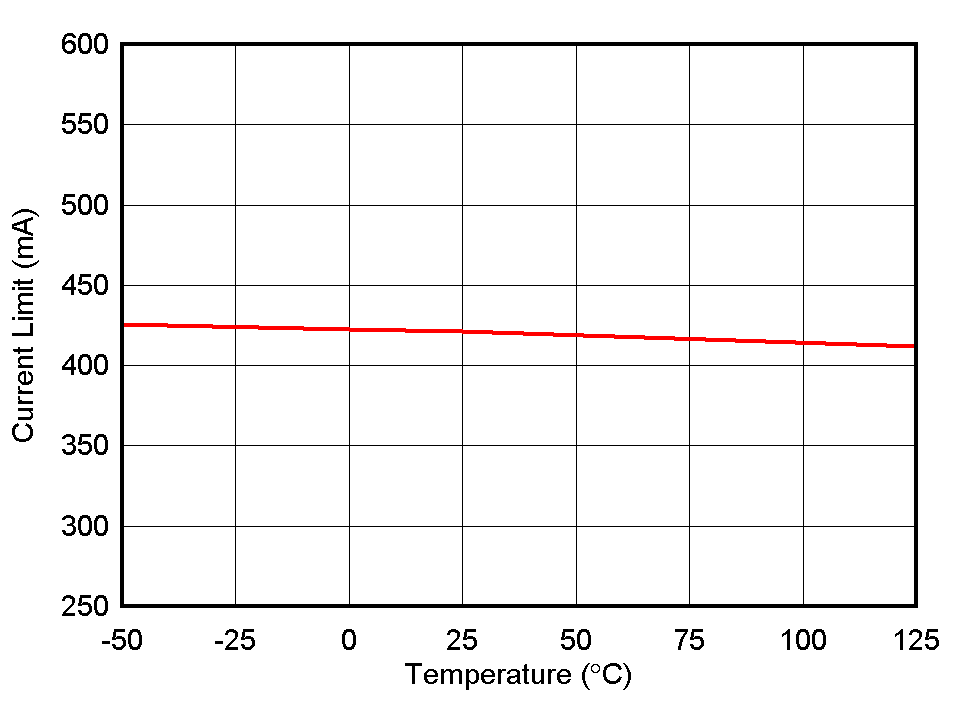

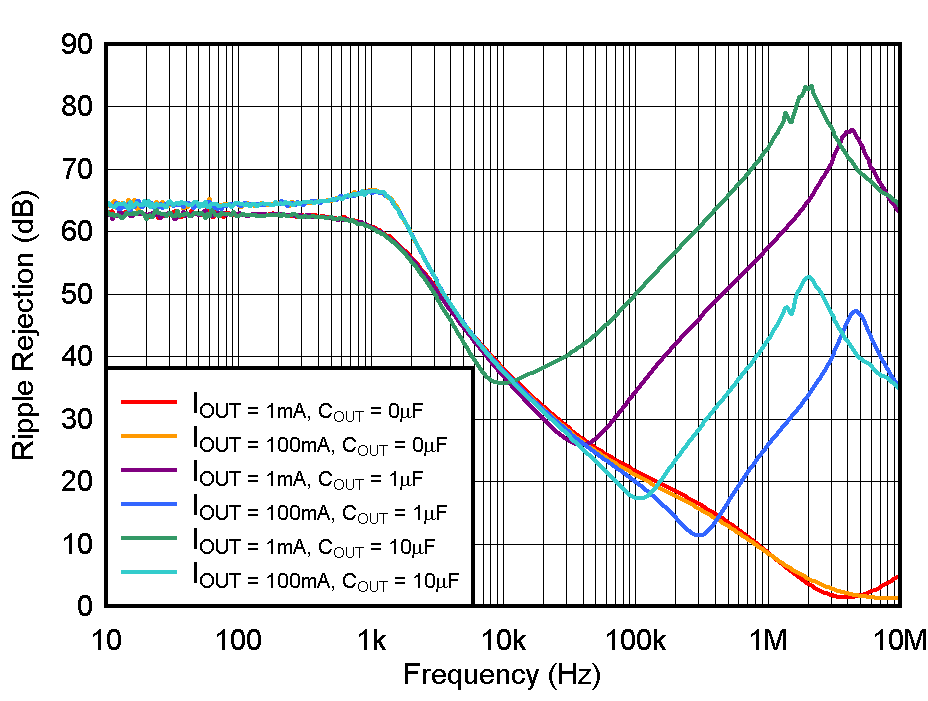

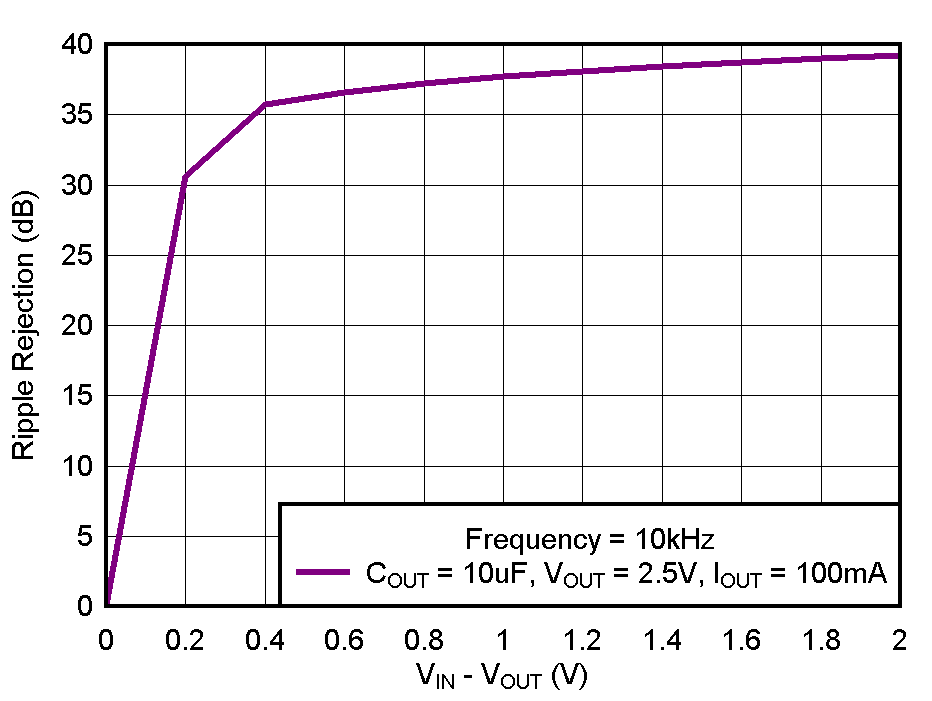

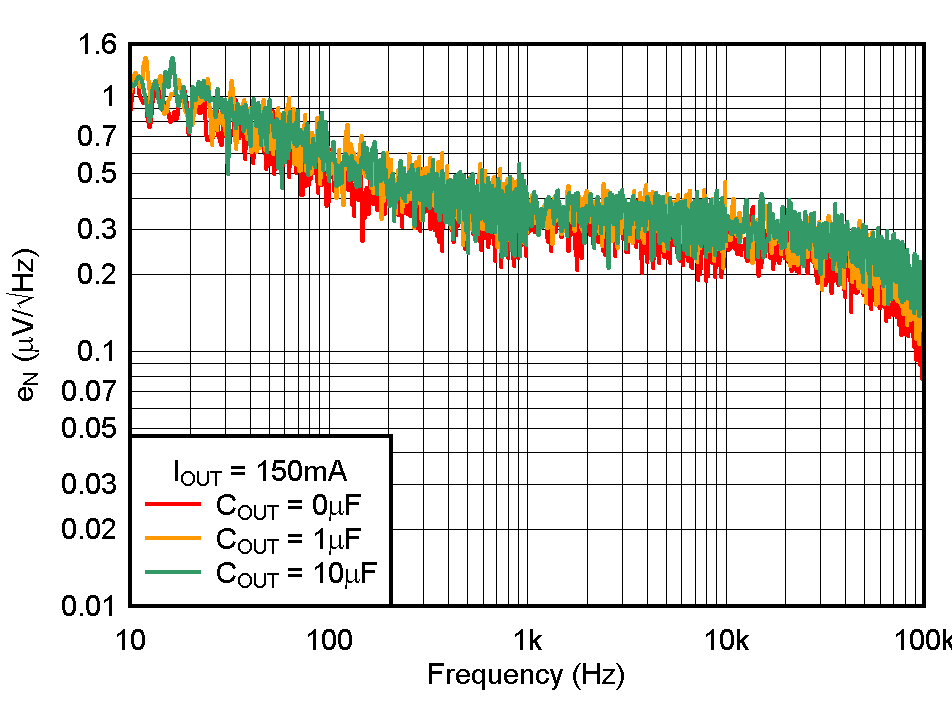

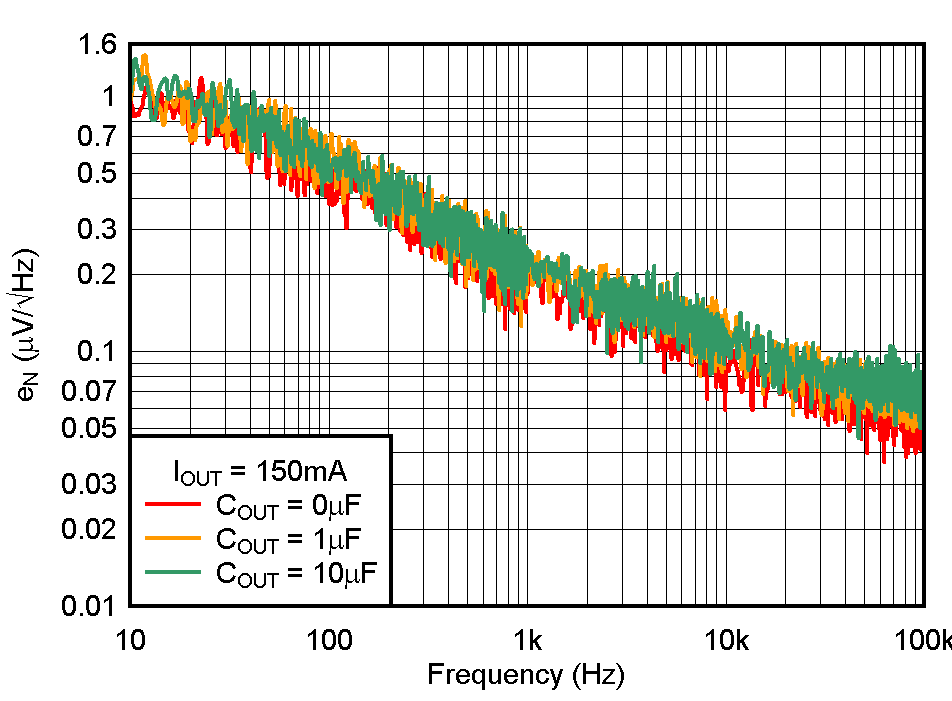

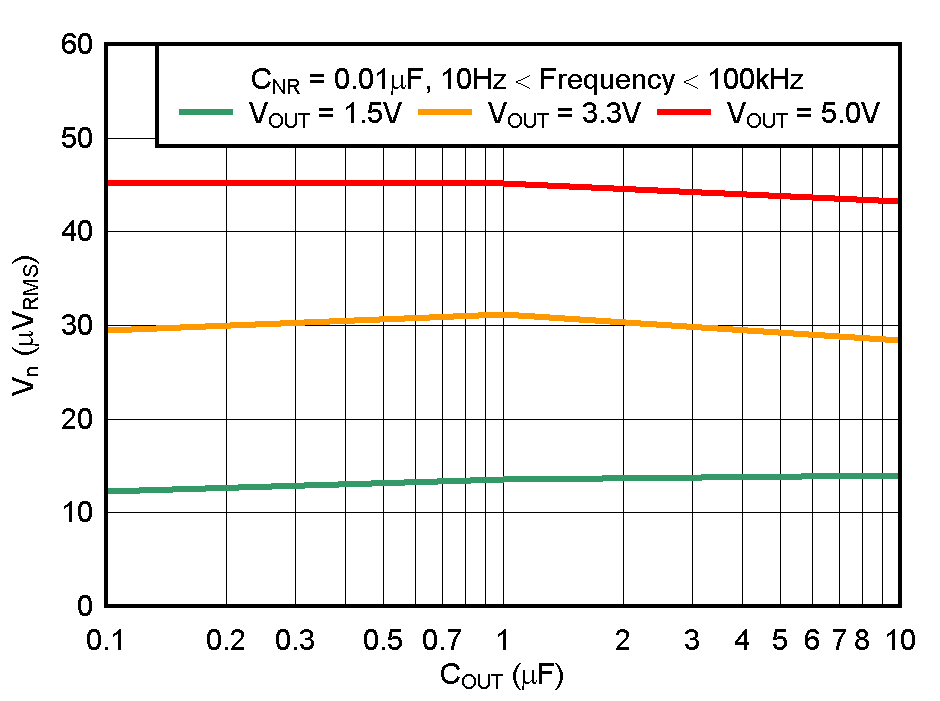

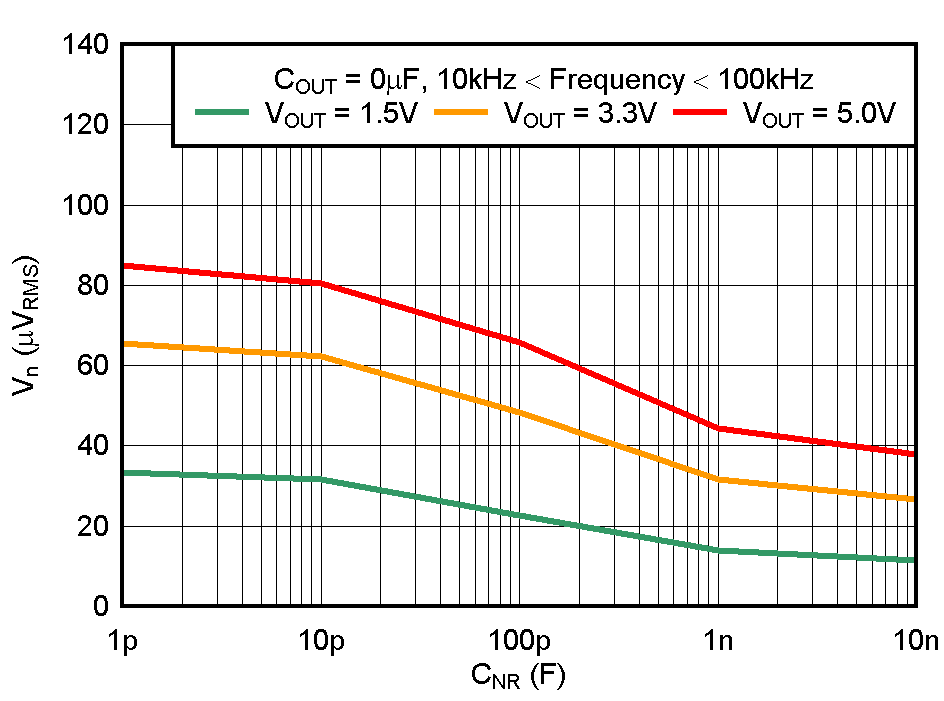

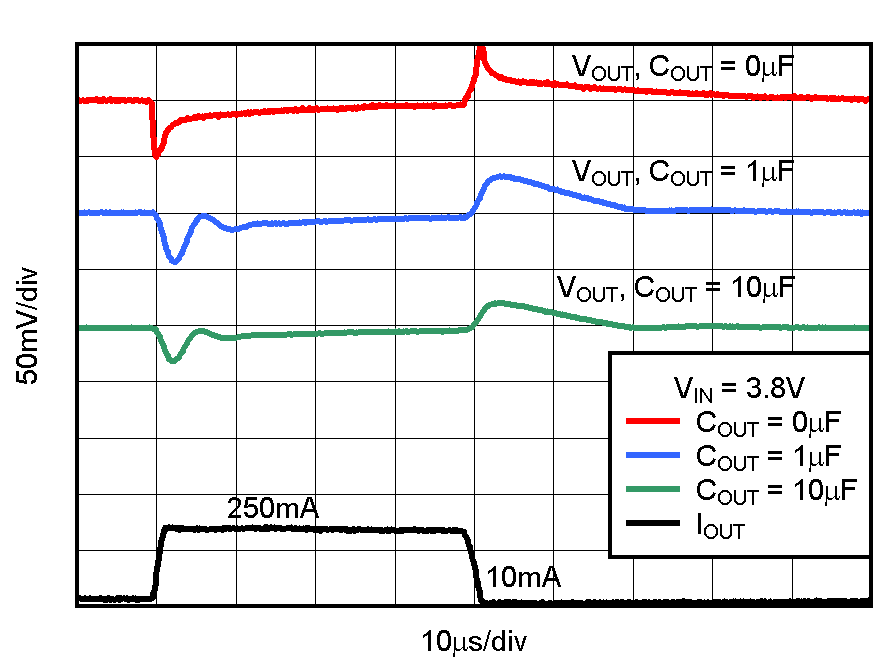

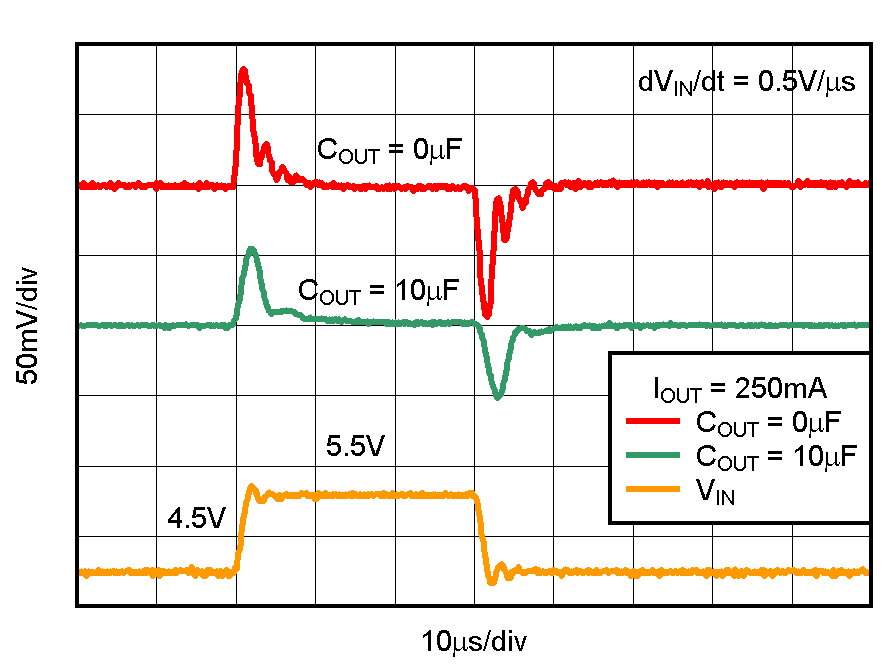

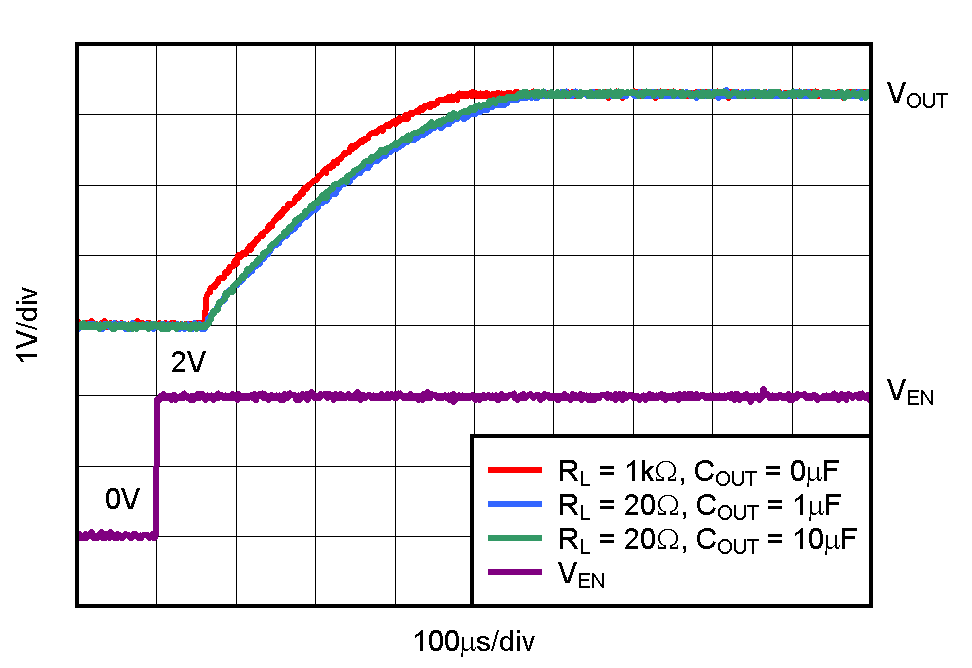

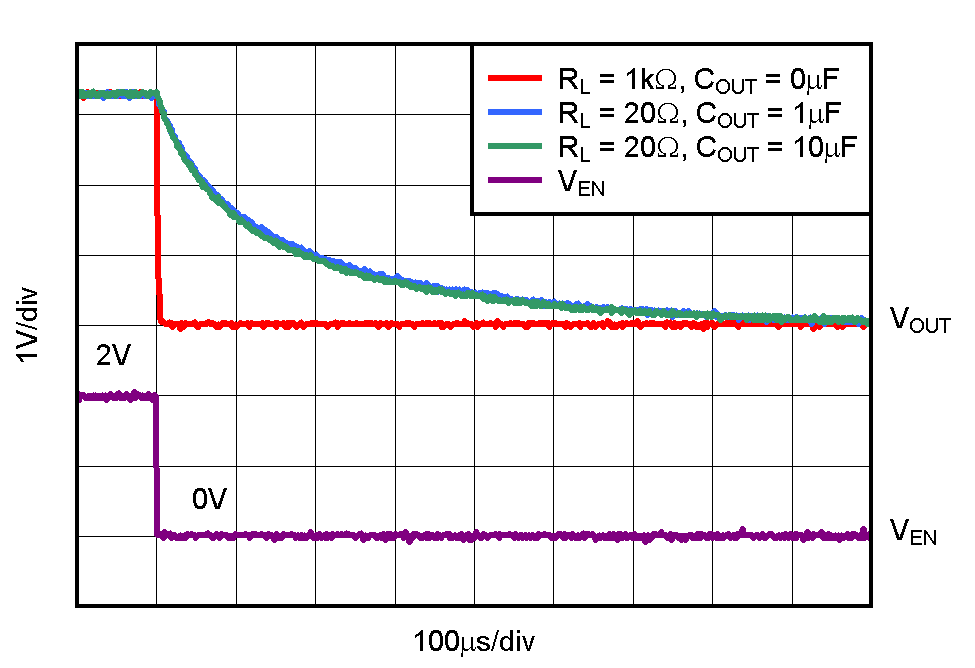

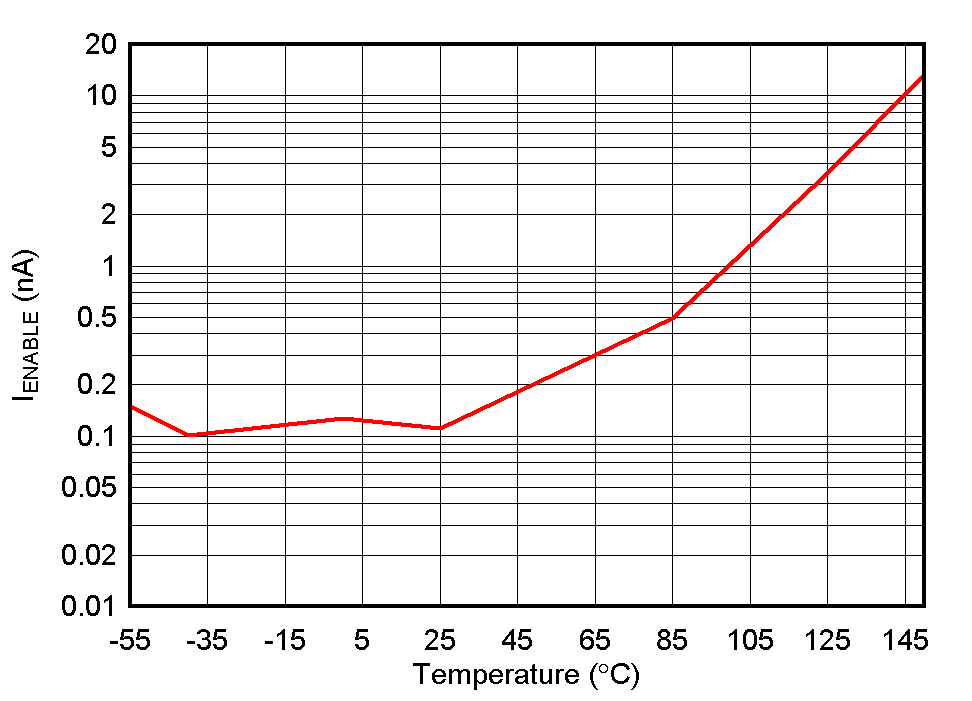

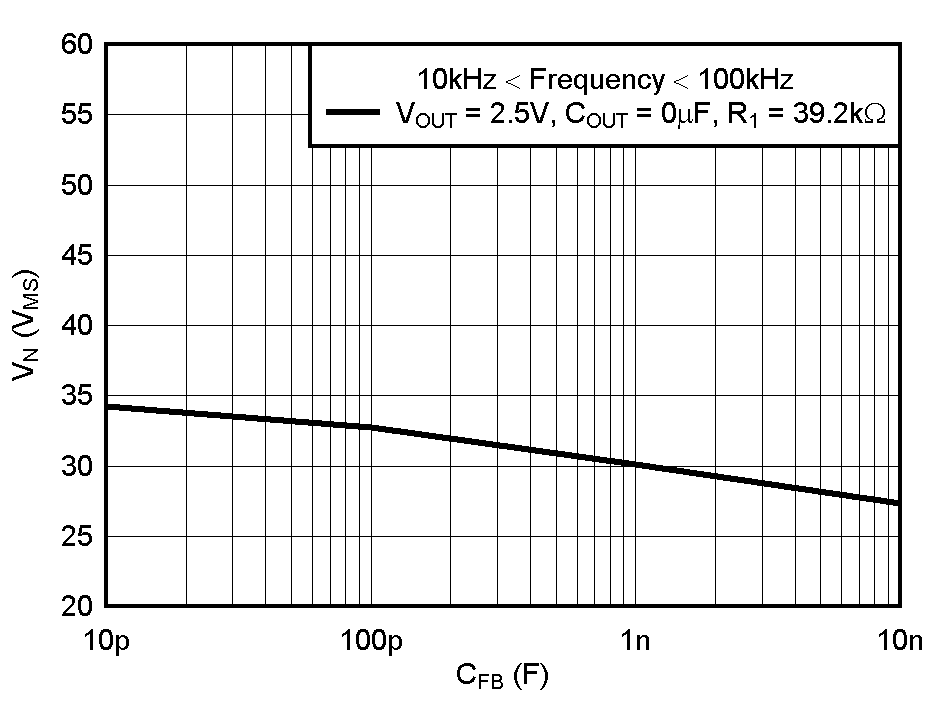

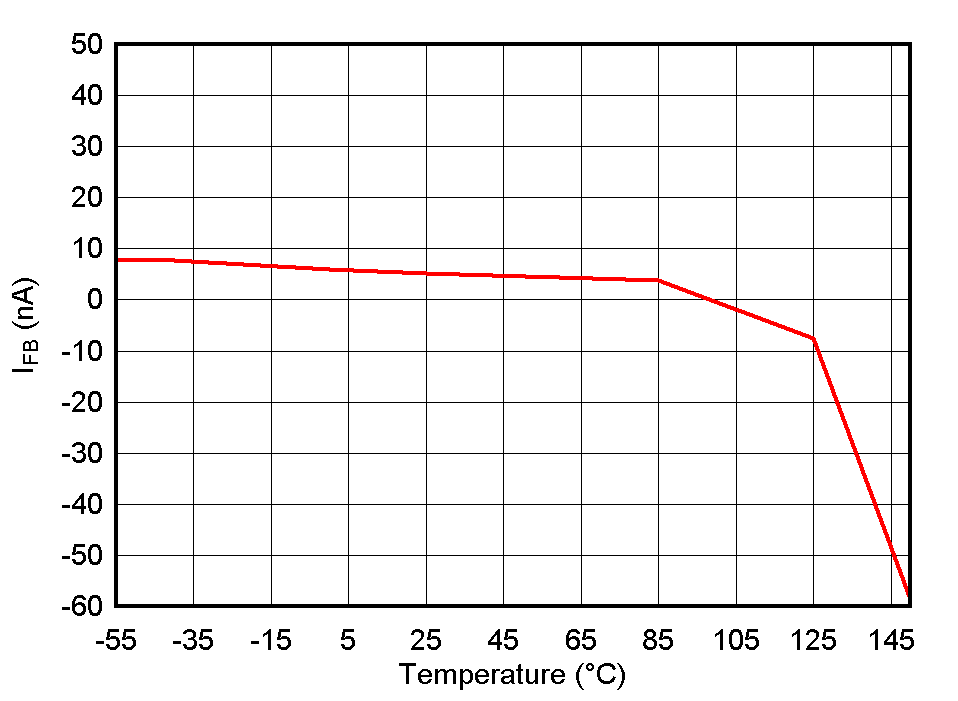

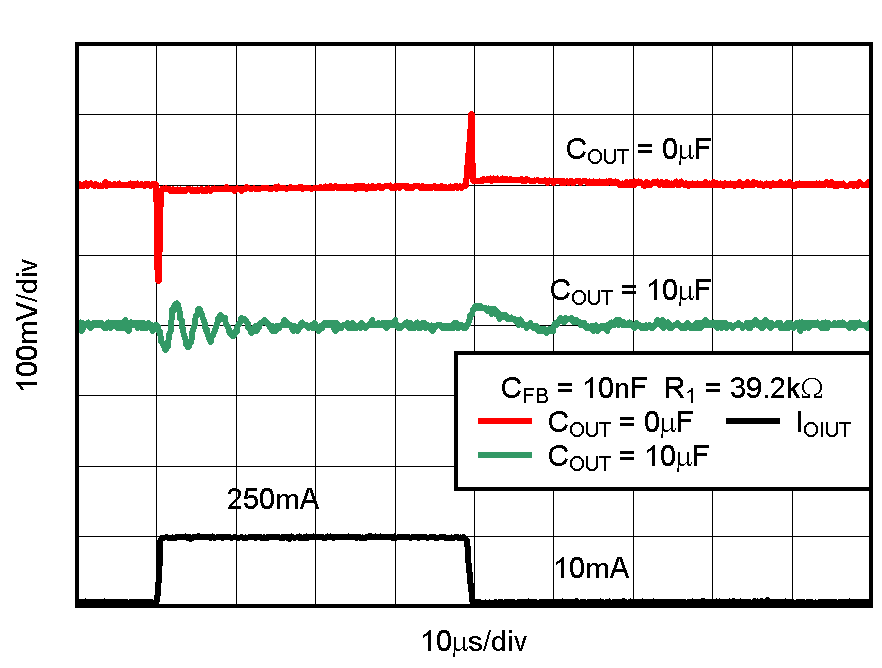

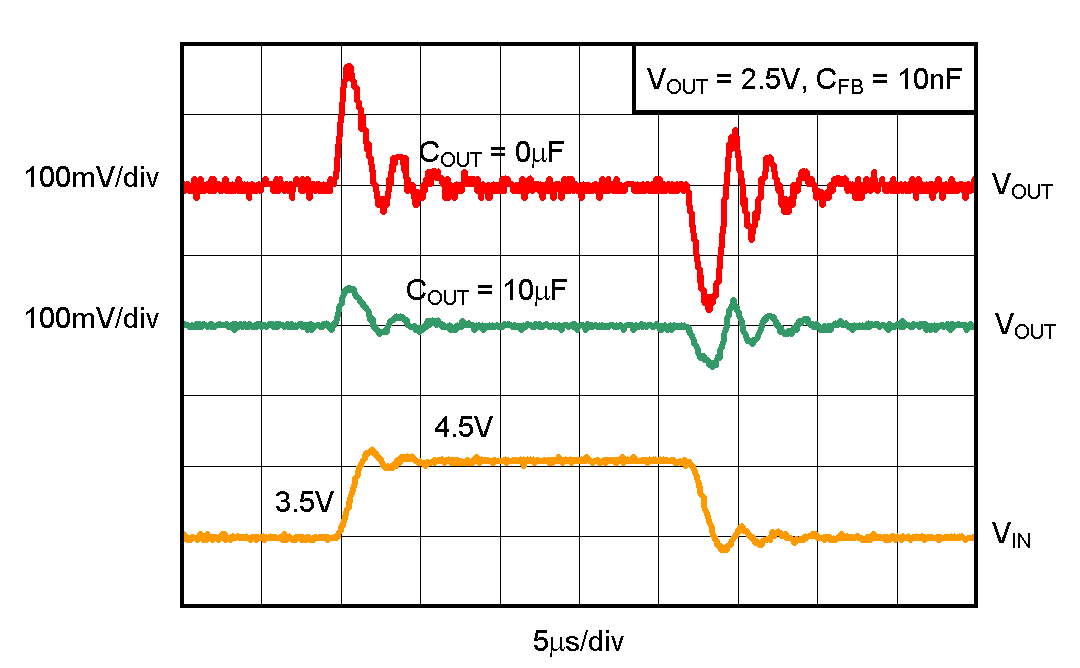

5.8 Typical Characteristics

for all voltage versions at TJ = 25°C, VIN = VOUT(nom) + 0.5V, IOUT = 10mA, VEN = 1.7V, and COUT = 0.1μF (unless otherwise noted)

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

.

Figure 5-45 IENABLE vs Temperature| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| Legacy silicon |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| Legacy silicon |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

.

Figure 5-46 IENABLE vs Temperature| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |

| New silicon, M3 suffix |