SBVS074N January 2007 – June 2024

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

3 Description

The TPS748 low-dropout (LDO) linear regulator provides an easy-to-use robust power management solution for a wide variety of applications. User-programmable soft-start minimizes stress on the input power source by reducing capacitive inrush current on start-up. The soft-start is monotonic and designed for powering many different types of processors and ASICs. The enable input and power-good output allow easy sequencing with external regulators. This complete flexibility allows a solution to be configured that meets the sequencing requirements of FPGAs, DSPs, and other applications with special start-up requirements.

A precision reference and error amplifier deliver 1% accuracy (new chip) over load, line, temperature, and process. The device is stable with any type of capacitor greater than or equal to 2.2μF, and is fully specified for TJ = –40°C to +125°C. The TPS748 is offered in a small, 3mm × 3mm, VSON-10 package, yielding a highly compact, total solution size. The device is also available in a 5mm × 5mm VQFN-20 package for compatibility with the TPS742.

| PART NUMBER | PACKAGE(1) | PACKAGE SIZE(2) |

|---|---|---|

| TPS748 | DRC (VSON, 10) | 3mm × 3mm |

| RGW (VQFN, 20) | 5mm × 5mm |

Typical Application Circuit

(Adjustable)

Typical Application Circuit

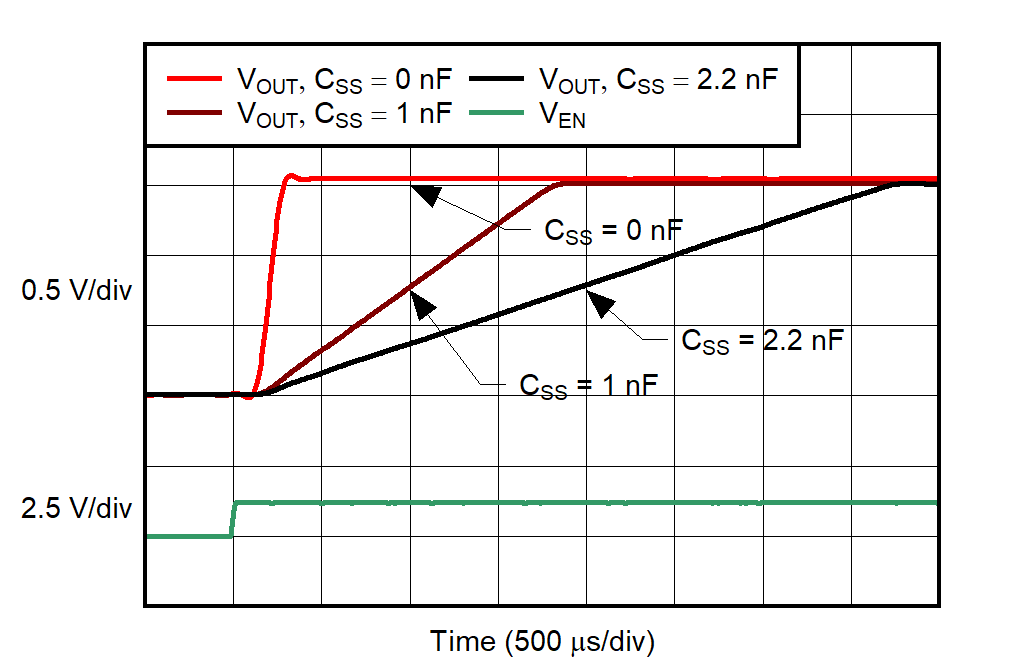

(Adjustable) Turn-On Response

Turn-On Response