SBVS189G March 2012 – October 2023 TPS7A7100

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configurations

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device And Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, And Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- RGT|16

- RGW|20

Thermal pad, mechanical data (Package|Pins)

- RGT|16

Orderable Information

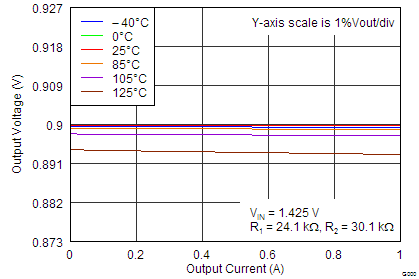

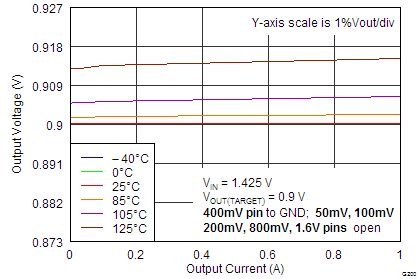

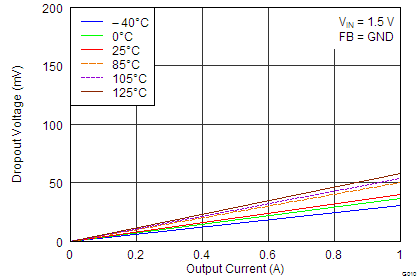

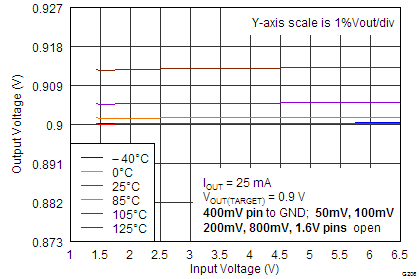

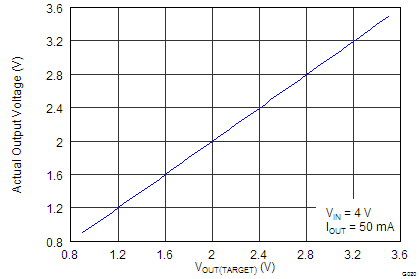

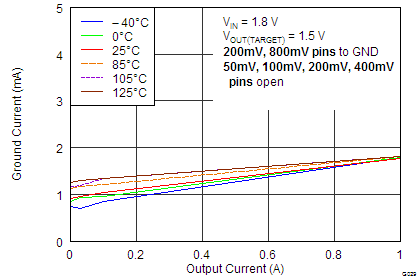

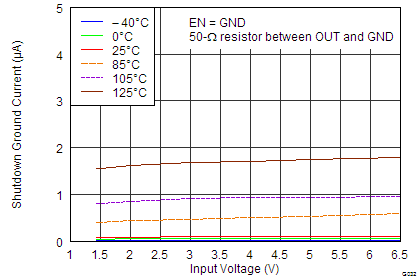

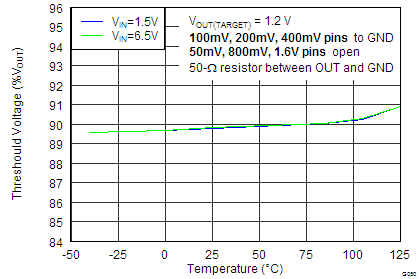

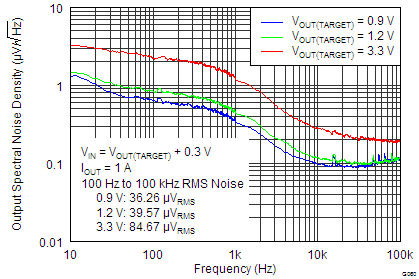

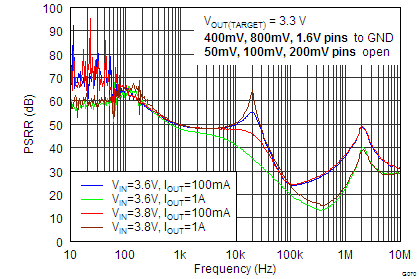

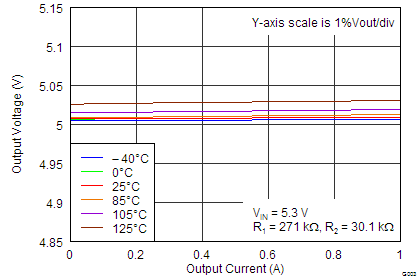

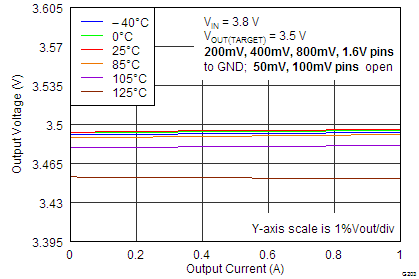

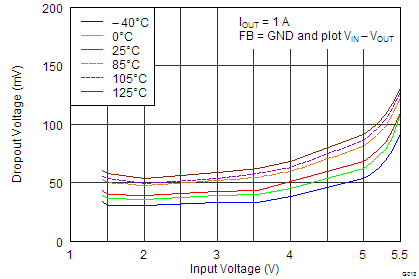

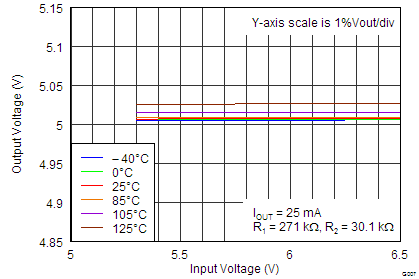

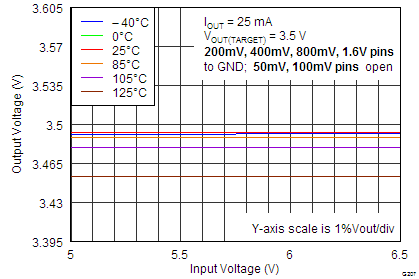

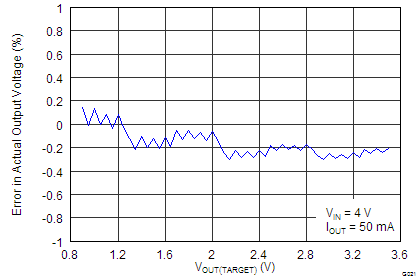

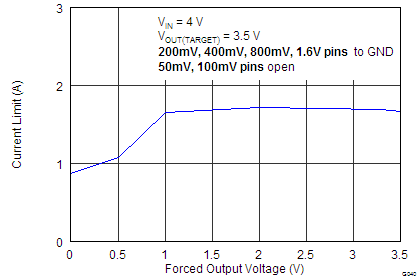

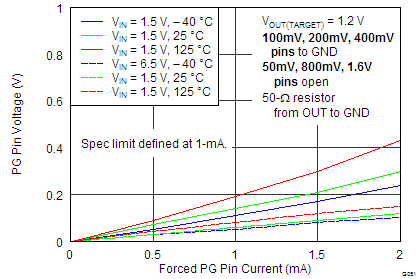

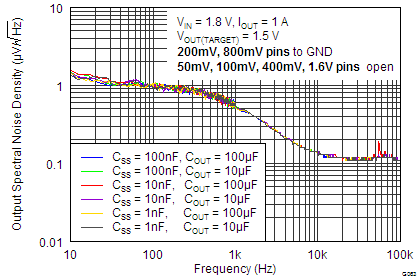

5.6 Typical Characteristics

at TJ = 25°C, VIN = VOUT(TARGET) + 0.3 V, IOUT = 25 mA, V(EN) = VIN, CIN = 10 μF, COUT = 10 μF, C(SS) = 10 nF, and the PG pin pulled up to VIN with a 100-kΩ pullup resistor (unless otherwise noted)