SBVS414 November 2021 TPS7H1210-SEP

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGW|20

Thermal pad, mechanical data (Package|Pins)

- RGW|20

Orderable Information

3 Description

The TPS7H1210-SEP negative voltage linear regulator is a low noise, high PSRR regulator capable of sourcing a maximum load of 1 A.

The regulator include a CMOS logic-level-compatible enable pin (EN) to allow for user-customizable power management schemes. Other features include built-in current limit and thermal shutdown to protect the device and system during fault conditions.

The TPS7H1210-SEP device is designed using bipolar technology primarily for high-accuracy, low-noise applications, where clean voltage rails are critical to maximize system performance. Therefore, it ideal to power op amps, ADCs, DACs, and other high-performance analog circuitry.

Additionally, the TPS7H1210-SEP device is suitable for post DC-DC converter regulation. By filtering the output voltage ripple inherent to DC-DC switching conversion, maximum system performance is ensured in sensitive devices and RF applications.

| PART NUMBER(1) | GRADE | PACKAGE(2) |

|---|---|---|

| TPS7H1210MRGWSEP | 20 krad(Si) RLAT, 30 krad(Si) characterized | VQFN (20) 5.00 mm × 5.00 mm Mass = 83.6 mg |

| TPS7H1210EVM | Evaluation board | EVM |

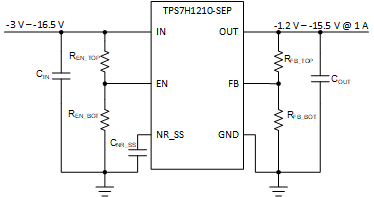

Typical Application

Schematic

Typical Application

Schematic