DLPS202A October 2020 – August 2024 TPS99000S-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Electrical Characteristics—Transimpedance Amplifier Parameters

- 5.6 Electrical Characteristics—Digital to Analog Converters

- 5.7 Electrical Characteristics—Analog to Digital Converter

- 5.8 Electrical Characteristics—FET Gate Drivers

- 5.9 Electrical Characteristics—Photo Comparator

- 5.10 Electrical Characteristics—Voltage Regulators

- 5.11 Electrical Characteristics—Temperature and Voltage Monitors

- 5.12 Electrical Characteristics—Current Consumption

- 5.13 Power-Up Timing Requirements

- 5.14 Power-Down Timing Requirements

- 5.15 Timing Requirements—Sequencer Clock

- 5.16 Timing Requirements—Host and Diagnostic Port SPI Interface

- 5.17 Timing Requirements—ADC Interface

- 5.18 Switching Characteristics

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3

Feature Description

- 6.3.1

Illumination Control

- 6.3.1.1 Illumination System High Dynamic Range Dimming Overview

- 6.3.1.2 Illumination Control Loop

- 6.3.1.3 Continuous Mode Operation

- 6.3.1.4

Discontinuous Mode Operation

- 6.3.1.4.1 Discontinuous Mode Pulse Width Limit

- 6.3.1.4.2 COMPOUT_LOW Timer in Discontinuous Operation

- 6.3.1.4.3 Dimming Within Discontinuous Operation Range

- 6.3.1.4.4 Multiple Pulse Heights to Increase Bit Depth

- 6.3.1.4.5 TIA Gain Adjustment

- 6.3.1.4.6 Current Limit in Discontinuous Mode

- 6.3.1.4.7 CMODE Big Cap Mode in Discontinuous Operation

- 6.3.2 Over-Brightness Detection

- 6.3.3 Analog to Digital Converter

- 6.3.4 Power Sequencing and Monitoring

- 6.3.5 DMD Mirror Voltage Regulator

- 6.3.6 Low Dropout Regulators

- 6.3.7 System Monitoring Features

- 6.3.8 Communication Ports

- 6.3.1

Illumination Control

- 6.4 Device Functional Modes

- 6.5 Register Maps

- 7 Application and Implementation

- 8 Power Supply Recommendations

- 9 Layout

- 10Device and Documentation Support

- 11Revision History

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PZP|100

Thermal pad, mechanical data (Package|Pins)

- PZP|100

Orderable Information

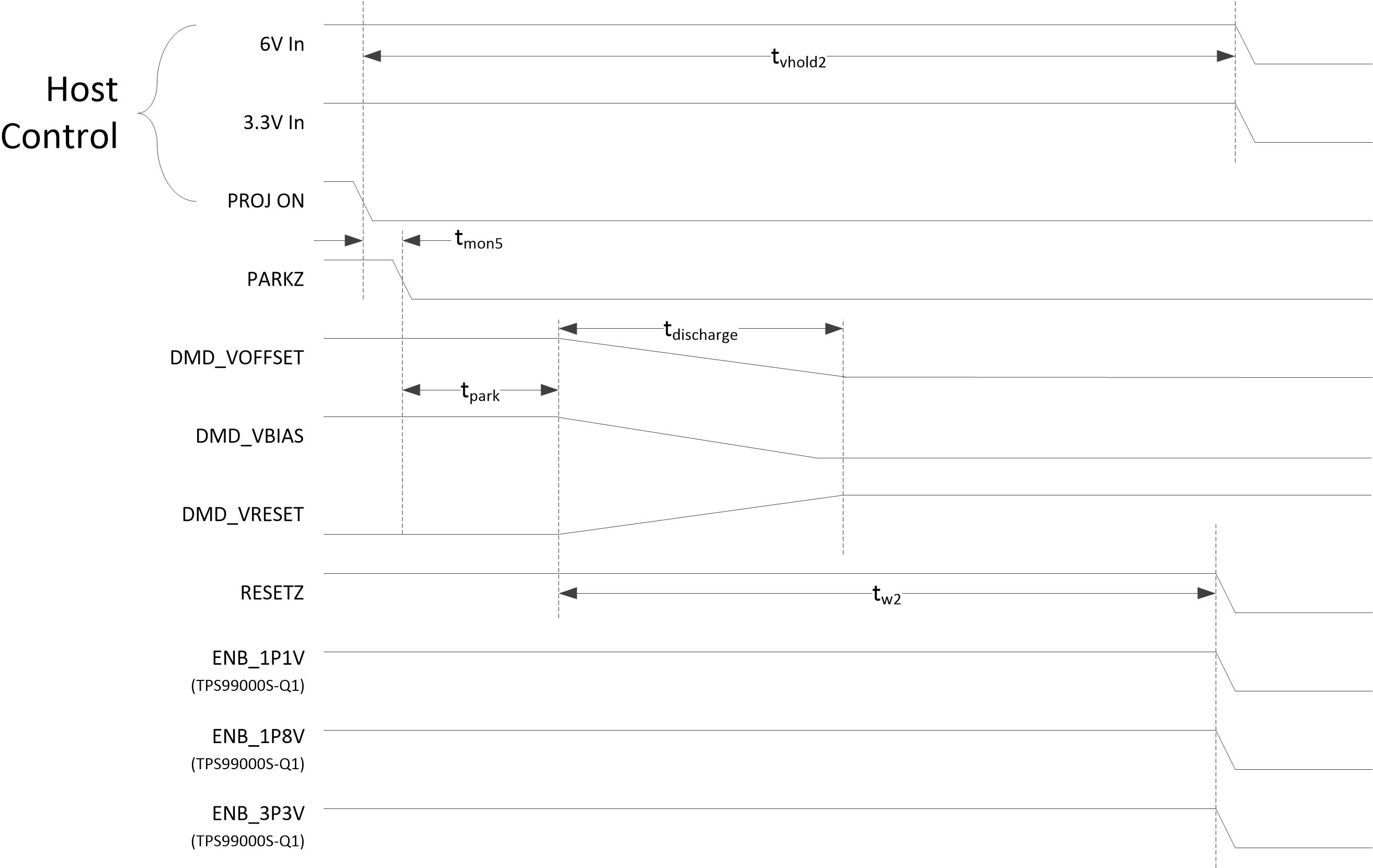

5.14 Power-Down Timing Requirements

See (1)

| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| tvhold1 | Host voltage hold time after VMAIN minimum

threshold reached. tmon4(max) + tpark(max) + tw2(max) |

VMAIN threshold to 6V and 3.3V power loss(2)(3) | 900 | μs | |

| tvhold2 | Host voltage hold time after PROJ_ON

deasserted. tmon5(max) + tpark(max) + tw2(max) |

VMAIN threshold to 6V and 3.3V power loss.(2)(3) | 1.78 | ms | |

| tmon4 | VMAIN monitoring time | Minimum voltage trip threshold to PARKZ falling edge | 52 | 120 | μs |

| tmon5 | PROJ_ON deassertion reaction time | Falling edge of PROJ_ON to PARKZ falling edge | 1 | ms | |

| tpark | DMD Park time | PARKZ falling edge to start DMD_VOFFSET discharge | 280 | μs | |

| tdischarge(4) | DMD voltage rail discharge time | VOFFSET Cout = 1μF VRESET Cout = 1μF VBIAS Cout = 0.47μF |

260 | μs | |

| tw2 | DMD voltage disables to RESETZ deassertion | Start of DMD voltage rail discharge to RESETZ falling edge | 500 | μs | |

(1) There are two methods for initiating the power-down sequence:

- VMAIN voltage decreases below its minimum threshold. This is typical if the TPS99000S-Q1 is expected to initiate the power-down sequence when the main power is removed from the system. Note that the 6V and 3.3V input rails must remain within the operating range for a specified period of time after the power-down sequence begins.

- PROJ_ON low. This allows a host controller to initiate power down through a digital input to the TPS99000S-Q1.

(2) 6V input rails include DRVR_PWR, VIN_DRST, VIN_LDOT_5V,

VIN_LDOA_3P3V, VIN_LDOT3P3V.

(3) 3.3V input rails include VDD_IO, DVDD, AVDD.

(4) The DMD specifies a maximum absolute voltage difference between

VBIAS and VOFFSET. To remain below this maximum voltage difference, VBIAS must

discharge faster than VOFFSET. This is accomplished by using a smaller

Cout capacitance for VBIAS to allow it to discharge quicker than

VOFFSET.

Figure 5-2 Power

Down Timing—VMAIN Trigger

Figure 5-2 Power

Down Timing—VMAIN Trigger Figure 5-3 Power

Down Timing—PROJ_ON Trigger

Figure 5-3 Power

Down Timing—PROJ_ON Trigger