SLUSDH7C February 2019 – January 2024 UCC21732-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Power Ratings

- 5.6 Insulation Specifications

- 5.7 Safety-Related Certifications

- 5.8 Safety Limiting Values

- 5.9 Electrical Characteristics

- 5.10 Switching Characteristics

- 5.11 Insulation Characteristics Curves

- 5.12 Typical Characteristics

- 6 Parameter Measurement Information

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Power Supply

- 7.3.2 Driver Stage

- 7.3.3 VCC and VDD Undervoltage Lockout (UVLO)

- 7.3.4 Active Pulldown

- 7.3.5 Short Circuit Clamping

- 7.3.6 External Active Miller Clamp

- 7.3.7 Overcurrent and Short Circuit Protection

- 7.3.8 2-Level Turn-Off

- 7.3.9 Fault ( FLT, Reset and Enable ( RST/EN)

- 7.3.10 Isolated Analog to PWM Signal Function

- 7.4 Device Functional Modes

-

8 Applications and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Input Filters for IN+, IN- and RST/EN

- 8.2.2.2 PWM Interlock of IN+ and IN-

- 8.2.2.3 FLT, RDY and RST/EN Pin Circuitry

- 8.2.2.4 RST/EN Pin Control

- 8.2.2.5 Turn-On and Turn-Off Gate Resistors

- 8.2.2.6 External Active Miller Clamp

- 8.2.2.7 Overcurrent and Short Circuit Protection

- 8.2.2.8 Isolated Analog Signal Sensing

- 8.2.2.9 Higher Output Current Using an External Current Buffer

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DW|16

Thermal pad, mechanical data (Package|Pins)

- DW|16

Orderable Information

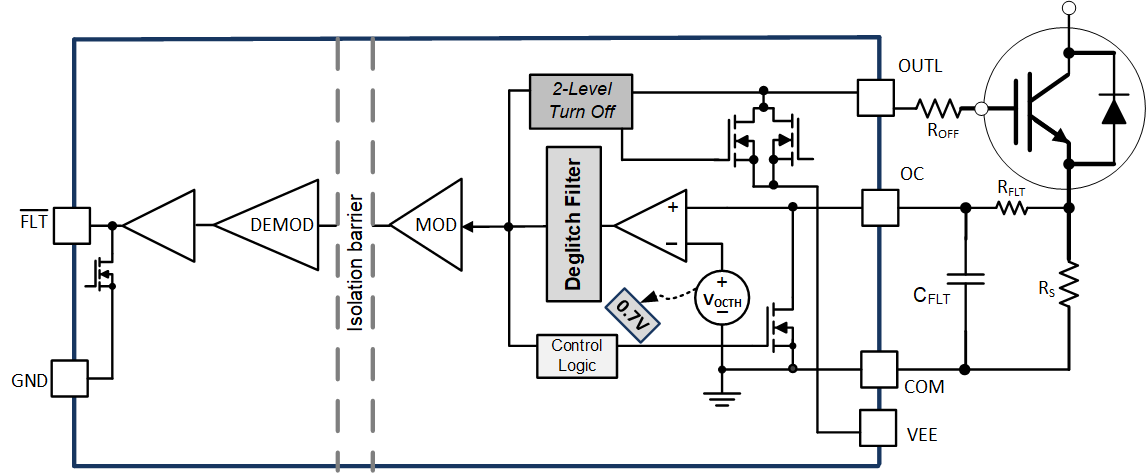

7.3.8 2-Level Turn-Off

The UCC21732-Q1 initiates a fast 2-level turn-off when the overcurrent and short circuit protection is triggered. When the overcurrent and short circuit fault happens, the power power semiconductor transits from the linear region to the saturation region very fast. The channel current is controlled by the gate voltage. By pulling down the gate voltage to a mid-voltage level V2LOFF and stay for a fixed time t2LOFF, the channel current can be limited to a much lower level, which significantly reduces the energy dissipation during the fault event. After t2LOFF, the driver continues to pull down the gate voltage by the soft turn off current ITL3 until it reaches VEE. With dI/dt of the channel current is controlled by the gate voltage and decreasing in a soft manner, thus the overshoot of the power semiconductor is limited and prevents the overvoltage breakdown. The timing diagram of 2-level turn-off shows in Figure 6-10.

Figure 7-6 2-Level Turn-Off

Figure 7-6 2-Level Turn-Off