SBOS061C February 1997 – October 2024 XTR105

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|14

- N|14

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6.3.2 Voltage Regulator

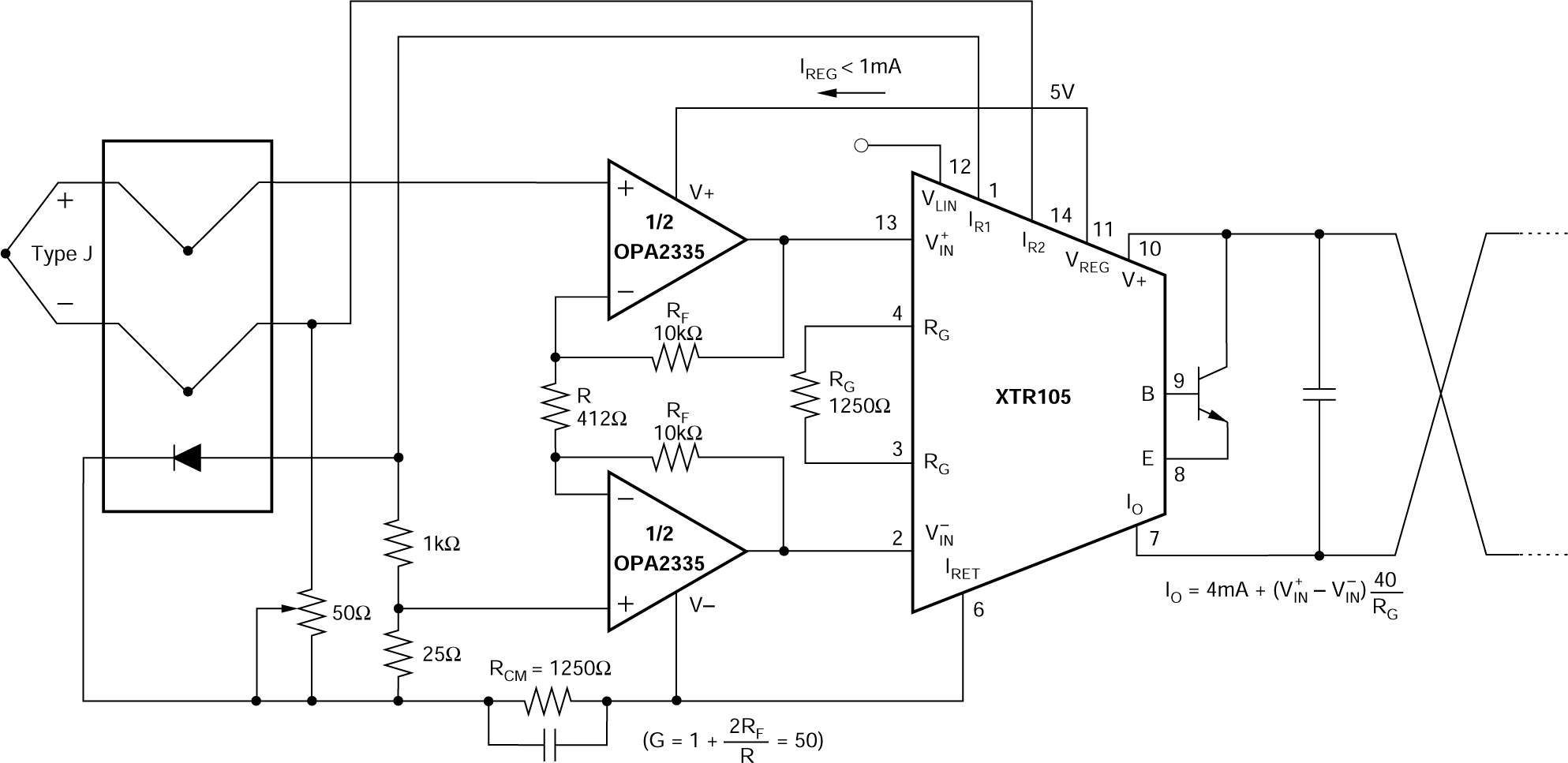

The VREG pin provides an on-chip voltage source of approximately 5.1V and is designed for powering external input circuitry (as shown in Figure 6-2). This source is a moderately accurate voltage reference, and is not the same reference used to set the 800µA current references. VREG is capable of sourcing approximately 1mA of current. Exceeding 1mA can affect the 4mA zero output.

Figure 6-2 Thermocouple Low Offset, Low

Drift Loop Measurement With Diode Cold Junction Compensation

Figure 6-2 Thermocouple Low Offset, Low

Drift Loop Measurement With Diode Cold Junction Compensation