-

bq24193 I2C Controlled 4.5-A Single Cell USB/Adapter Charger with Narrow VDC Power Path Management and USB OTG

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (Continued)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Device Power Up

- 8.3.2 Power Path Management

- 8.3.3 Battery Charging Management

- 8.3.4 Status Outputs (PG, STAT, and INT)

- 8.3.5 Protections

- 8.3.6 Serial Interface

- 8.4 Device Functional Modes

- 8.5

Register Map

- 8.5.1

I2C Registers

- 8.5.1.1 Input Source Control Register REG00 (reset = 00110000, or 30)

- 8.5.1.2 Power-On Configuration Register REG01 (reset = 00011011, or 1B)

- 8.5.1.3 Charge Current Control Register REG02 (reset = 01100000, or 60)

- 8.5.1.4 Pre-Charge/Termination Current Control Register REG03 (reset = 00010001, or 11)

- 8.5.1.5 Charge Voltage Control Register REG04 (reset = 10110010, or B2)

- 8.5.1.6 Charge Termination/Timer Control Register REG05 (reset = 10011010, or 9A)

- 8.5.1.7 IR Compensation / Thermal Regulation Control Register REG06 (reset = 00000011, or 03)

- 8.5.1.8 Misc Operation Control Register REG07 (reset = 01001011, or 4B)

- 8.5.1.9 System Status Register REG08

- 8.5.1.10 Fault Register REG09

- 8.5.1.11 Vender / Part / Revision Status Register REG0A (reset = 00101111, or 2F)

- 8.5.1

I2C Registers

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

Package Options

Mechanical Data (Package|Pins)

- RGE|24

Thermal pad, mechanical data (Package|Pins)

- RGE|24

Orderable Information

bq24193 I2C Controlled 4.5-A Single Cell USB/Adapter Charger with Narrow VDC Power Path Management and USB OTG

1 Features

- High Efficiency 4.5-A Switch Mode Charger

- 92% Charge Efficiency at 2 A, 90% at 4 A

- Accelerate Charge Time by Battery Path Impedance Compensatioin

- Highest Battery Discharge Efficiency with 12-mΩ Battery Discharge MOSFET up to 9-A Discharge Current

- Single Input USB-compliant/Adapter Charger

- USB Host or Charging Port D+/D- Detection Compatible to USB Battery Charger Spec 1.2

- Input Voltage and Current Limit Supports USB2.0 and USB3.0

- Input Current Limit: 100 mA, 150 mA, 500 mA, 900 mA, 1.2 A, 1.5 A, 2 A and 3 A

- 3.9-V to 17-V Input Operating Voltage Range

- Support All Kinds of Adapter with Input Voltage DPM Regulation

- USB OTG 5 V at 1.3 A Synchronous Boost Converter Operation

- 93% 5-V Boost Efficiency at 1 A

- Narrow VDC (NVDC) Power Path Management

- Instant-on Works with No Battery or Deeply Discharged Battery

- Ideal Diode Operation in Battery Supplement Mode

- 1.5-MHz Switching Frequency for Low Profile Inductor

- Autonomous Battery Charging with or without Host Management

- Battery Charge Enable

- Battery Charge Preconditioning

- Charge Termination and Recharge

- High Accuracy (0°C to 125°C)

- ±0.5% Charge Voltage Regulation

- ±7% Charge Current Regulation

- ±7.5% Input Current Regulation

- ±2% Output Regulation in Boost Mode

- High Integration

- Power Path Management

- Synchronous Switching MOSFETs

- Integrated Current Sensing

- Bootstrap Diode

- Internal Loop Compensation

- Safety

- Battery Temperature Sensing and Charging Safety Timer

- JEITA Guideline Compliant

- Thermal Regulation and Thermal Shutdown

- Input System Over-Voltage Protection

- MOSFET Over-Current Protection

- Charge Status Outputs for LED or Host Processor

- Low Battery Leakage Current and Support Shipping Mode

- 4.00 mm x 4.00 mm QFN-24 Package

2 Applications

- Tablet PC and Smart Phone

- Portable Audio Speaker

- Portable Media Players

- Internet Devices

3 Description

The bq24193 is a highly-integrated switch-mode battery charge management and system power path management device for single cell Li-Ion and Li-polymer batteries in a wide range of tablet and other portable devices.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| bq24193 | VQFN (24) | 4.00 mm x 4.00 mm |

- For all available packages, see the orderable addendum at the end of the datasheet.

bq24193 with PSEL, USB On-The-Go (OTG) and Support JEITA Profile

4 Revision History

Changes from * Revision (December 2014) to A Revision

- Changed VSLEEPZ MAX from 300 to 350 mVGo

- Changed VBAT_DPL_HY MAX from 230 mV to 260 mVGo

- Changed ICHG_20pct MAX from 125 to 135 mAGo

- Added ICHG_20pct at room temperatureGo

- Changed VSHORT TYP from 1.8 to 2.0 VGo

- Changed IADPT_DPM MIN from 1.4 to 1.35 AGo

- Changed IADPT_DPM MAX from 1.6 to 1.65 AGo

- Changed KILIM MIN from 440 to 435 A x ΩGo

- Changed VBTST_REFRESH, VBUS > 6 V TYP from 4.2 V to 4.5 VGo

- Changed VREGN, VVBUS = 5 V, IREGN = 20 mA MAXGo

- Changed value from: 4.85 V to: 5 VGo

5 Description (Continued)

Its low impedance power path optimizes switch-mode operation efficiency, reduces battery charging time and extends battery life during discharging phase. The I2C serial interface with charging and system settings makes the device a truly flexible solution.

The device supports a wide range of input sources, including standard USB host port, USB charging port and high power DC adapter. The bq24193 takes the result from detection circuit in the system, such as USB PHY device. The bq24193 is compliant with USB 2.0 and USB 3.0 power spec with input current and voltage regulation. Meanwhile, the bq24193 meets USB On-the-Go operation power rating specification by supplying 5 V on VBUS with current limit up to 1.3 A.

The power path management regulates the system slightly above battery voltage but does not drop below 3.5-V minimum system voltage (programmable). With this feature, the system maintains operation even when the battery is completely depleted or removed. When the input current limit or voltage limit is reached, the power path management automatically reduces the charge current to zero. As the system load continues to increase, the power path discharges the battery until the system power requirement is met. This supplement mode operation prevents overloading the input source.

The device initiates and completes a charging cycle without software control. It automatically detects the battery voltage and charges the battery in three phases: pre-conditioning, constant current and constant voltage. At the end of the charging cycle, the charger automatically terminates when the charge current is below a preset limit in the constant voltage phase. When the full battery falls below the recharge threshold, the charger will automatically start another charging cycle.

The device provide various safety features for battery charging and system operation, including dual pack negative thermistor monitoring, charging safety timer and over-voltage/over-current protections. The bq24193 also supports JEITA guideline compliant temperature profile. The thermal regulation reduces charge current when the junction temperature exceeds 120°C (programmable).

The STAT output reports the charging status and any fault conditions. The PG output in the bq24193 indicates if a good power source is present.The INT immediately notifies the host when a fault occurs.

The bq24193 is available in a 24-pin, 4.00 x 4.00 mm2 thin VQFN package.

6 Pin Configuration and Functions

Pin Functions

| PIN | TYPE | DESCRIPTION | |

|---|---|---|---|

| NAME | NUMBER | ||

| VBUS | 1,24 | P | Charger Input Voltage. The internal n-channel reverse block MOSFET (RBFET) is connected between VBUS and PMID with VBUS on source. Place a 1-µF ceramic capacitor from VBUS to PGND and place it as close as possible to IC. (Refer to Application Information Section for details) |

| PSEL | 2 | I Digital |

Power source selection input. High indicates a USB host source and Low indicates an adapter source. |

| PG | 3 | O Digital |

Open drain active low power good indicator. Connect to the pull up rail via 10-kΩ resistor. LOW indicates a good input source if the input voltage is between UVLO and ACOV, above SLEEP mode threshold, and current limit is above 30 mA. |

| STAT | 4 | O Digital |

Open drain charge status output to indicate various charger operation. Connect to the pull up rail via 10-kΩ. LOW indicates charge in progress. HIGH indicates charge complete or charge disabled. When any fault condition occurs, STAT pin blinks at 1 Hz. |

| SCL | 5 | I Digital |

I2C Interface clock. Connect SCL to the logic rail through a 10-kΩ resistor. |

| SDA | 6 | I/O Digital |

I2C Interface data. Connect SDA to the logic rail through a 10-kΩ resistor. |

| INT | 7 | O Digital |

Open-drain Interrupt Output. Connect the INT to a logic rail via 10-kΩ resistor. The INT pin sends active low, 256-us pulse to host to report charger device status and fault. |

| OTG | 8 | I Digital |

USB current limit selection pin during buck mode, and active high enable pin during boost mode. |

| In buck mode with USB host (PSEL=High), when OTG = High, IIN limit = 500 mA and when OTG = Low, IIN limit = 100 mA. | |||

| The boost mode is activated when the REG01[5:4] = 10 and OTG pin is High. | |||

| CE | 9 | I Digital |

Active low Charge Enable pin. Battery charging is enabled when REG01[5:4] = 01 and CE pin = Low. CE pin must be pulled high or low. |

| ILIM | 10 | I Analog |

ILIM pin sets the maximum input current limit by regulating the ILIM voltage at 1 V. A resistor is connected from ILIM pin to ground to set the maximum limit as IINMAX = (1V/RILIM) × 530. The actual input current limit is the lower one set by ILIM and by I2C REG00[2:0]. The minimum input current programmed on ILIM pin is 500 mA. |

| TS1 | 11 | I Analog |

Temperature qualification voltage input #1. Connect a negative temperature coefficient thermistor. Program temperature window with a resistor divider from REGN to TS1 to GND. Charge suspends when either TS pin is out of range. Recommend 103AT-2 thermistor. TS1 and TS2 pins have to be shorted together in bq24193. |

| TS2 | 12 | I Analog |

Temperature qualification voltage input #2. Connect a negative temperature coefficient thermistor. Program temperature window with a resistor divider from REGN to TS2 to GND. Charge suspends when either TS pin is out of range. Recommend 103AT-2 thermistor. TS1 and TS2 pins have to be connected together in bq24193. |

| BAT | 13,14 | P | Battery connection point to the positive terminal of the battery pack. The internal BATFET is connected between BAT and SYS. Connect a 10 µF closely to the BAT pin. |

| SYS | 15,16 | P | System connection point. The internal BATFET is connected between BAT and SYS. When the battery falls below the minimum system voltage, switch-mode converter keeps SYS above the minimum system voltage. (Refer to Application Information Section for inductor and capacitor selection.) |

| PGND | 17,18 | P | Power ground connection for high-current power converter node. Internally, PGND is connected to the source of the n-channel LSFET. On PCB layout, connect directly to ground connection of input and output capacitors of the charger. A single point connection is recommended between power PGND and the analog GND near the IC PGND pin. |

| SW | 19,20 | O Analog |

Switching node connecting to output inductor. Internally SW is connected to the source of the n-channel HSFET and the drain of the n-channel LSFET. Connect the 0.047-µF bootstrap capacitor from SW to BTST. |

| BTST | 21 | P | PWM high side driver positive supply. Internally, the BTST is connected to the anode of the boost-strap diode. Connect the 0.047-µF bootstrap capacitor from SW to BTST. |

| REGN | 22 | P | PWM low side driver positive supply output. Internally, REGN is connected to the cathode of the boost-strap diode. Connect a 4.7-µF (10-V rating) ceramic capacitor from REGN to analog GND. The capacitor should be placed close to the IC. REGN also serves as bias rail of TS1 and TS2 pins. |

| PMID | 23 | O Analog |

Connected to the drain of the reverse blocking MOSFET and the drain of HSFET. Given the total input capacitance, connect a 1-µF capacitor on VBUS to PGND, and the rest all on PMID to PGND. (Refer to Application Information Section for details) |

| Thermal Pad | – | P | Exposed pad beneath the IC for heat dissipation. Always solder thermal pad to the board, and have vias on the thermal pad plane star-connecting to PGND and ground plane for high-current power converter. |

7 Specifications

7.1 Absolute Maximum Ratings(1)

over operating free-air temperature range (unless otherwise noted)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Voltage range (with respect to GND) | VBUS | –2 | 22 | V |

| PMID | –0.3 | 22 | V | |

| STAT, PG | –0.3 | 20 | V | |

| BTST | –0.3 | 26 | V | |

| SW | –2 | 20 | V | |

| BAT, SYS (converter not switching) | –0.3 | 6 | V | |

| SDA, SCL, INT, OTG, ILIM, REGN, TS1, TS2, CE, PSEL | –0.3 | 7 | V | |

| BTST TO SW | –0.3 | –7 | V | |

| PGND to GND | –0.3 | –0.3 | V | |

| Output sink current | INT, STAT, PG | 6 | mA | |

| Junction temperature | –40°C | 150 | °C | |

| Storage temperature, Tstg | –65 | 150 | °C | |

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | 1000 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101(2) | 250 | |||

7.3 Recommended Operating Conditions

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VIN | Input voltage | 3.9 | 17(1) | V |

| IIN | Input current | 3 | A | |

| ISYS | Output current (SYS) | 4.5 | A | |

| VBAT | Battery voltage | 4.4 | V | |

| IBAT | Fast charging current | 4.5 | A | |

| Discharging current with internal MOSFET | 6 (continuous) 9 (peak) (up to 1 sec duration) |

A | ||

| TA | Operating free-air temperature range | –40 | 85 | °C |

7.4 Thermal Information

| THERMAL METRIC(1) | bq24193 | UNIT | |

|---|---|---|---|

| RGE (24 PIN) | |||

| RθJA | Junction-to-ambient thermal resistance | 32.2 | °C/W |

| RθJCtop | Junction-to-case (top) thermal resistance | 29.8 | |

| RθJB | Junction-to-board thermal resistance | 9.1 | |

| ψJT | Junction-to-top characterization parameter | 0.3 | |

| ψJB | Junction-to-board characterization parameter | 9.1 | |

| RθJCbot | Junction-to-case (bottom) thermal resistance | 2.2 | |

7.5 Electrical Characteristics

VVBUS_UVLOZ < VVBUS < VACOV and VVBUS > VBAT + VSLEEP, TJ = –40°C to 125°C and TJ = 25°C for typical values unless other noted.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| QUIESCENT CURRENTS | ||||||

| IBAT | Battery discharge current (BAT, SW, SYS) | VVBUS < VUVLO, VBAT = 4.2 V, leakage between BAT and VBUS | 5 | µA | ||

| High-Z Mode, or no VBUS, BATFET disabled (REG07[5] = 1), | 12 | 20 | µA | |||

| High-Z Mode, or no VBUS, REG07[5] = 0, –40°C to 85°C | 32 | 55 | µA | |||

| IVBUS | Input supply current (VBUS) | VVBUS = 5 V, High-Z mode | 15 | 30 | µA | |

| VVBUS = 17 V, High-Z mode | 30 | 50 | µA | |||

| VVBUS > VUVLO, VVBUS > VBAT, converter not switching | 1.5 | 3 | mA | |||

| VVBUS > VUVLO, VVBUS > VBAT, converter switching, VBAT = 3.2 V, ISYS = 0 A | 4 | mA | ||||

| VVBUS > VUVLO, VVBUS > VBAT, converter switching, VBAT = 3.8 V, ISYS = 0 A | 15 | mA | ||||

| IOTGBOOST | Battery discharge current in boost mode | VBAT = 4.2 V, Boost mode, IVBUS = 0 A, converter switching | 4 | mA | ||

| VBUS/BAT POWER UP | ||||||

| VVBUS_OP | VBUS operating range | 3.9 | 17 | V | ||

| VVBUS_UVLOZ | VBUS for active I2C, no battery | VVBUS rising | 3.6 | V | ||

| VSLEEP | Sleep mode falling threshold | VVBUS falling, VVBUS-VBAT | 35 | 80 | 120 | mV |

| VSLEEPZ | Sleep mode rising threshold | VVBUS rising, VVBUS-VBAT | 170 | 250 | 350 | mV |

| VACOV | VBUS over-voltage rising threshold | VVBUS rising | 17.4 | 18 | V | |

| VACOV_HYST | VBUS over-voltage falling hysteresis | VVBUS falling | 700 | mV | ||

| VBAT_UVLOZ | Battery for active I2C, no VBUS | VBAT rising | 2.3 | V | ||

| VBAT_DPL | Battery depletion threshold | VBAT falling | 2.4 | 2.6 | V | |

| VBAT_DPL_HY | Battery depletion rising hysteresis | VBAT rising | 170 | 260 | mV | |

| VVBUSMIN | Bad adapter detection threshold | VVBUS falling | 3.8 | V | ||

| IBADSRC | Bad adapter detection current source | 30 | mA | |||

| tBADSRC | Bad source detection duration | 30 | ms | |||

| POWER PATH MANAGEMENT | ||||||

| VSYS_RANGE | Typical system regulation voltage | Isys = 0 A, Q4 off, VBAT up to 4.2 V, REG01[3:1] = 101, VSYSMIN = 3.5 V |

3.5 | 4.35 | V | |

| VSYS_MIN | System voltage output | REG01[3:1] = 101, VSYSMIN = 3.5 V | 3.55 | 3.65 | V | |

| RON(RBFET) | Internal top reverse blocking MOSFET on-resistance | Measured between VBUS and PMID | 23 | 38 | mΩ | |

| RON(HSFET) | Internal top switching MOSFET on-resistance between PMID and SW | TJ = –40°C to 85°C | 27 | 35 | mΩ | |

| TJ = -40°C to 125°C | 27 | 45 | ||||

| RON(LSFET) | Internal bottom switching MOSFET on-resistance between SW and PGND | TJ = –40°C to 85°C | 32 | 45 | mΩ | |

| TJ = -40°C to 125°C | 32 | 48 | ||||

| VFWD | BATFET forward voltage in supplement mode | BAT discharge current 10 mA | 30 | mV | ||

| VSYS_BAT | SYS/BAT Comparator | VSYS falling | 90 | mV | ||

| VBATGD | Battery good comparator rising threshold | VBAT rising | 3.4 | 3.55 | 3.7 | V |

| VBATGD_HYST | Battery good comparator falling threshold | VBAT falling | 100 | mV | ||

| BATTERY CHARGER | ||||||

| VBAT_REG_ACC | Charge voltage regulation accuracy | VBAT = 4.112 V and 4.208 V | –0.5% | 0.5% | ||

| IICHG_REG_ACC | Fast charge current regulation accuracy | VBAT = 3.8 V, ICHG = 1792 mA, TJ = 25°C | –4% | 4% | ||

| VBAT = 3.8 V, ICHG = 1792 mA, TJ = –20°C to 125°C | –7% | 7% | ||||

| ICHG_20pct | Charge current with 20% option on | VBAT = 3.1 V, ICHG = 104 mA, REG02 = 03 | 75 | 100 | 135 | mA |

| ICHG_20pct | Charge current with 20% option on | VBAT = 3.1 V, ICHG = 104 mA, REG02 = 03, at room temperature | 130 | mA | ||

| VBATLOWV | Battery LOWV falling threshold | Fast charge to precharge, REG04[1] = 1 | 2.6 | 2.8 | 2.9 | V |

| VBATLOWV_HYST | Battery LOWV rising threshold | Precharge to fast charge, REG04[1] = 1 | 2.8 | 3.0 | 3.1 | V |

| IPRECHG_ACC | Precharge current regulation accuracy | VBAT = 2.6 V, ICHG = 256 mA | –20% | 20% | ||

| ITERM_ACC | Termination current accuracy | ITERM = 256 mA, ICHG = 960 mA | –20% | 20% | ||

| VSHORT | Battery Short Voltage | VBAT falling | 2.0 | V | ||

| VSHORT_HYST | Battery Short Voltage hysteresis | VBAT rising | 200 | mV | ||

| ISHORT | Battery short current | VBAT < 2.2V | 100 | mA | ||

| VRECHG | Recharge threshold below VBAT_REG | VBAT falling, REG04[0] = 0 | 100 | mV | ||

| tRECHG | Recharge deglitch time | VBAT falling, REG04[0] = 0 | 20 | ms | ||

| RON_BATFET | SYS-BAT MOSFET on-resistance | TJ = 25°C | 12 | 15 | mΩ | |

| TJ = –40°C to 125°C | 12 | 20 | ||||

| INPUT VOLTAGE/CURRENT REGULATION | ||||||

| VINDPM_REG_ACC | Input voltage regulation accuracy | –2% | 2% | |||

| IUSB_DPM | USB Input current regulation limit, VBUS = 5 V, current pulled from SW | USB100 | 85 | 100 | mA | |

| USB150 | 125 | 150 | mA | |||

| USB500 | 440 | 500 | mA | |||

| USB900 | 750 | 900 | mA | |||

| IADPT_DPM | Input current regulation accuracy | Input current limit 1.5 A | 1.35 | 1.5 | 1.65 | A |

| IIN_START | Input current limit during system start up | VSYS < 2.2 V | 100 | mA | ||

| KILIM | IIN = KILIM/RILIM | IINDPM = 1.5 A | 435 | 485 | 530 | A x Ω |

| BAT OVER-VOLTAGE PROTECTION | ||||||

| VBATOVP | Battery over-voltage threshold | VBAT rising, as percentage of VBAT_REG | 104% | |||

| VBATOVP_HYST | Battery over-voltage hysteresis | VBAT falling, as percentage of VBAT_REG | 2% | |||

| tBATOVP | Battery over-voltage deglitch time to disable charge | 1 | µs | |||

| THERMAL REGULATION AND THERMAL SHUTDOWN | ||||||

| TJunction_REG | Junction temperature regulation accuracy | REG06[1:0] = 11 | 115(1) | 120 | 125(1) | °C |

| TSHUT | Thermal shutdown rising temperature | Temperature increasing | 160 | °C | ||

| TSHUT_HYS | Thermal shutdown hysteresis | 30 | °C | |||

| Thermal shutdown rising deglitch | Temperature increasing delay | 1 | ms | |||

| Thermal shutdown falling deglitch | Temperature decreasing delay | 1 | ms | |||

| JEITA THERMISTER COMPARATOR (bq24193) | ||||||

| VT1 | T1 (0°C) threshold, Charge suspended T1 below this temperature. | VTS rising, As percentage to VREGN | 70.2% | 70.8% | 71.4% | |

| VT1_HYS | Charge back to ICHG/2 and 4.2 V above this temperature | Hysteresis, VTS falling | 0.6% | |||

| VT2 | T2 (10°C) threshold, Charge back to ICHG/2 and 4.2 V below this temperature | VTS rising, as percentage of VREGN | 68.0% | 68.6% | 69.2% | |

| VT2_HYS | Charge back to ICHG and 4.2 V above this temperature | Hysteresis, VTS falling | 0.8% | |||

| VT3 | T3 (45°C) threshold, Charge back to ICHG and 4.05 V above this temperature | VTS falling, as percentage of VREGN | 55.5% | 56.1% | 56.7% | |

| VT3_HYS | Charge back to ICHG and 4.2 V below this temperature | Hysteresis, VTS rising | 0.8% | |||

| VT5 | T5 (60°C) threshold, charge suspended above this temperature | VTS falling, as percentage of VREGN | 47.6% | 48.1% | 48.6% | |

| VT5_HYS | Charge back to ICHG and 4.05 V below this temperature | Hysteresis, VTS rising | 1.2% | |||

| CHARGE OVER-CURRENT COMPARATOR | ||||||

| IHSFET_OCP | HSFET over-current threshold | 5.3 | 7 | A | ||

| IBATFET_OCP | System over load threshold | 9 | A | |||

| CHARGE UNDER-CURRENT COMPARATOR (CYCLE-BY-CYCLE) | ||||||

| VLSFET_UCP | LSFET charge under-current falling threshold | From sync mode to non-sync mode | 100 | mA | ||

| PWM OPERATION | ||||||

| FSW | PWM Switching frequency, and digital clock | 1300 | 1500 | 1700 | kHz | |

| DMAX | Maximum PWM duty cycle | 97% | ||||

| VBTST_REFRESH | Bootstrap refresh comparator threshold | VBTST-VSW when LSFET refresh pulse is requested, VBUS = 5 V | 3.6 | V | ||

| VBTST-VSW when LSFET refresh pulse is requested, VBUS > 6 V | 4.5 | |||||

| BOOST MODE OPERATION | ||||||

| VOTG_REG | OTG output voltage | I(VBUS) = 0 | 5.00 | V | ||

| VOTG_REG_ACC | OTG output voltage accuracy | I(VBUS) = 0 | –2% | 2% | ||

| IOTG | OTG mode output current | REG01[0] = 0 | 0.5 | A | ||

| REG01[0] = 1 | 1.3 | A | ||||

| IOTG_HSZCP | HSFET under current falling threshold | 100 | mA | |||

| IRBFET_OCP | RBFET over-current threshold | REG01[0] = 1 | 1.4 | 1.8 | 2.7 | A |

| REG01[0] = 0 | 0.6 | 1.1 | 1.8 | |||

| REGN LDO | ||||||

| VREGN | REGN LDO output voltage | VVBUS = 10 V, IREGN = 40 mA | 5.6 | 6 | 6.4 | V |

| VVBUS = 5 V, IREGN = 20 mA | 4.75 | 4.8 | 5 | V | ||

| IREGN | REGN LDO current limit | VVBUS = 10 V, VREGN = 3.8 V | 50 | mA | ||

| LOGIC I/O PIN CHARACTERISTICS (OTG, CE, PSEL, STAT, PG) | ||||||

| VILO | Input low threshold | 0.4 | V | |||

| VIH | Input high threshold | 1.3 | V | |||

| VOUT_LO | Output low saturation voltage | Sink current = 5 mA | 0.4 | V | ||

| IBIAS | High level leakage current | Pull up rail 1.8 V | 1 | µA | ||

| I2C INTERFACE (SDA, SCL, INT) | ||||||

| VIH | Input high threshold level | VPULL-UP = 1.8 V, SDA and SCL | 1.3 | V | ||

| VIL | Input low threshold level | VPULL-UP = 1.8 V, SDA and SCL | 0.4 | V | ||

| VOL | Output low threshold level | Sink current = 5 mA | 0.4 | V | ||

| IBIAS | High-level leakage current | VPULL-UP = 1.8 V, SDA and SCL | 1 | µA | ||

| fSCL | SCL clock frequency | 400 | kHz | |||

| DIGITAL CLOCK AND WATCHDOG TIMER | ||||||

| fHIZ | Digital crude clock | REGN LDO disabled | 15 | 35 | 50 | kHz |

| fDIG | Digital clock | REGN LDO enabled | 1300 | 1500 | 1700 | kHz |

| tWDT | REG05[5:4] = 11 | REGN LDO enabled | 136 | 160 | sec | |

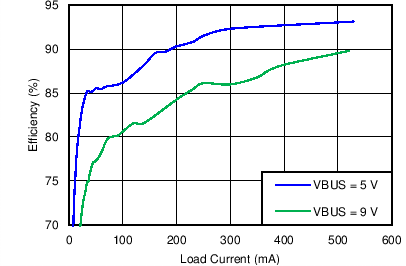

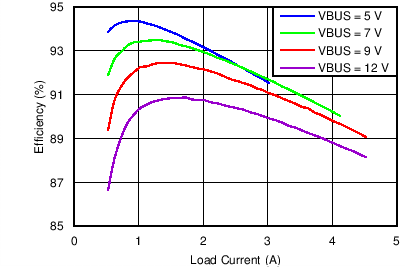

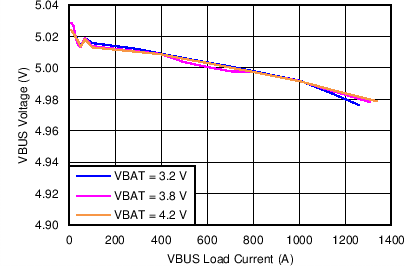

7.6 Typical Characteristics

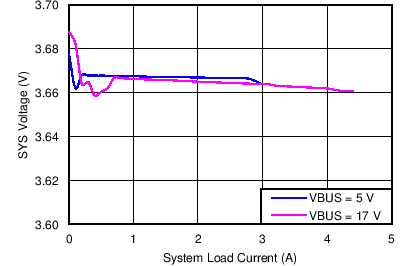

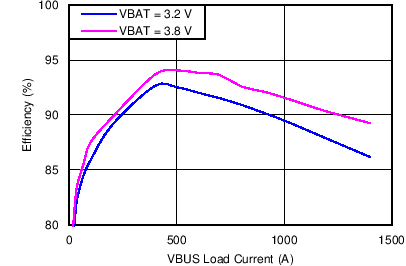

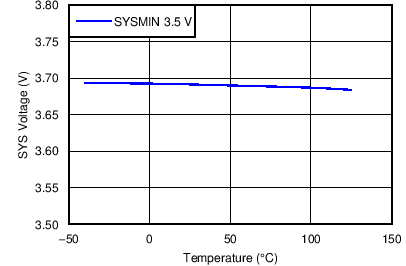

Table 1. Table of Figures

| FIGURE NUMBER | |

|---|---|

| System Light Load Efficiency vs System Load Current | Figure 1 |

| SYS Voltage Regulation vs System Load | Figure 2 |

| Charging Efficiency vs Charging Current | Figure 3 |

| Boost Mode Efficiency vs VBUS Load Current | Figure 4 |

| Boost Mode VBUS Voltage Regulation vs VBUS Load Current | Figure 5 |

| SYS Voltage vs Temperature | Figure 6 |

| BAT Voltage vs Temperature | Figure 7 |

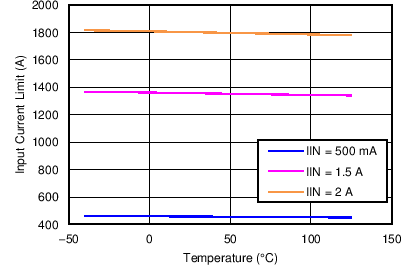

| Input Current Limit vs temperature | Figure 8 |

| Charge Current vs temperature | Figure 9 |