-

CDx4AC109 Dual J-K Positive-Edge-Triggered Flip-flops with Clear and Preset

- 1

- 1 Features

- 2 Description

- 3 Pin Configuration and Functions

-

4 Specifications

- 4.1 Absolute Maximum Ratings

- 4.2 ESD Ratings

- 4.3 Recommended Operating Conditions

- 4.4 Thermal Information

- 4.5 Electrical Characteristics

- 4.6 Timing Requirements

- 4.7 Timing Requirements

- 4.8 Timing Requirements

- 4.9 Switching Characteristics

- 4.10 Switching Characteristics

- 4.11 Switching Characteristics

- 4.12 Operating Characteristics

- 5 Parameter Measurement Information

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- N|16

- D|16

Thermal pad, mechanical data (Package|Pins)

CDx4AC109 Dual J-K Positive-Edge-Triggered Flip-flops with Clear and Preset

1 Features

- AC types feature 1.5V to 5.5V operation and balanced noise immunity at 30% of the supply voltage

- Speed of bipolar F, AS, and S, with significantly reduced power consumption

- Balanced propagation delays

- ±24mA output drive current

- Fanout to 15 F devices

- SCR-latchup-resistant CMOS process and circuit design

- Exceeds 2kV ESD protection per MIL-STD-883, method 3015

2 Description

The CD74AC109-Q1 device contains two independent J-K positive edge triggered flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the J and K inputs that meets the setup-time requirements is transferred to the outputs on the positive-going edge of the clock (CLK) pulse. The device is qualified for automotive applications.

Device

Information

| PART NUMBER | PACKAGE(1) | BODY SIZE(2) |

|---|---|---|

| CDx4AC109 | D (SOIC, 16) | 9.90mm x 3.90mm |

| N (PDIP, 16) | 19.3mm x 6.35mm | |

| J (CDIP, 16) | 19.56mm x 6.92mm |

(1) For more information, see Mechanical, Packaging,

and Orderable Information.

(2) The body size (length × width) is a

nominal value and does not include pins.

Logic

Diagram

Logic

Diagram3 Pin Configuration and Functions

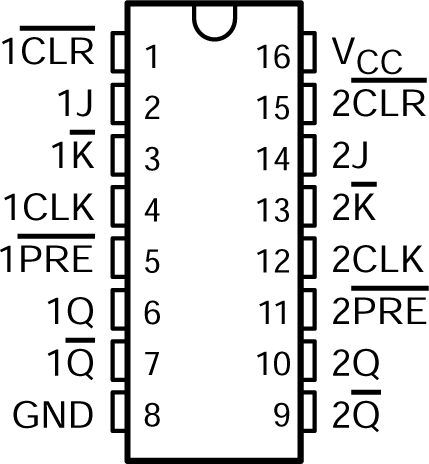

Figure 3-1 CD54AC109 J Package; CD74AC109

D or N Package; 16-Pin CDIP, SOIC or PDIP (Top View)

Figure 3-1 CD54AC109 J Package; CD74AC109

D or N Package; 16-Pin CDIP, SOIC or PDIP (Top View)Table 3-1 Pin Functions

| PIN | I/O(1) | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| 1CLR | 1 | I | Active low clear for first channel |

| 1J | 2 | I | J input for first channel |

| 1K | 3 | I | Active low K input for first channel |

| 1CLK | 4 | I | CLK input for first channel |

| 1PRE | 5 | I | Active low Preset input for first channel |

| 1Q | 6 | O | True Q output for first channel |

| 1Q | 7 | O | Inverted Q output for first channel |

| GND | 8 | - | Ground |

| 2Q | 9 | O | True Q output for second channel |

| 2Q | 10 | O | Inverted Q output for second channel |

| 2PRE | 11 | I | Active low preset for second channel |

| 2CLK | 12 | I | Clock input for second channel |

| 2K | 13 | I | Active low K input for second channel |

| 2J | 14 | I | J input for second channel |

| 2CLR | 15 | I | Active low clear for second channel |

| VCC | 16 | - | Power pin |

(1) I = input, O = output, P = power,

FB = feedback, GND = ground, N/A = not applicable