-

CSD19502Q5B 80 V N-Channel NexFET™ Power MOSFET

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- DNK|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

DATA SHEET

CSD19502Q5B 80 V N-Channel NexFET™ Power MOSFET

1 Features

- Ultra-Low Qg and Qgd

- Low Thermal Resistance

- Avalanche Rated

- Logic Level

- Pb-Free Terminal Plating

- RoHS Compliant

- Halogen Free

- SON 5-mm × 6-mm Plastic Package

2 Applications

- Secondary Side Synchronous Rectifier

- Motor Control

3 Description

This 3.4 mΩ, 80 V, SON 5 mm × 6 mm NexFET™ power MOSFET is designed to minimize losses in power conversion applications.

Top View

SPACE

SPACE

Product Summary

| TA = 25°C | TYPICAL VALUE | UNIT | ||

|---|---|---|---|---|

| VDS | Drain-to-Source Voltage | 80 | V | |

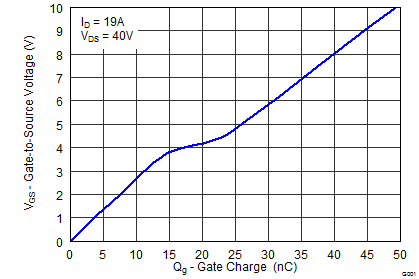

| Qg | Gate Charge Total (10 V) | 48 | nC | |

| Qgd | Gate Charge Gate to Drain | 8.6 | nC | |

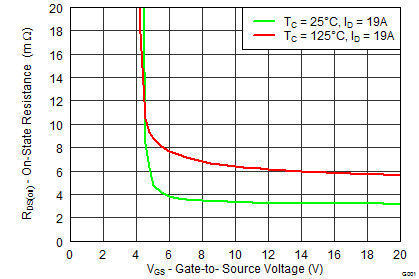

| RDS(on) | Drain-to-Source On Resistance | VGS = 6 V | 3.8 | mΩ |

| VGS = 10 V | 3.4 | mΩ | ||

| VGS(th) | Threshold Voltage | 2.7 | V | |

.

Ordering Information(1)

| Device | Media | Qty | Package | Ship |

|---|---|---|---|---|

| CSD19502Q5B | 13-Inch Reel | 2500 | SON 5 x 6 mm Plastic Package |

Tape and Reel |

| CSD19502Q5BT | 13-Inch Reel | 250 |

- For all available packages, see the orderable addendum at the end of the data sheet.

Absolute Maximum Ratings

| TA = 25°C | VALUE | UNIT | |

|---|---|---|---|

| VDS | Drain-to-Source Voltage | 80 | V |

| VGS | Gate-to-Source Voltage | ±20 | V |

| ID | Continuous Drain Current (Package limited) | 100 | A |

| Continuous Drain Current (Silicon limited), TC = 25°C | 157 | ||

| Continuous Drain Current(1) | 17 | ||

| IDM | Pulsed Drain Current(2) | 400 | A |

| PD | Power Dissipation(1) | 3.1 | W |

| Power Dissipation, TC = 25°C | 195 | ||

| TJ, Tstg |

Operating Junction and Storage Temperature Range |

–55 to 150 | °C |

| EAS | Avalanche Energy, single pulse ID = 74 A, L = 0.1 mH, RG = 25 Ω |

274 | mJ |

- Typical RθJA = 40°C/W on a 1-inch2, 2-oz. Cu pad on a 0.06-inch thick FR4 PCB.

- Max RθJC = 0.8°C/W, pulse duration ≤100 µs, duty cycle ≤1%

RDS(on) vs VGS |

Gate Charge |