JAJSGY4B May 2013 – February 2019 ADS8862

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

- 9 Parameter Measurement Information

- 10Detailed Description

- 11Application and Implementation

- 12Power Supply Recommendations

- 13Layout

- 14デバイスおよびドキュメントのサポート

- 15メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- DRC|10

発注情報

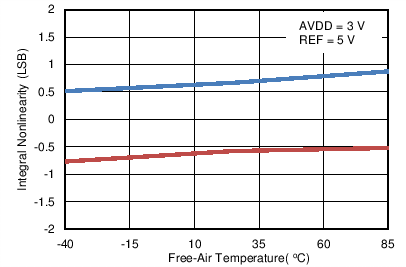

8.9 Typical Characteristics

at TA = 25°C, AVDD = 3 V, DVDD = 3 V, VREF = 5 V, and fSAMPLE = 680 kSPS (unless otherwise noted)

Nonlinearity (Minimum and Maximum)