Typical values at TA = +25°C, ADC

Sampling Rate = 2949.12 GHz. Default conditions: output sample rate = 491.52 MSPS

(decimate by 6), PLL clock mode with fREF = 491.52 MHz, AIN =

–3 dBFS, DSA setting = 4 dB.

| With

3.6 GHz matching, normalized to 3.6 GHz |

|

Figure 7-137 RX

In-Band Gain Flatness, fIN = 3600 MHz

| With

3.6 GHz matching |

| Differential Amplitude Error = PIN(DSA

Setting – 1) – PIN(DSA Setting) + 1 |

Figure 7-139 RX

Uncalibrated Differential Amplitude Error vs DSA Setting at 3.6 GHz

| With

3.6 GHz matching |

| Integrated Amplitude Error = PIN(DSA

Setting) – PIN(DSA Setting = 0) + (DSA

Setting) |

Figure 7-141 RX

Uncalibrated Integrated Amplitude Error vs DSA Setting at 3.6 GHz

| With

3.6 GHz matching |

| Differential Phase Error = PhaseIN(DSA

Setting – 1) – PhaseIN(DSA Setting) |

Figure 7-143 RX

Uncalibrated Phase Error vs DSA Setting at 3.6 GHz

| With

3.6 GHz matching |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 7-145 RX

Uncalibrated Integrated Phase Error vs DSA Setting at 3.6 GHz

| With

3.6 GHz matching , fIN = 3610 MHz,

AIN = –3 dBFS |

|

Figure 7-147 RX

Output FFT at 3.6 GHz

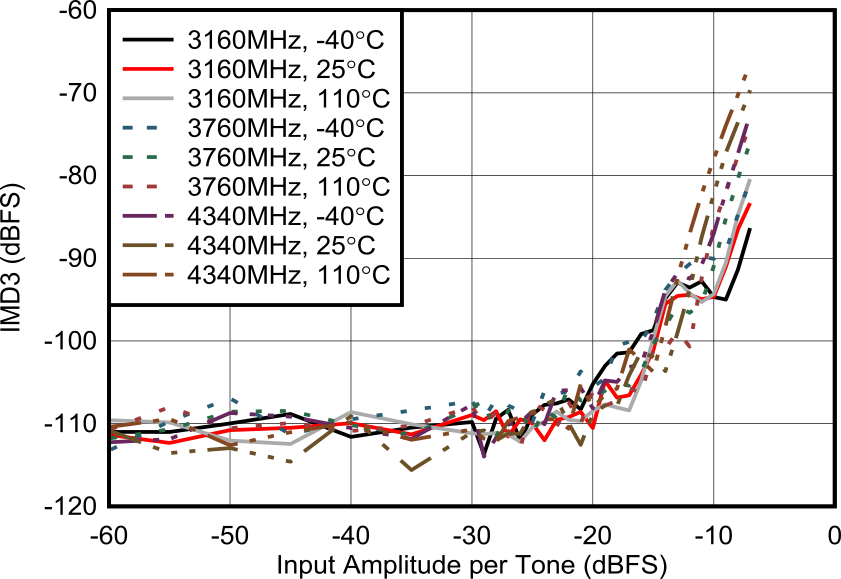

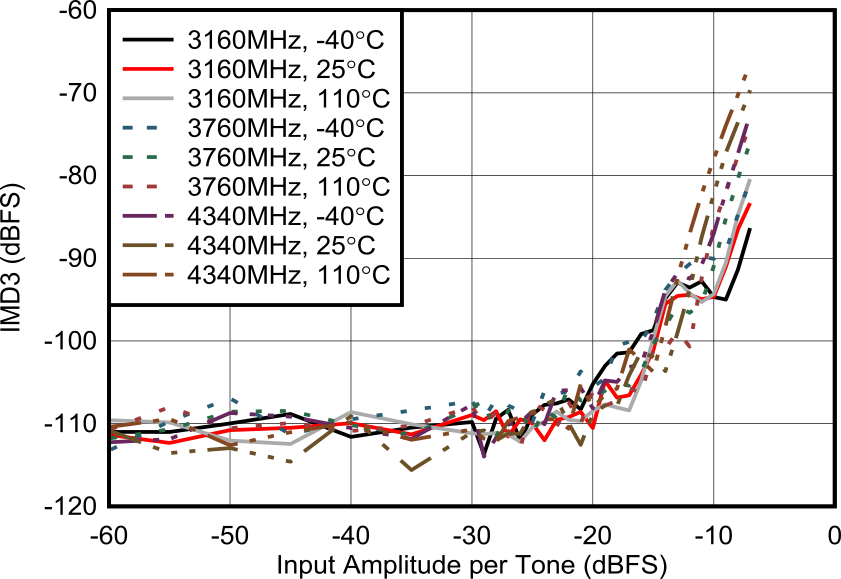

| With

3.5 GHz matching, 20-MHz tone spacing |

|

Figure 7-149 RX

IMD3 vs Input Level and Temperature at 3.6 GHz

| External clock mode, 2x Decimation |

|

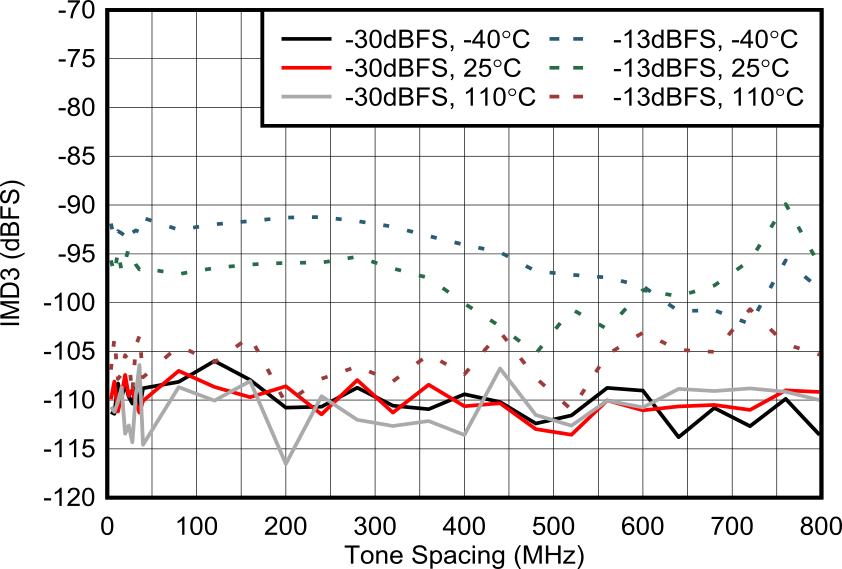

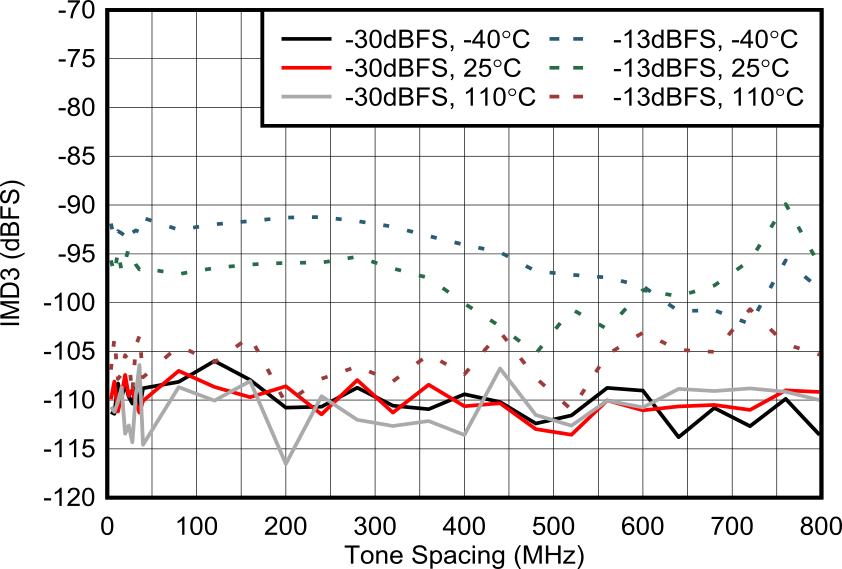

Figure 7-151 RX

IMD3 vs Tone Spacing at 3.76 GHz

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

Figure 7-153 RX

HD2 vs DSA Setting and Temperature at 3.6 GHz

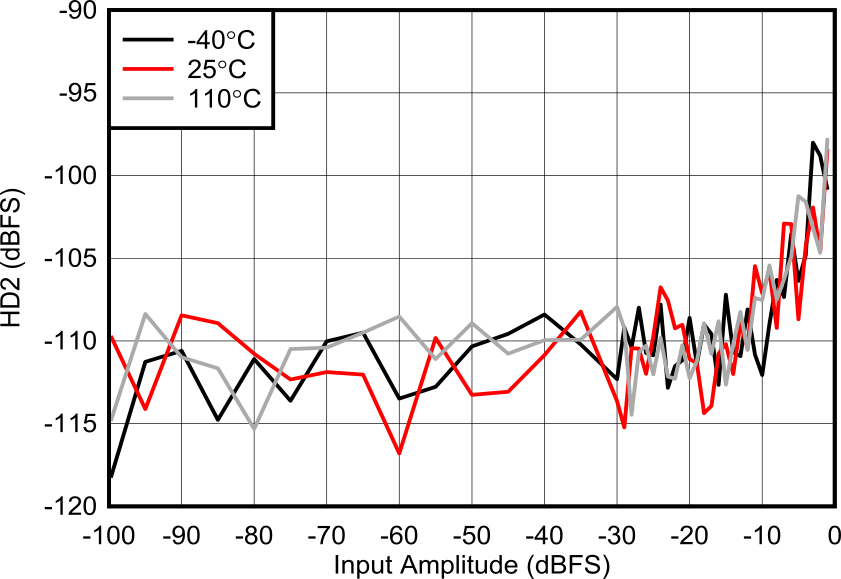

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

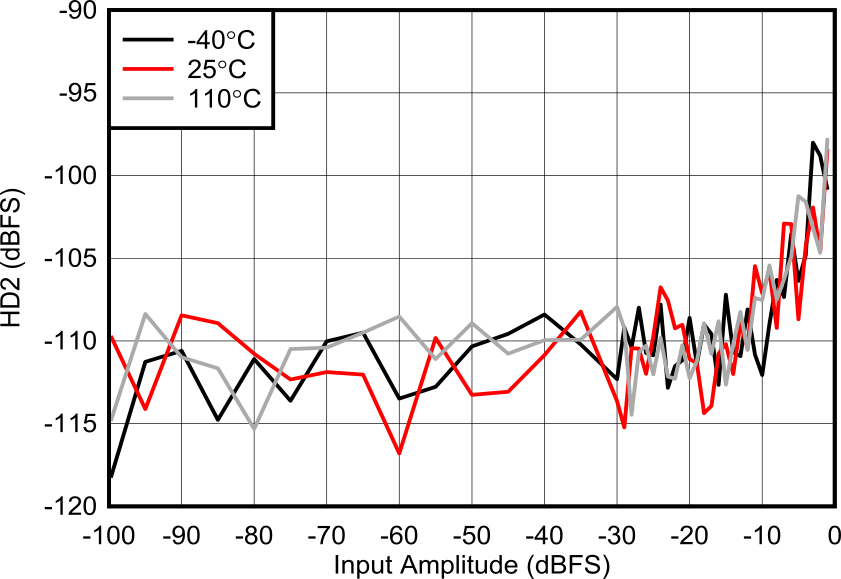

Figure 7-155 RX

HD2 vs Input Level and Temperature at 3.6 GHz

| External clock mode, 25°C, 2x Decimation |

Figure 7-157 RX

HD2 vs Input Level

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

Figure 7-159 RX

HD3 vs DSA Setting and Temperature at 3.6 GHz

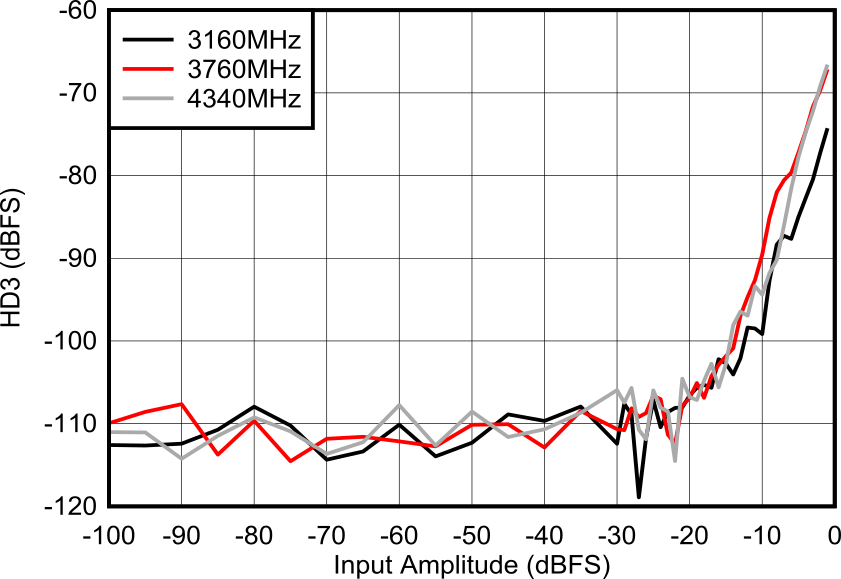

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

Figure 7-161 RX

HD3 vs Input Level and Temperature at 3.6 GHz

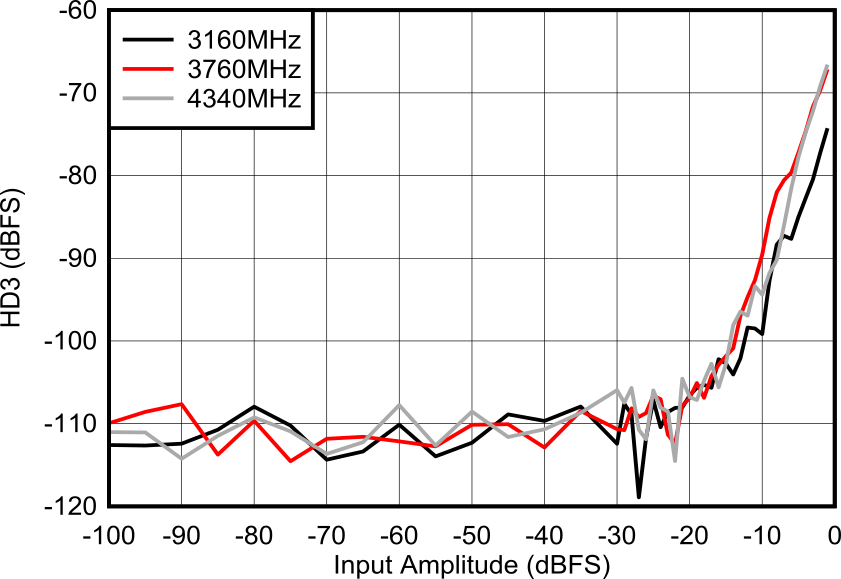

| External clock mode, 25°C, 2x Decimation |

Figure 7-163 RX

HD3 vs Input Level

| External clock mode, 25°C, 2x Decimation |

Figure 7-165 RX

Noise Spectral Density vs Input Level at 3.76GHz Figure 7-167 RX

SFDR Excluding HD2/3 vs DSA Setting and Channel at 3.6 GHz

Figure 7-167 RX

SFDR Excluding HD2/3 vs DSA Setting and Channel at 3.6 GHz

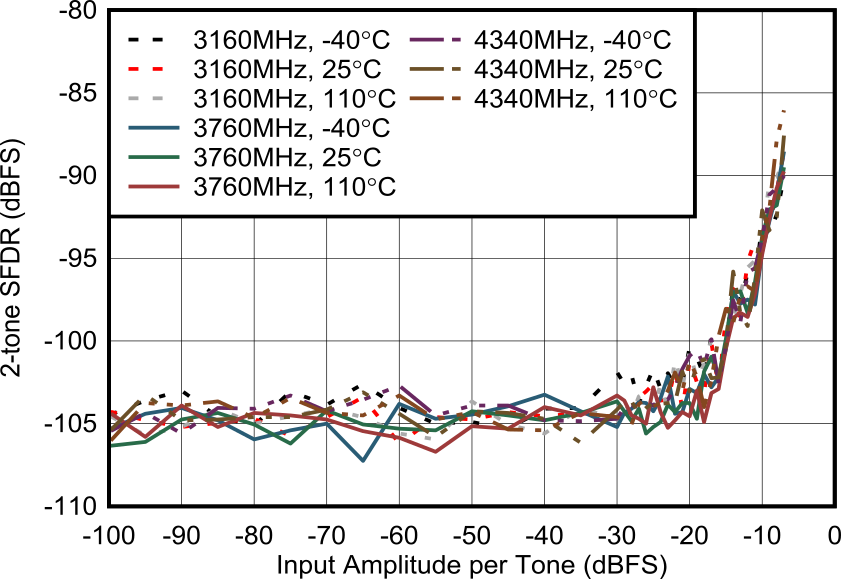

| External clock mode, 20MHz tone spacing, excluding

3rd order distortion |

Figure 7-169 RX

2-tone SFDR vs Input Amplitude and Frequency at 3.7 GHz

| With

3.6 GHz matching, –7 dBFS each tone, 20-MHz tone

spacing, all supplies at MIN, TYP, or MAX recommended

operating voltages |

Figure 7-171 RX

IMD5 vs Supply Voltage and Channel at 3.6 GHz

| With

3.6 GHz matching, normalized to phase at 25°C |

Figure 7-138 RX

Input Phase vs Temperature at 3.6 GHz

| With

3.6 GHz matching |

| Differential Amplitude Error = PIN(DSA

Setting – 1) – PIN(DSA Setting) + 1 |

Figure 7-140 RX

Calibrated Differential Amplitude Error vs DSA Setting at 3.6 GHz

| With

3.6 GHz matching |

| Integrated Amplitude Error = PIN(DSA

Setting) – PIN(DSA Setting = 0) + (DSA

Setting) |

Figure 7-142 RX

Calibrated Integrated Amplitude Error vs DSA Setting at 3.6 GHz

| With

3.6 GHz matching |

| Differential Phase Error = PhaseIN(DSA

Setting – 1) – PhaseIN(DSA Setting) |

Figure 7-144 RX

Calibrated Differential Phase Error vs DSA Setting at 3.6 GHz

| With

3.6 GHz matching |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 7-146 RX

Calibrated Integrated Phase Error vs DSA Setting at 3.6 GHz

| With

3.5 GHz matching, each tone at –7 dBFS, 20-MHz tone

spacing |

Figure 7-148 RX

IMD3 vs DSA Setting and Temperature at 3.6 GHz

| External clock mode, 20-MHz tone spacing, 2x

Decimation |

|

Figure 7-150 RX

IMD3 vs Input Level

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

Figure 7-152 RX

HD2 vs DSA Setting and Channel at 3.6 GHz

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

Figure 7-154 RX

HD2 vs Input Level and Channel at 3.6 GHz

| External clock mode, 2x Decimation |

Figure 7-156 RX

HD2 vs Input Level at 3.76 GHz

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

Figure 7-158 RX

HD3 vs DSA Setting and Channel at 3.6 GHz

| With

3.5 GHz matching, DDC bypass mode (TI only mode for

characterization) |

Figure 7-160 RX

HD3 vs Input Level and Channel at 3.6 GHz

| External clock mode, 2x Decimation |

Figure 7-162 RX

HD3 vs Input Level at 3.76 GHz

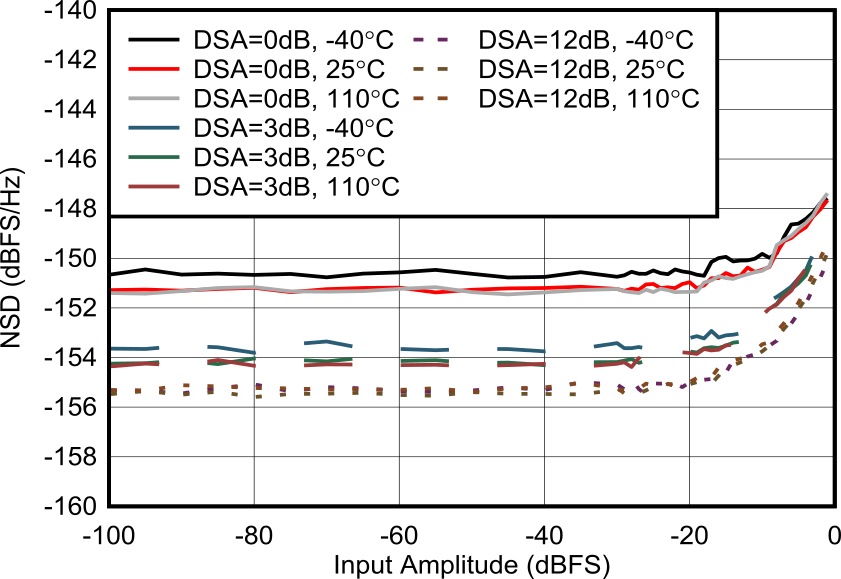

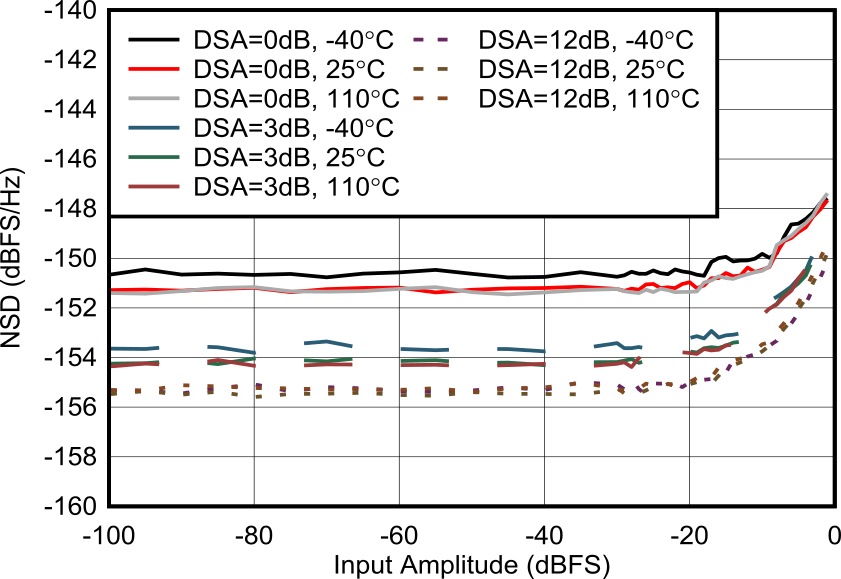

| With

3.5 GHz matching, 12.5-MHz offset from tone |

Figure 7-164 RX

Noise Spectral Density vs Input Level and DSA Setting at 3.6 GHz Figure 7-166 RX

In-Band SFDR (±200 MHz) vs Input Level and Channel at 3.6 GHz

Figure 7-166 RX

In-Band SFDR (±200 MHz) vs Input Level and Channel at 3.6 GHz

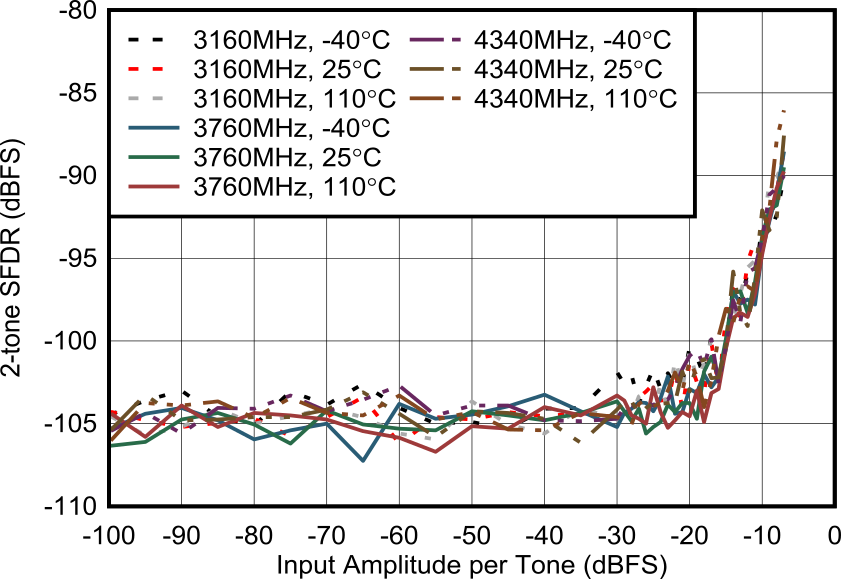

| External clock mode, 20MHz tone spacing, excluding

3rd order distortion |

Figure 7-168 RX

2-tone SFDR vs Input Amplitude and DSA Setting at 3.7 GHz

| With

3.6 GHz matching, –7 dBFS each tone, 20-MHz tone

spacing, all supplies at MIN, TYP, or MAX recommended

operating voltages |

Figure 7-170 RX

IMD3 vs Supply Voltage and Channel at 3.6 GHz

| With

3.6 GHz matching, tone at –20 dBFS, 12.5-MHz offset

frequency, all supplies at MIN, TYP, or MAX recommended

operating voltages |

Figure 7-172 RX

Noise Spectral Density vs Supply Voltage and Channel at 3.6 GHz