JAJSQU7B July 2023 – June 2024 AWRL1432

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 機能ブロック図

- 5 Device Comparison

- 6 Terminal Configurations and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Power-On Hours (POH)

- 7.4 Recommended Operating Conditions

- 7.5 VPP Specifications for One-Time Programmable (OTP) eFuses

- 7.6

Power Supply Specifications

- 7.6.1 Power Optimized 3.3V I/O Topology

- 7.6.2 BOM Optimized 3.3V I/O Topology

- 7.6.3 Power Optimized 1.8V I/O Topology

- 7.6.4 BOM Optimized 1.8V I/O Topology

- 7.6.5 System Topologies

- 7.6.6 Internal LDO output decoupling capacitor and layout conditions for BOM optimized topology

- 7.6.7 Noise and Ripple Specifications

- 7.7 Power Save Modes

- 7.8 Peak Current Requirement per Voltage Rail

- 7.9 RF Specification

- 7.10 Supported Front End features

- 7.11 CPU Specifications

- 7.12 Thermal Resistance Characteristics

- 7.13

Timing and Switching Characteristics

- 7.13.1 Power Supply Sequencing and Reset Timing

- 7.13.2 Synchronized Frame Triggering

- 7.13.3 Input Clocks and Oscillators

- 7.13.4 MultiChannel buffered / Standard Serial Peripheral Interface (McSPI)

- 7.13.5 RDIF Interface Configuration

- 7.13.6 LIN

- 7.13.7 General-Purpose Input/Output

- 7.13.8 Controller Area Network - Flexible Data-rate (CAN-FD)

- 7.13.9 Serial Communication Interface (SCI)

- 7.13.10 Inter-Integrated Circuit Interface (I2C)

- 7.13.11 Quad Serial Peripheral Interface (QSPI)

- 7.13.12 JTAG Interface

-

8 Detailed Description

- 8.1 Overview

- 8.2 機能ブロック図

- 8.3 Subsystems

- 8.4 Other Subsystems

- 8.5 Memory Partitioning Options

- 8.6 Boot Modes

- 9 Monitoring and Diagnostics

- 10Applications, Implementation, and Layout

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

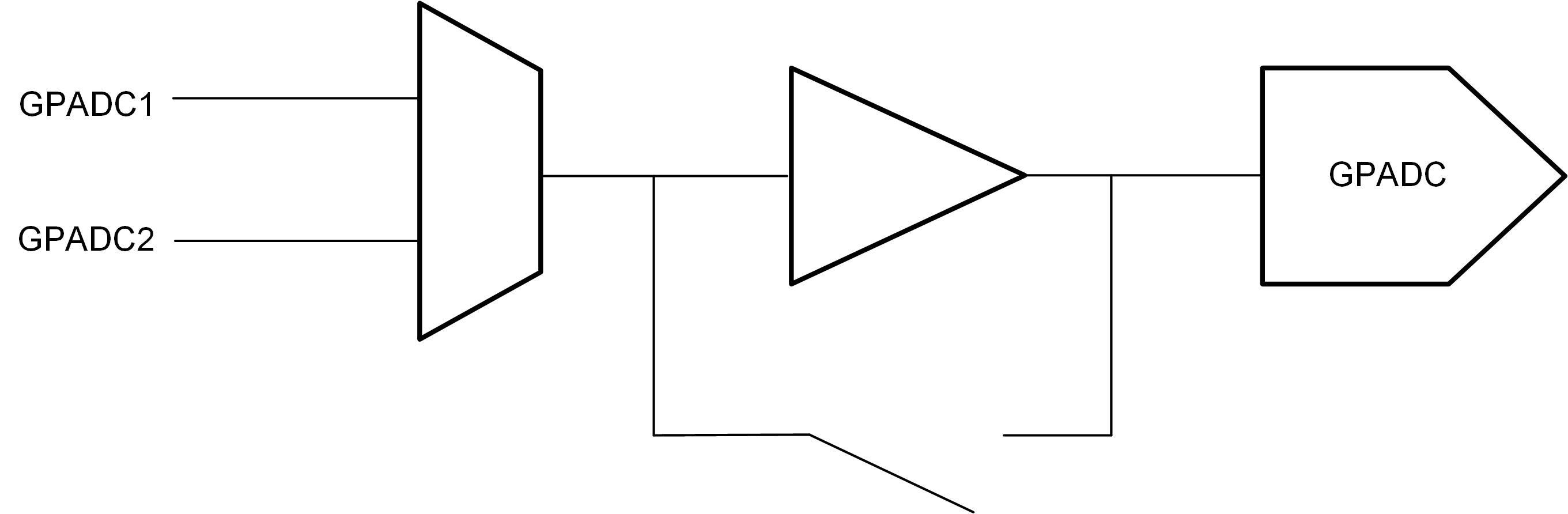

8.4.1 GPADC Channels (Service) for User Application

The AWRL1432 device includes provision for an ADC service for user application, where the GPADC engine present inside the device can be used to measure up to two external voltages. The GPADC1, and GPADC2 pins are used for this purpose.

- GPADC itself is controlled by TI firmware running inside the FEC subsystem and access to it for customer’s external voltage monitoring purpose is via ‘APPSS’ calls routed to the FEC subsystem. This API could be linked with the user application running on APPSS Cortex M4F®.

- Device Firmware package (DFP) provides APIs to configure and measure these signals. The API allows configuring the settling time (number of ADC samples to skip) and number of consecutive samples to take. At the end of a frame, the minimum, maximum and average of the readings will be reported for each of the monitored voltages.

Figure 8-7 GPADC Path

Figure 8-7 GPADC PathGPADC structures are used for measuring the output of internal temperature sensors. The accuracy of these measurements is ±7°C.