JAJSFD8A September 2016 – May 2018 BQ25890H

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Functional Block Diagram

- 8.2

Feature Description

- 8.2.1 Device Power-On-Reset (POR)

- 8.2.2 Device Power Up from Battery without Input Source

- 8.2.3 Device Power Up from Input Source

- 8.2.4 Input Current Optimizer (ICO)

- 8.2.5 Boost Mode Operation from Battery

- 8.2.6 Power Path Management

- 8.2.7 Battery Charging Management

- 8.2.8 Battery Monitor

- 8.2.9 Status/Control Outputs (STAT, INT and DSEL)

- 8.2.10 BATET (Q4) Control

- 8.2.11 Current Pulse Control Protocol

- 8.2.12 D+/D- Output Driver

- 8.2.13 Input Current Limit on ILIM

- 8.2.14 Thermal Regulation and Thermal Shutdown

- 8.2.15 Voltage and Current Monitoring in Buck and Boost Mode

- 8.2.16 Battery Protection

- 8.2.17 Serial Interface

- 8.3 Device Functional Modes

- 8.4 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RTW|24

サーマルパッド・メカニカル・データ

- RTW|24

発注情報

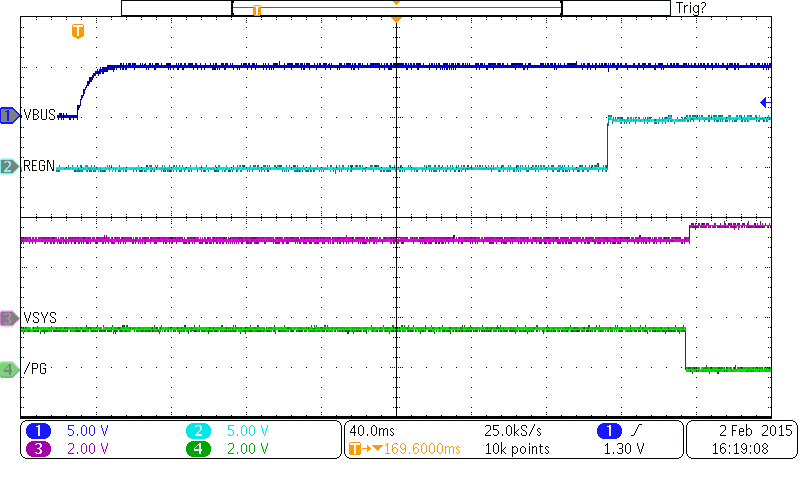

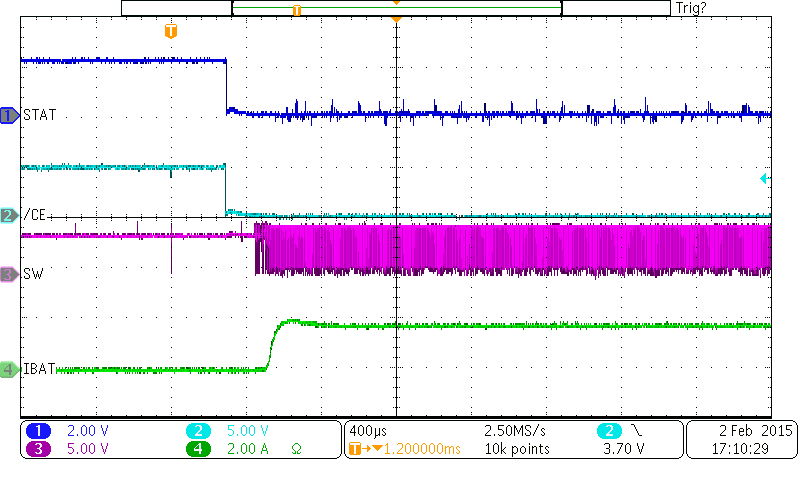

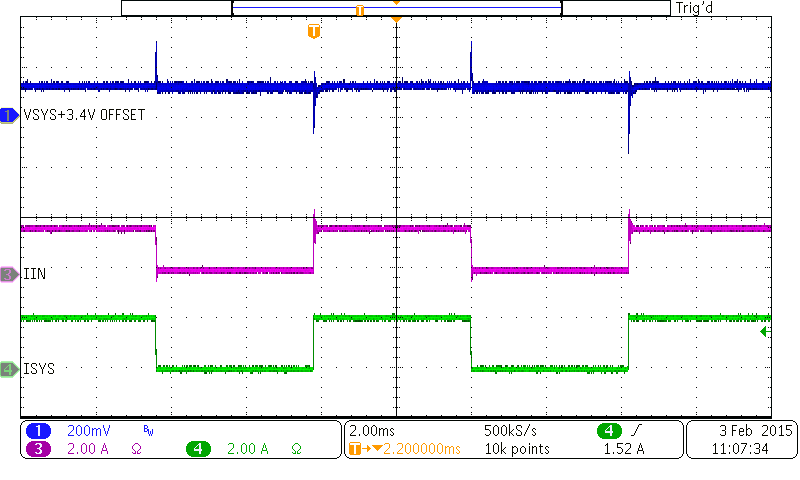

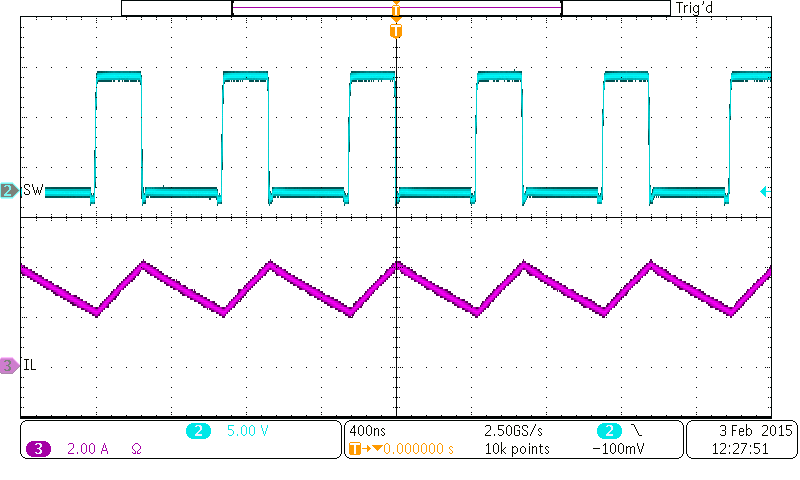

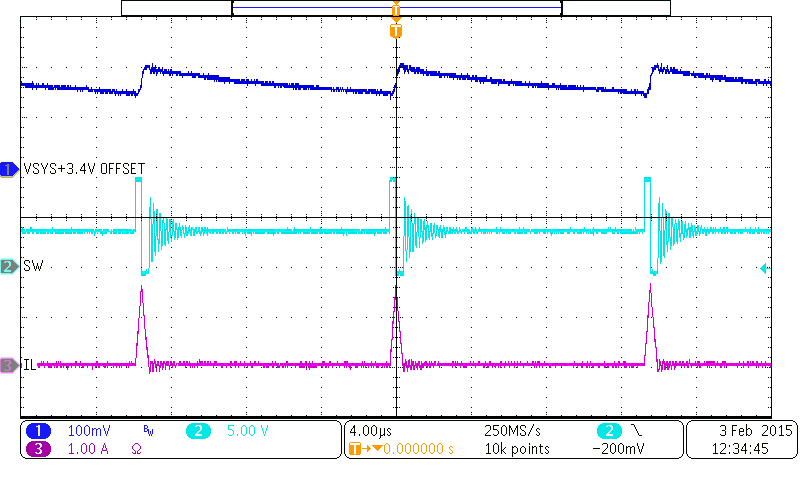

9.2.3 Application Curves

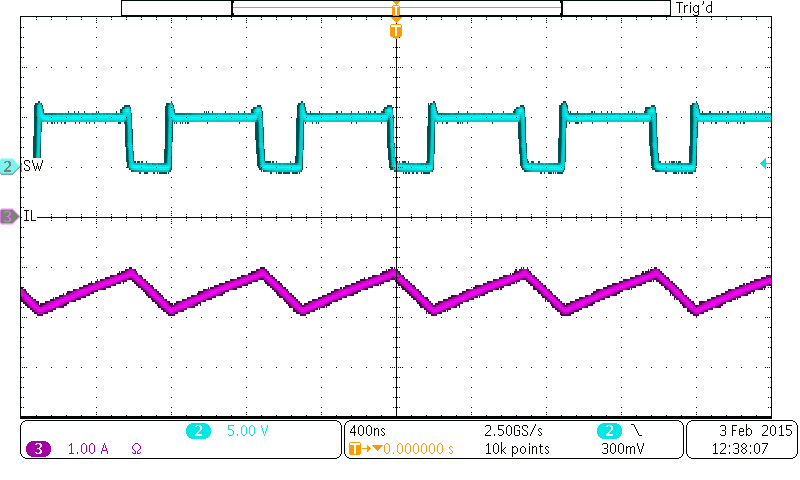

| VBAT = 3.2 V | ||

| VBUS = 5 V | ||

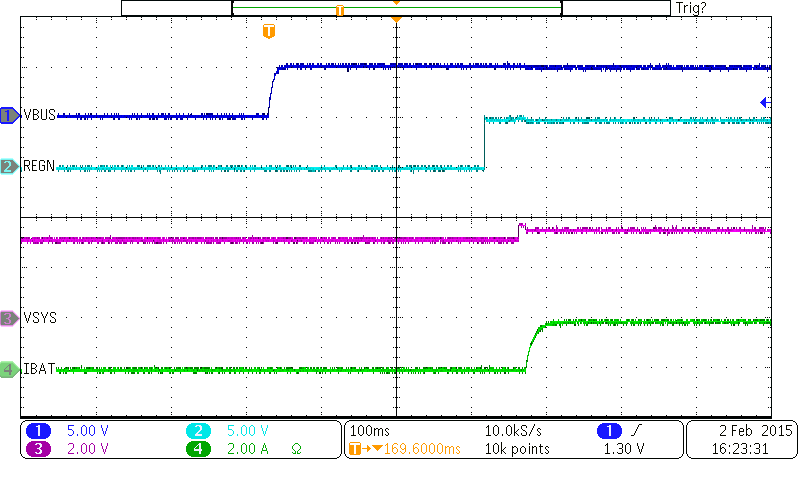

| VBUS = 5 V | IIN = 3 A | Charge Disable |

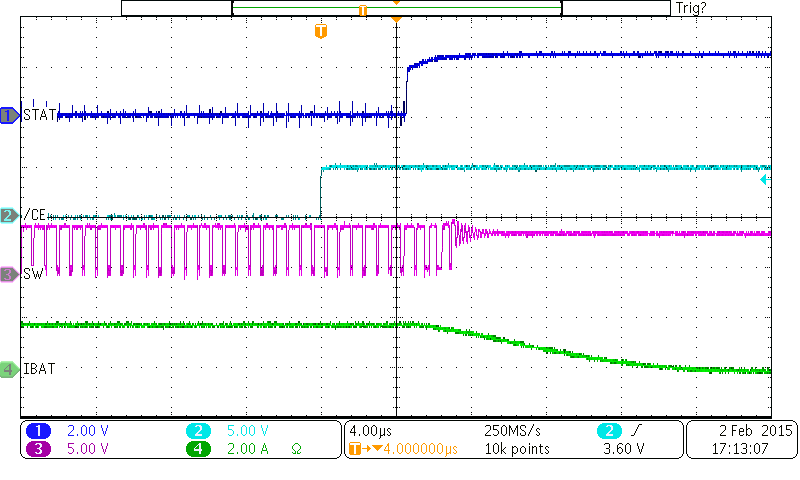

| VBUS = 12 V | VBAT = 3.8 V | ICHG = 3 A |

| VBAT = 3.8 V | ILOAD = 1 A | |

| VBUS = 12 V | ||

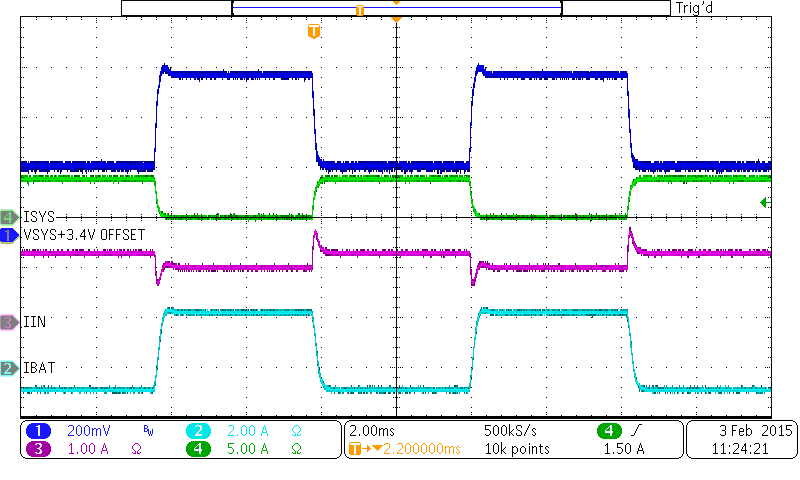

| VBUS = 9 V | IIN = 1.5 A | VBAT = 3.8 V |

| ICHG = 2 A | ISYS = 0 A - 4 A |

| VBUS = 9V | ISYS = 10 mA, | Charge Disable |

| No Battery |

| VBAT = 3.8 V | ILOAD = 0 A - 1 A | |