SLUSA92D January 2011 – May 2015

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Simplified Schematic

- 5 Revision History

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Supply Current

- 7.6 Power-On Reset (POR)

- 7.7 WAKE FROM SLEEP

- 7.8 RBI RAM Backup

- 7.9 3.3-V Regulator

- 7.10 2.5-V Regulator

- 7.11 DISP, PRES, SMBD, SMBC

- 7.12 CHG, DSG FET Drive

- 7.13 Internal Precharge Limiting

- 7.14 GPOD

- 7.15 FUSE

- 7.16 LED5, LED4, LED3, LED2, LED1

- 7.17 Coulomb Counter

- 7.18 VC1, VC2, VC3, VC4

- 7.19 TS1, TS2

- 7.20 Internal Temperature Sensor

- 7.21 Internal Thermal Shutdown

- 7.22 High Frequency Oscillator

- 7.23 Low Frequency Oscillator

- 7.24 Internal Voltage Reference

- 7.25 Flash

- 7.26 OCD Current Protection

- 7.27 SCD1 Current Protection

- 7.28 SCD2 Current Protection

- 7.29 SCC Current Protection

- 7.30 SBS Timing Requirements

- 7.31 Typical Characteristics

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||||

|---|---|---|---|---|---|---|---|

| Supply voltage | VCC, PACK, PCHGIN, PCR | 25 | V | ||||

| BAT | 3.8 | VVC2 + 5.0 | |||||

| VSTARTUP | Start up voltage at PACK | 3.0 | 5.5 | V | |||

| VIN | Input voltage range | VC1, BAT | VVC2 | VVC2 + 5.0 | V | ||

| VC2 | VVC3 | VVC3 + 5.0 | |||||

| VC3 | VVC4 | VVC4 + 5.0 | |||||

| VC4 | VSRP | VSRP + 5.0 | |||||

| VCn – VC(n+1), (n=1, 2, 3, 4) | 0 | 5.0 | |||||

| PACK | 25 | ||||||

| SRP to SRN | –0.2 | 0.2 | |||||

| CREG33 | External 3.3V REG capacitor | 1 | µF | ||||

| CREG25 | External 2.5V REG capacitor | 1 | µF | ||||

| TOPR | Operating temperature | –40 | 85 | °C | |||

7.4 Thermal Information

| THERMAL METRIC | bq3050 | UNIT | |

|---|---|---|---|

| TSSOP (DBT) | |||

| 38 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 64.2 | °C/W |

| RθJC(top) | Junction-to-case(top) thermal resistance | 16.5 | |

| RθJB | Junction-to-board thermal resistance | 31.2 | |

| ψJT | Junction-to-top characterization parameter | 0.3 | |

| ψJB | Junction-to-board characterization parameter | 26.9 | |

| RθJC(bot) | Junction-to-case(bottom) thermal resistance | n/a | |

7.5 Supply Current

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ICC | Normal | CHG on, DSG on, no Flash write | 410 | µA | ||

| Sleep | CHG on, DSG on, no SBS communication | 160 | ||||

| CHG off, DSG off, no SBS communication | 80 | |||||

| Shutdown | 3.7 | |||||

7.6 Power-On Reset (POR)

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIT– | Negative-going voltage input | At REG25 | 1.9 | 2.0 | 2.1 | V |

| VHYS | POR Hysteresis | At REG25 | 65 | 125 | 165 | mV |

7.7 WAKE FROM SLEEP

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VWAKE | VWAKE Threshold | VWAKE | 0.2 | 1.2 | 2.0 | mV |

| VWAKE | 0.4 | 2.4 | 3.6 | |||

| VWAKE | 2.0 | 5.0 | 6.8 | |||

| VWAKE | 5.3 | 10 | 13 | |||

| VWAKE_TCO | Temperature drift of VWAKE accuracy | 0.5% | °C | |||

| tWAKE | Time from application of current and wake of bq3050 | 0.2 | 1 | ms | ||

7.8 RBI RAM Backup

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| I(RBI) | RBI data-retention input current | VRBI > V(RBI)MIN, VCC < VIT | 20 | 1100 | nA | |

| VRBI > V(RBI)MIN, VCC < VIT, TA= 0°C to 70°C |

500 | |||||

| V(RBI) | RBI data-retention voltage | 1 | V | |||

7.9 3.3-V Regulator

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VREG33 | Regulator output voltage | 3.8 V < VCC or BAT ≤ 5 V, ICC ≤4 mA |

2.4 | 3.5 | V | |

| 5V < VCC or BAT ≤ 6.8 V, ICC ≤13 mA |

3.1 | 3.3 | 3.5 | |||

| 6.8 V < VCC or BAT ≤ 20 V, ICC ≤ 30 mA |

3.1 | 3.3 | 3.5 | |||

| IREG33 | Regulator output current | 2 | mA | |||

| ΔV(VDDTEMP) | Regulator output change with temperature | VCC or BAT = 14.4 V, IREG33 = 2 mA | 0.2% | |||

| ΔV(VDDLINE) | Line regulation | VCC or BAT = 14.4 V, IREG33 = 2 mA | 1 | 13 | mV | |

| ΔV(VDDLOAD) | Load regulation | VCC or BAT = 14.4 V, IREG33 = 2 mA | 5 | 18 | mV | |

| I(REG33MAX) | Current limit | VCC or BAT = 14.4 V, VREG33 = 3 V | 70 | mA | ||

| VCC or BAT = 14.4 V, VREG33 = 0 V | 33 | |||||

7.10 2.5-V Regulator

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VREG25 | Regulator output voltage | IREG25 = 10 mA | 2.35 | 2.5 | 2.55 | V |

| IREG25 | Regulator Output Current | 3 | mA | |||

| ΔV(VDDTEMP) | Regulator output change with temperature | VCC or BAT = 14.4 V, IREG25 = 2 mA | 0.25% | |||

| ΔV(VDDLINE) | Line regulation | VCC or BAT = 14.4 V, IREG25 = 2 mA | 1 | 4 | mV | |

| ΔV(VDDLOAD) | Load regulation | VCC or BAT = 14.4 V, IREG25 = 2 mA | 20 | 40 | mV | |

| I(REG33MAX) | Current limit | VCC or BAT = 14.4 V, VREG25 = 2.3 V | 65 | mA | ||

| VCC or BAT = 14.4 V, VREG25 = 0 V | 23 | |||||

7.11 DISP, PRES, SMBD, SMBC

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIH | High-level input | DISP, PRES, SMBD, SMBC | 2.0 | V | ||

| VIL | Low-level input | DISP, PRES, SMBD, SMBC | 0.8 | V | ||

| VOL | Low-level output voltage | SMBD, SMBC | 0.4 | V | ||

| CIN | Input capacitance | DISP, PRES, SMBD, SMBC | 5 | pF | ||

| ILKG | Input leakage current | DISP, PRES, SMBD, SMBC | 1 | μA | ||

| IWPU | Weak Pull Up Current | PRES, VOH = VREG25 – 0.5 V | 60 | 120 | μA | |

| I(DISP) | DISP source currents | DISP active, DISP = VREG25 – 0.6 V | –3 | mA | ||

| ILKG(DISP) | DISP leakage current | DISP inactive | –0.22 | 0.22 | μA | |

| RPD(SMBx) | SMBC, SMBD Pull-Down | TA = –40 to 100˚C | 550 | 775 | 1000 | kΩ |

7.12 CHG, DSG FET Drive

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| V(FETON) | Output voltage, charge, and discharge FETs on | VO(FETONDSG) = V(DSG) – VPACK, VGS connect 10 MΩ, VCC 3.8 V to 8.4 V | 8.0 | 9.7 | 12 | V |

| VO(FETONDSG) = V(DSG) – VPACK, VGS connect 10 MΩ, VCC > 8.4 V | 9.0 | 11 | 12 | |||

| VO(FETONCHG) = V(CHG) – VBAT, VGS connect 10 MΩ, VCC 3.8 V to 8.4 V | 8.0 | 9.7 | 12 | |||

| VO(FETONCHG) = V(CHG) – VBAT, VGS connect 10 MΩ, VCC > 8.4 V | 9.0 | 11 | 12 | |||

| V(FETOFF) | Output voltage, charge and discharge FETs off | VO(FETOFFDSG) = V(DSG) – VPACK | –0.4 | 0.4 | V | |

| VO(FETOFFCHG) = V(CHG) – VBAT | –0.4 | 0.4 | ||||

| tr | Rise time | CL= 4700 pF RG= 5.1 kΩ VCC < 8.4 VDSG: VBAT to VBAT + 4 V VCHG: VPACK to VPACK + 4 V |

800 | 1400 | μs | |

| CL = 4700 pF RG = 5.1 kΩ VCC > 8.4 VDSG: VBAT to VBAT + 4 V VCHG: VPACK to VPACK + 4 V |

200 | 500 | ||||

| tf | Fall time | CL = 4700 pF RG = 5.1 kΩ VDSG: VBAT + VO(FETONDSG) to VBAT + 1 V VCHG: VPACK + VO(FETONCHG) to VPACK + 1 V |

80 | 200 | μs | |

7.13 Internal Precharge Limiting

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| IPCHGMAX | Maximum Precharge current | 3-cell and 4-cell configuration | 100 | mA | ||

| RPCHG_RDSON | Internal Precharge FET RDSON | VDS(PRECHG) ≥ 1 V, VCC < 8.4 V | 30 | 55 | 85 | Ω |

| VDS(PRECHG) ≥ 1 V, VCC ≥ 8.4 V | 15 | 30 | 55 | |||

7.14 GPOD

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VPU_GPOD | GPOD Pull-Up Voltage | VCC | V | |||

| VOL_GPOD | GPOD Output Voltage Low | IOL = 1 mA | 0.3 | V | ||

7.15 FUSE

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOH(FUSE) | High Level FUSE Output | VCC = 3.8 V to 9 V | 2.4 | 8.5 | V | |

| VCC = 9 V to 25 V | 7 | 8 | 9 | |||

| VIH(FUSE) | Weak pull-up current in off state(1) | 2.8 | V | |||

| 100 | nA | |||||

| tR(FUSE) | FUSE Output Rise Time | CL = 1 nF, VCC = 9 V to 25 V, VOH(FUSE) = 0 V to 5 V | 5 | 20 | μs | |

| ZO(FUSE) | FUSE Output Impedance | 2 | 5 | kΩ | ||

(1) Verified by design. Not production tested.

7.16 LED5, LED4, LED3, LED2, LED1

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| CIN | Input capacitance | 5 | pF | |||

| ILKG | Input leakage current | 1 | μA | |||

| IOL | Low-level output current | VOL = 0.4 V, 3 mA setting |

2.5 | 3.5 | 4.5 | mA |

| VOL = 0.4 V, 4 mA setting |

3.0 | 4.5 | 6.0 | |||

| VOL = 0.4 V, 5 mA setting |

3.5 | 5.5 | 7.5 | |||

| ILEDx | Current matching between LEDx | 0.1 | mA | |||

7.17 Coulomb Counter

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|

| Input voltage range | SRP – SRN | –0.20 | 0.25 | V | |

| Conversion time | Single conversion | 250 | ms | ||

| Resolution (no missing codes) | 16 | Bits | |||

| Effective resolution | Single conversion, signed | 15 | Bits | ||

| Offset error | Post calibrated | 10 | µV | ||

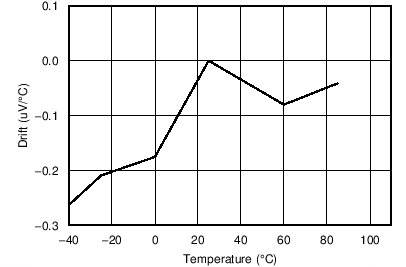

| Offset error drift | 0.3 | 0.5 | µV/°C | ||

| Full-scale error | –0.8% | 0.2% | 0.8% | ||

| Full-scale error drift | 150 | PPM/°C | |||

| Effective input resistance | 2.5 | mΩ |

7.18 VC1, VC2, VC3, VC4

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIN | Input voltage range | VC4 – VC3, VC3 – VC2, VC2 – VC1, VC1 – VSS | –0.20 | 8 | V | |

| Conversion time | Single conversion | 32 | ms | |||

| Resolution (no missing codes) | 16 | Bits | ||||

| Effective resolution | Single conversion, signed | 15 | Bits | |||

| R(BAL) | RDS(ON) for internal FET at VDS > 2 V | VDS = VC4 – VC3, VC3 – VC2, VC2 – VC1, VC1 – VSS |

200 | 310 | 430 | Ω |

| RDS(ON) for internal FET at VDS > 4 V | VDS = VC4 – VC3, VC3 – VC2, VC2 – VC1, VC1 – VSS |

60 | 125 | 230 | ||

7.19 TS1, TS2

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| R | Internal Pull Up Resistor | 16.5 | 17.5 | 19.0 | KΩ | |

| RDRIFT | Internal Pull Up Resistor Drift From 25°C | 200 | PPM/°C | |||

| RPAD | Internal Pin Pad resistance | 84 | Ω | |||

| VIN | Input voltage range | TS1 – VSS, TS2 – VSS | –0.20 | 0.8 × VREG25 | V | |

| Conversion Time | 16 | ms | ||||

| Resolution (no missing codes) | 16 | Bits | ||||

| Effective resolution | 11 | 12 | Bits | |||

7.20 Internal Temperature Sensor

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| V(TEMP) | Temperature sensor voltage | –1.9 | –2.0 | –2.1 | mV/°C | |

| Conversion Time | 16 | ms | ||||

| Resolution (no missing codes) | 16 | Bits | ||||

| Effective resolution | 11 | 12 | Bits | |||

7.21 Internal Thermal Shutdown

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| TMAX1 | Maximum PCHG temperature | 110 | 150 | °C | ||

| TMAX2 | Maximum REG33 temperature | 125 | 175 | °C | ||

| TRECOVER | Recovery hysteresis temperature | 10 | °C | |||

| tPROTECT | Protection time | 5 | µs | |||

7.22 High Frequency Oscillator

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| f(OSC) | Operating frequency of CPU Clock | 4.194 | MHz | |||

| f(EIO) | Frequency error(1)(2) | TA = –20°C to 70°C | –2% | ±0.25% | 2% | |

| TA = –40°C to 85°C | –3% | ±0.25% | 3% | |||

| t(SXO) | Start-up time(3) | TA = –25°C to 85°C | 3 | 6 | ms | |

(1) The frequency error is measured from 4.194 MHz.

(2) The frequency drift is included and measured from the trimmed frequency at VREG25 = 2.5 V, TA = 25°C.

(3) The startup time is defined as the time it takes for the oscillator output frequency to be ±3% when the device is already powered.

7.23 Low Frequency Oscillator

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| f(LOSC) | Operating frequency | 32.768 | kHz | |||

| f(LEIO) | Frequency error(1)(3) | TA = –20°C to 70°C | –1.5% | ±0.25% | 1.5% | |

| TA = –40°C to 85°C | –2.5% | ±0.25% | 2.5% | |||

| t(LSXO) | Start-up time(2) | TA = –25°C to 85°C | 100 | μs | ||

(1) The frequency drift is included and measured from the trimmed frequency at VCC = 2.5 V, TA = 25°C.

(2) The startup time is defined as the time it takes for the oscillator output frequency to be ±3%.

(3) The frequency error is measured from 32.768 kHz.

7.24 Internal Voltage Reference

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VREF | Internal Reference Voltage | 1.215 | 1.225 | 1.230 | V | |

| VREF_DRIFT | Internal Reference Voltage Drift | TA = –25°C to 85°C | ±80 | PPM/°C | ||

| TA = 0°C to 60°C | ±50 | |||||

7.25 Flash

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER(1) | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| Data retention | 10 | Year | ||||

| Flash programming write-cycles | Data Flash | 20k | Cycle | |||

| Instruction Flash | 1k | |||||

| ICC(PROG_DF) | Data Flash-write supply current | TA = –40°C to 85°C | 3 | 4 | mA | |

| ICC(ERASE_DF) | Data Flash-erase supply current | TA = –40°C to 85°C | 3 | 18 | mA | |

(1) Verified by design. Not production tested.

7.26 OCD Current Protection

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| V(OCD) | OCD detection threshold voltage range, typical | RSNS = 0 | 50 | 200 | mV | |

| RSNS = 1 | 25 | 100 | ||||

| ΔV(OCDT) | OCD detection threshold voltage program step | RSNS = 0 | 10 | mV | ||

| RSNS = 1 | 5 | |||||

| V(OFFSET) | OCD offset | –10 | 10 | mV | ||

| V(Scale_Err) | OCD scale error | –10% | 10% | |||

| t(OCDD) | Over Current in Discharge Delay | 1 | 31 | ms | ||

| t(OCDD_STEP) | OCDD Step options | 2 | ms | |||

| t(DETECT) | Current fault detect time | VSRP – SRN = VTHRESH + 12.5 mV | 160 | µs | ||

| tACC | Over Current and Short Circuit delay time accuracy | Accuracy of typical delay time | –20% | 20% | ||

7.27 SCD1 Current Protection

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| V(SDC1) | SCD1 detection threshold voltage range, typical | RSNS = 0 | 100 | 450 | mV | |

| RSNS = 1 | 50 | 225 | ||||

| ΔV(SCD1T) | SCD1 detection threshold voltage program step | RSNS = 0 | 50 | mV | ||

| RSNS = 1 | 25 | |||||

| V(OFFSET) | SCD1 offset | –10 | 10 | mV | ||

| V(Scale_Err) | SCD1 scale error | –10% | 10% | |||

| t(SCD1D) | Short Circuit in Discharge Delay | AFE.STATE_CNTL[SCDDx2] = 0 | 0 | 915 | µs | |

| AFE.STATE_CNTL[SCDDx2] = 1 | 0 | 1830 | ||||

| t(SCD1D_STEP) | SCD1D Step options | AFE.STATE_CNTL[SCDDx2] = 0 | 61 | µs | ||

| AFE.STATE_CNTL[SCDDx2] = 1 | 122 | |||||

| t(DETECT) | Current fault detect time | VSRP – SRN = VTHRESH + 12.5 mV | 160 | µs | ||

| tACC | Over Current and Short Circuit delay time accuracy | Accuracy of typical delay time | –20% | 20% | ||

7.28 SCD2 Current Protection

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| V(SDC2) | SCD2 detection threshold voltage range, typical | RSNS = 0 | 100 | 450 | mV | |

| RSNS = 1 | 50 | 225 | ||||

| ΔV(SCD2T) | SCD2 detection threshold voltage program step | RSNS = 0 | 50 | mV | ||

| RSNS = 1 | 25 | |||||

| V(OFFSET) | SCD2 offset | –10 | 10 | mV | ||

| V(Scale_Err) | SCD2 scale error | –10% | 10% | |||

| t(SCD1D) | Short Circuit in Discharge Delay | AFE.STATE_CNTL[SCDDx2] = 0 | 0 | 458 | µs | |

| AFE.STATE_CNTL[SCDDx2] = 1 | 0 | 915 | ||||

| t(SCD2D_STEP) | SCD2D Step options | AFE.STATE_CNTL[SCDDx2] = 0 | 30.5 | µs | ||

| AFE.STATE_CNTL[SCDDx2] = 1 | 61 | |||||

| t(DETECT) | Current fault detect time | VSRP – SRN = VTHRESH + 12.5 mV | 160 | µs | ||

| tACC | Over Current and Short Circuit delay time accuracy | Accuracy of typical delay time | –20% | 20% | ||

7.29 SCC Current Protection

Typical values stated where TA = 25ºC and VCC = 14.4 V, Min/Max values stated where TA= –40ºC to 85ºC and VCC = 3.8 V to 25 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| V(SCCT) | SCC detection threshold voltage range, typical | RSNS = 0 | –100 | –300 | mV | |

| RSNS = 1 | –50 | –225 | ||||

| ΔV(SCCDT) | SCC detection threshold voltage program step | RSNS = 0 | –50 | mV | ||

| RSNS = 1 | –25 | |||||

| V(OFFSET) | SCC offset | –10 | 10 | mV | ||

| V(Scale_Err) | SCC scale error | –10% | 10% | |||

| t(SCCD) | Short Circuit in Charge Delay | 0 | 915 | ms | ||

| t(SCCD_STEP) | SCCD Step options | 61 | ms | |||

| t(DETECT) | Current fault detect time | VSRP – SRN = VTHRESH + 12.5 mV | 160 | µs | ||

| tACC | Over Current and Short Circuit delay time accuracy | Accuracy of typical delay time | –20% | 20% | ||

7.30 SBS Timing Requirements

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| fSMB | SMBus operating frequency | Slave mode, SMBC 50% duty cycle | 10 | 100 | kHz | |

| fMAS | SMBus master clock frequency | Master mode, no clock low slave extend | 51.2 | kHz | ||

| tBUF | Bus free time between start and stop | 4.7 | µs | |||

| tHD:STA | Hold time after (repeated) start | 4.0 | µs | |||

| tSU:STA | Repeated start setup time | 4.7 | µs | |||

| tSU:STO | Stop setup time | 4.0 | µs | |||

| tHD:DAT | Data hold time | 300 | ns | |||

| tSU:DAT | Data setup time | 250 | ns | |||

| tTIMEOUT | Error signal/detect | See(1) | 25 | 35 | ms | |

| tLOW | Clock low period | 4.7 | µs | |||

| tHIGH | Clock high period | See(2) | Disabled | |||

| tHIGH | Clock high period | See(2) | 4.0 | 50 | µs | |

| tLOW:SEXT | Cumulative clock low slave extend time | See(3) | 25 | ms | ||

| tLOW:MEXT | Cumulative clock low master extend time | See(4) | 10 | ms | ||

| tF | Clock/data fall time | See(5) | 300 | ns | ||

| tR | Clock/data rise time | See(6) | 1000 | ns | ||

(1) The bq3050 times out when any clock low exceeds tTIMEOUT.

(2) tHIGH, Max, is the minimum bus idle time. SMBC = 1 for t > 50 µs causes reset of any transaction involving bq3050 that is in progress. This specification is valid when the THIGH_VAL=0. If THIGH_VAL = 1, then the value of THIGH is set by THIGH_1,2 and the timeout is not SMBus standard.

(3) tLOW:SEXT is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.

(4) tLOW:MEXT is the cumulative time a master device is allowed to extend the clock cycles in one message from initial start to the stop.

(5) Rise time tR = VILMAX – 0.15) to (VIHMIN + 0.15)

(6) Fall time tF = 0.9 VDD to (VILMAX – 0.15)

Figure 1. SMBus Timing Diagram

Figure 1. SMBus Timing Diagram

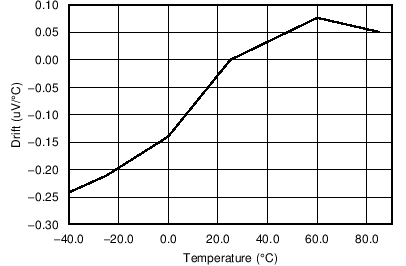

7.31 Typical Characteristics