JAJSVS1A June 2024 – September 2024 BQ51013C-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 概要 (続き)

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Details of a Qi Wireless Power System and BQ51013C-Q1 Power Transfer Flow Diagrams

- 8.3.2 Dynamic Rectifier Control

- 8.3.3 Dynamic Efficiency Scaling

- 8.3.4 RILIM Calculations

- 8.3.5 Input Overvoltage

- 8.3.6 Adapter Enable Functionality and EN1/EN2 Control

- 8.3.7 End Power Transfer Packet (WPC Header 0x02)

- 8.3.8 Status Outputs

- 8.3.9 WPC Communication Scheme

- 8.3.10 Communication Modulator

- 8.3.11 Adaptive Communication Limit

- 8.3.12 Synchronous Rectification

- 8.3.13 Temperature Sense Resistor Network (TS)

- 8.3.14 3-State Driver Recommendations for the TS/CTRL Pin

- 8.3.15 Thermal Protection

- 8.3.16 WPC v2.0 Compliance – Foreign Object Detection

- 8.3.17 Receiver Coil Load-Line Analysis

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

BQ51013C-Q1 Wireless Power Receiver Used as a Power

Supply

- 9.2.1.1 Design Requirements

- 9.2.1.2

Detailed Design Procedure

- 9.2.1.2.1 Using The BQ51013C-Q1 as a Wireless Power Supply: (See Figure 1-1 )

- 9.2.1.2.2 Series and Parallel Resonant Capacitor Selection

- 9.2.1.2.3 Recommended RX Coils

- 9.2.1.2.4 COMM, CLAMP, and BOOT Capacitors

- 9.2.1.2.5 Control Pins and CHG

- 9.2.1.2.6 Current Limit and FOD

- 9.2.1.2.7 RECT and OUT Capacitance

- 9.2.1.3 Application Curves

- 9.2.2 Dual Power Path: Wireless Power and DC Input

- 9.2.3 Wireless and Direct Charging of a Li-Ion Battery at 800 mA

- 9.2.1

BQ51013C-Q1 Wireless Power Receiver Used as a Power

Supply

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Revision History

- 14Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- RHL|20

サーマルパッド・メカニカル・データ

- RHL|20

発注情報

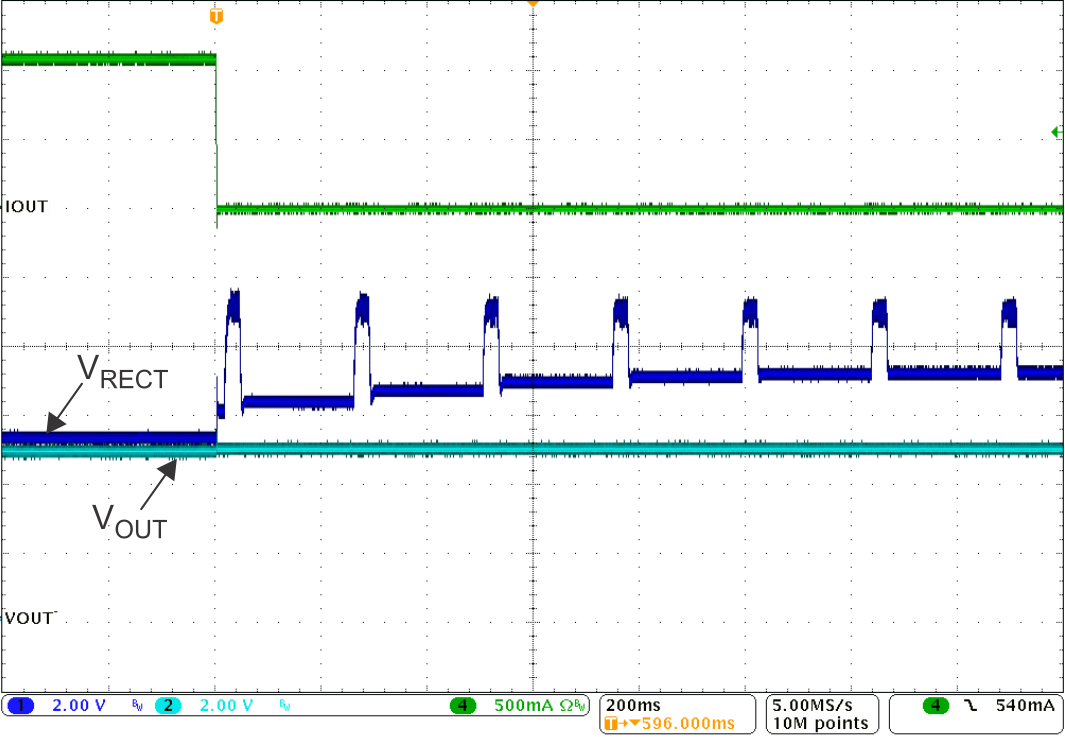

7.6 Typical Characteristics

| Input: RX AC power | Output: RX RECT power | |

| Efficiency: Output Power / Input Power | ||

| Input: TX DC power | Output: RX RECT power | |

| Plot: Output Power / Input Power | ||

| RILIM = 250 Ω and 750 Ω |

| COUT = 1 µf | Without Communication | |

| Input: TX DC power | Output: RX RECT power | |

| Efficiency: Output Power / Input Power | ||

| RILIM = 250 Ω | ||

| Maximum Current = 1 A |

- Efficiency measured from DC input to the transmitter to DC output of the receiver. The BQ500210EVM-689 TX was used for these measurements. Measurement subject to change if an alternate TX is used.

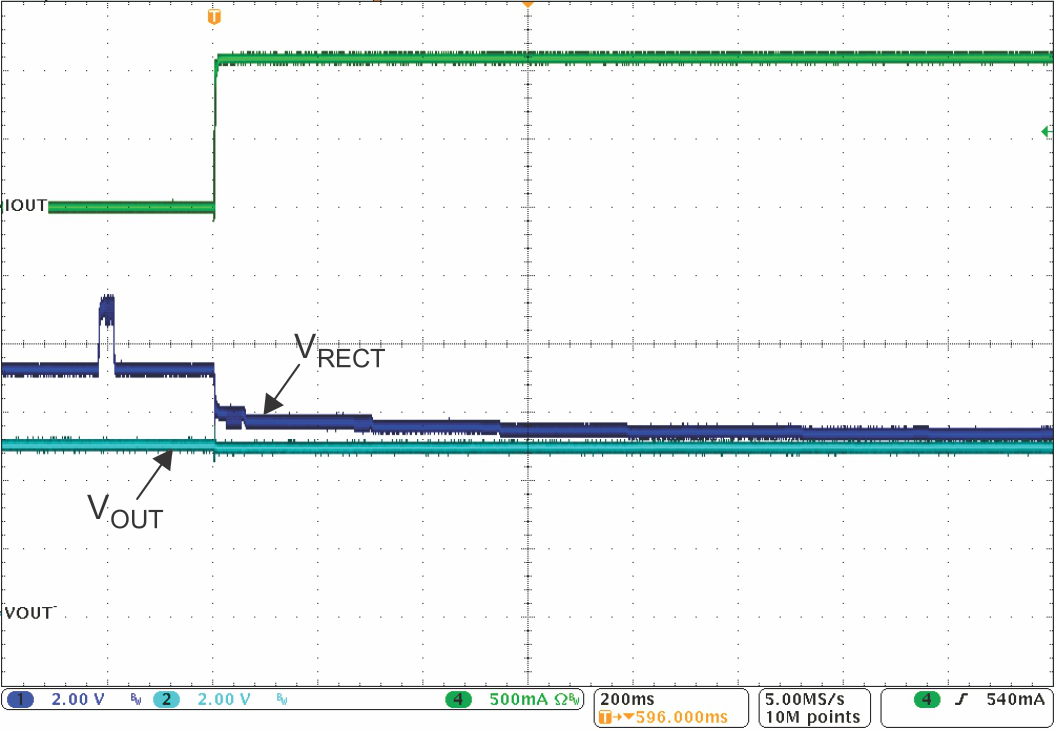

- Total droop experienced at the output is dependent on receiver coil design. The output impedance must be low enough at that particular operating frequency in order to not collapse the rectifier below 5 V.

- On-the-go mode is enabled by driving EN1 high. In this test, the external PMOS is connected between the output of the BQ51013C-Q1 device and the AD pin; therefore, any voltage source on the output is supplied to the AD pin.