-

CDx4AC273、CDx4ACT273 オクタル D タイプ フリップ フロップ、リセット付き JAJSUL8C November 1998 – May 2024 CD54AC273 , CD54ACT273 , CD74AC273 , CD74ACT273

PRODUCTION DATA

-

CDx4AC273、CDx4ACT273 オクタル D タイプ フリップ フロップ、リセット付き

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- J|20

サーマルパッド・メカニカル・データ

発注情報

Data Sheet

CDx4AC273、CDx4ACT273 オクタル D タイプ フリップ フロップ、リセット付き

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- バッファ付き入力

- 伝搬遅延時間 (標準値)

- VCC = 5V、TA = 25℃、CL = 50pF で 6.5ns

- SCR ラッチアップ耐性の高い CMOS プロセスと回路設計

- 消費電力を大幅に低減した、バイポーラ FAST™/AS/S の速度

- 伝搬遅延時間の平衡化

- AC タイプは 1.5V~5.5V で動作し、バランスのとれたノイズ耐性を電源の 30% で実現

- ±24mA 出力駆動電流

- 15個の FAST™ IC にファンアウト

- 50Ω 伝送ラインを駆動

2 概要

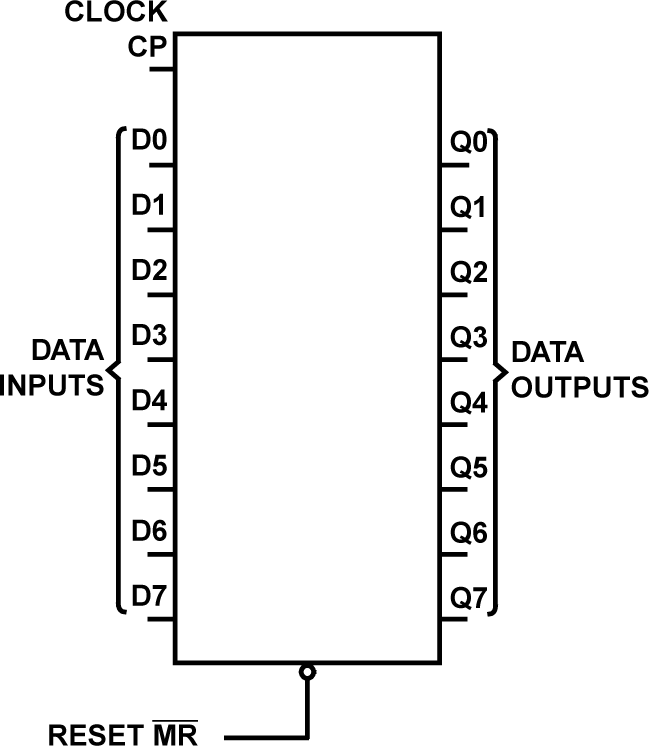

'AC273 および 'ACT273 デバイスは、アドバンスト CMOS ロジック技術を使用したリセット付きオクタル D タイプ フリップ フロップです。D 入力の情報は、クロック パルスの正方向エッジで Q 出力に転送されます。8 つのフリップ フロップはすべて、共通クロック (CP) と共通リセット (MR) で制御されます。リセットは、クロックとは独立した低電圧レベルで行われます。

製品情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| CD74AC273/CD74ACT273 | DW (SOIC、20) | 12.8 mm × 10.3 mm | 12.8 mm × 7.5 mm |

| DB (SSOP、20) | 7.2 mm × 7.8 mm | 7.2 mm × 5.3 mm | |

| N (PDIP、20) | 24.33 mm × 9.4 mm | 24.33 mm × 6.35 mm | |

| PW (TSSOP、20) | 5.00 mm × 6.4 mm | 5.00 mm × 4.4 mm |

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

機能ブロック図

機能ブロック図3 Pin Configuration and Functions

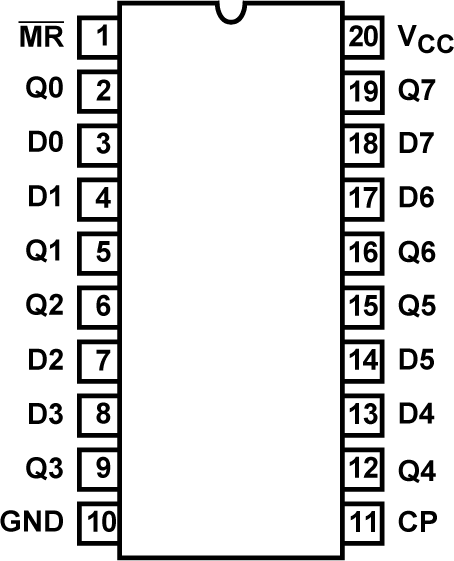

Figure 3-1 CD54AC273, CD54ACT273 (CDIP)

CD74AC273, CD74ACT273 (PDIP, SOIC) Top View

Figure 3-1 CD54AC273, CD54ACT273 (CDIP)

CD74AC273, CD74ACT273 (PDIP, SOIC) Top ViewPin Functions

| PIN | I/O(1) | DESCRIPTION | |

|---|---|---|---|

| NO. | NAME | ||

| !MR | 1 | I | Master reset, active low |

| Q0 | 2 | O | Output Q0 |

| D0 | 3 | I | Input D0 |

| D1 | 4 | I | Input D1 |

| Q1 | 5 | O | Output Q1 |

| Q2 | 6 | O | Output Q2 |

| D2 | 7 | I | Input D2 |

| D3 | 8 | I | Input D3 |

| Q3 | 9 | O | Output Q3 |

| GND | 10 | - | Ground |

| CP | 11 | I | Clock, rising edge triggered |

| Q4 | 12 | O | Output Q4 |

| D4 | 13 | I | Input D4 |

| D5 | 14 | I | Input D5 |

| Q5 | 15 | O | Output Q5 |

| Q6 | 16 | O | Output Q6 |

| D6 | 17 | I | Input D6 |

| D7 | 18 | I | Input D7 |

| Q7 | 19 | O | Output Q7 |

| VCC | 20 | - | Supply |

(1) I = input, O = output, I/O =

input or output, G = ground, P = power.