JAJSUL8C November 1998 – May 2024 CD54AC273 , CD54ACT273 , CD74AC273 , CD74ACT273

PRODUCTION DATA

- 1

- 1 特長

- 2 概要

- 3 Pin Configuration and Functions

- 4 Specifications

- 5 Parameter Measurement Information

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- N|20

- DW|20

サーマルパッド・メカニカル・データ

発注情報

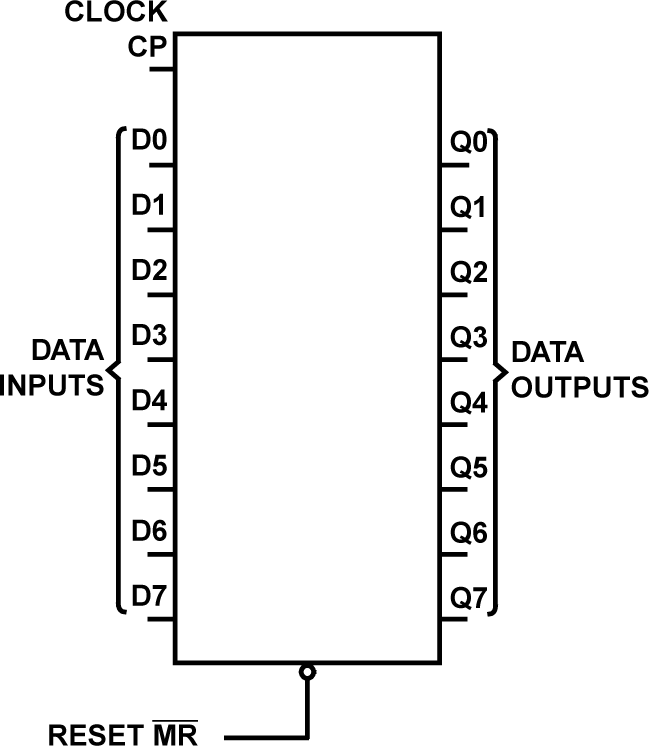

2 概要

'AC273 および 'ACT273 デバイスは、アドバンスト CMOS ロジック技術を使用したリセット付きオクタル D タイプ フリップ フロップです。D 入力の情報は、クロック パルスの正方向エッジで Q 出力に転送されます。8 つのフリップ フロップはすべて、共通クロック (CP) と共通リセット (MR) で制御されます。リセットは、クロックとは独立した低電圧レベルで行われます。

製品情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| CD74AC273/CD74ACT273 | DW (SOIC、20) | 12.8 mm × 10.3 mm | 12.8 mm × 7.5 mm |

| DB (SSOP、20) | 7.2 mm × 7.8 mm | 7.2 mm × 5.3 mm | |

| N (PDIP、20) | 24.33 mm × 9.4 mm | 24.33 mm × 6.35 mm | |

| PW (TSSOP、20) | 5.00 mm × 6.4 mm | 5.00 mm × 4.4 mm |

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

機能ブロック図

機能ブロック図