-

CDCLVP111 Low-Voltage 1:10 LVPECL With Selectable Input Clock Driver

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- RHB|32

発注情報

CDCLVP111 Low-Voltage 1:10 LVPECL With Selectable Input Clock Driver

1 Features

- Distributes One Differential Clock Input Pair LVPECL to 10 Differential LVPECL

- Fully Compatible With LVECL and LVPECL

- Supports a Wide Supply Voltage Range from 2.375 V to 3.8 V

- Selectable Clock Input Through CLK_SEL

- Low-Output Skew (Typical 15 ps) for Clock-Distribution Applications

- Additive Jitter Less Than 1 ps

- Propagation Delay Less Than 350 ps

- Open Input Default State

- LVDS, CML, SSTL Input Compatible

- VBB Reference Voltage Output for Single-Ended Clocking

- Available in a 32-Pin LQFP and QFN Package

- Frequency Range From DC to 3.5 GHz

- Pin-to-Pin Compatible With MC100 Series EP111, ES6111, LVEP111, PTN1111

2 Applications

- Designed for Driving 50-Ω Transmission Lines

- High Performance Clock Distribution

3 Description

The CDCLVP111 clock driver distributes one differential clock pair of LVPECL input, (CLK0, CLK1) to ten pairs of differential LVPECL clock (Q0, Q9) outputs with minimum skew for clock distribution. The CDCLVP111 can accept two clock sources into an input multiplexer. The CDCLVP111 is specifically designed for driving 50-Ω transmission lines. When an output pin is not used, leaving it open is recommended to reduce power consumption. If only one of the output pins from a differential pair is used, the other output pin must be identically terminated to 50 Ω.

The VBB reference voltage output is used if single-ended input operation is required. In this case, the VBB pin should be connected to CLK0 and bypassed to GND through a 10-nF capacitor.

However, for high-speed performance up to 3.5 GHz, the differential mode is strongly recommended.

The CDCLVP111 device is characterized for operation from –40°C to 85°C.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| CDCLVP111 | VQFN (32) | 5.00 mm × 5.00 mm |

| LQFP (32) | 7.00 mm × 7.00 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Functional Block Diagram

4 Revision History

Changes from E Revision (July 2011) to F Revision

- Added Device Information Table, Pin Configuration and Functions; Specifications; Applications and Implementation; Detailed Description; Layout;Device and Documentation Support; Mechanical, Packaging, and Ordering InformationGo

- Added extended frequency range from 1GHz down to 100MHz Go

Changes from D Revision (March 2010) to E Revision

- Changed the PowerPAD Pin Function DescriptionGo

Changes from C Revision (November 2009) to D Revision

- Changed the PowerPAD description in the PIN FUNCTIONS table to include the LQFP package information.Go

- Deleted duplicate information covering the PowerPAD from Note 1 of the Pin Functions table.Go

- Added "NOTE" at the beginning of "Applications and Implementation" section.Go

- Changed JEDEC symbol to RθJAGo

Changes from B Revision (April 2009) to C Revision

- Changed PowerPAD information to the Pinout PackageGo

- Added PowerPAD information to the Pin Functions tableGo

Changes from A Revision (March 2009) to B Revision

Changes from * Revision (January 2009) to A Revision

5 Pin Configuration and Functions

Pin Functions(1)

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VCC | Supply voltage (Relative to VEE) | –0.3 | 4.6 | V |

| VI | Input voltage | –0.3 | VCC + 0.5 | V |

| VO | Output voltage | –0.3 | VCC + 0.5 | V |

| IIN | Input current | ±20 | mA | |

| VEE | Negative supply voltage (Relative to VCC) | –4.6 | 0.3 | V |

| IBB | Sink/source current | –1 | 1 | mA |

| IO | DC output current | –50 | mA | |

| TJ | Maximum operating junction temperature | 125 | °C | |

| Tstg | Storage temperature | –65 | 150 | °C |

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | 3000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | 1500 | |||

6.3 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VCC | Supply voltage (relative to VEE) | 2.375 | 2.5/3.3 | 3.8 | V |

| TA | Operating free-air temperature | –40 | 85 | °C/W | |

| TJ | Operating junction temperature | 110 | °C |

6.4 Thermal Information

| THERMAL METRIC(1) | CDCLVP111 | UNIT | ||

|---|---|---|---|---|

| RHB (VQFN) | VF (LQFP) | |||

| 32 PINS | ||||

| RθJA | Junction-to-ambient thermal resistance | 45.2 | 85.1 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 37.5 | 23.2 | °C/W |

| RθJB | Junction-to-board thermal resistance | 17.9 | 49.4 | °C/W |

| ψJT | Junction-to-top characterization parameter | 1.5 | 0.9 | °C/W |

| ψJB | Junction-to-board characterization parameter | 17.9 | 48.7 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 9.7 | — | °C/W |

6.5 DC Electrical Characteristics, LVECL

Vsupply: VCC = 0 V, VEE = –2.375 V to –3.8 V over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| IEE | Supply internal current | Absolute value of current | –40°C, 25°C, 85°C | 40 | 85 | mA | |

| ICC | Output and internal supply current | All outputs terminated 50 Ω to VCC – 2 V | –40°C | 354 | mA | ||

| 25°C | 380 | ||||||

| 85°C | 405 | ||||||

| IIN | Input current | Includes pullup/pulldown resistors, VIH = VCC, VIL = VCC - 2 V |

–40°C, 25°C, 85°C | –150 | 150 | μA | |

| VBB | Internally generated bias voltage | For VEE = –3 to –3.8 V, IBB = –0.2 mA |

–40°C, 25°C, 85°C | –1.45 | –1.3 | –1.15 | V |

| VEE = –2.375 to –2.75 V, IBB = –0.2 mA |

–40°C, 25°C, 85°C | –1.4 | –1.25 | –1.1 | |||

| VIH | High-level input voltage (CLK_SEL) | –40°C, 25°C, 85°C | –1.165 | –0.88 | V | ||

| VIL | Low-level input voltage (CLK_SEL) | –40°C, 25°C, 85°C | –1.81 | –1.475 | V | ||

| VID | Input amplitude (CLKn, CLKn) | Difference of input, see (1) |

–40°C, 25°C, 85°C | 0.5 | 1.3 | V | |

| VCM | Common-mode voltage (CLKn, CLKn) | DC offset relative to VEE | –40°C, 25°C, 85°C | VEE + 1 | –0.3 | V | |

| VOH | High-level output voltage | IOH = –21 mA | –40°C | –1.26 | –0.85 | V | |

| 25°C | –1.2 | –0.85 | |||||

| 85°C | –1.15 | –0.85 | |||||

| VOL | Low-level output voltage | IOL = –5 mA | –40°C | –1.85 | –1.5 | V | |

| 25°C | –1.85 | –1.45 | |||||

| 85°C | –1.85 | –1.4 | |||||

| VOD | Differential output voltage swing | Terminated with 50 Ω to VCC –2 V, see Figure 5 |

–40°C, 25°C, 85°C | 600 | mV | ||

6.6 DC Electrical Characteristics, LVPECL

Vsupply: VCC = 2.375 V to 3.8 V, VEE= 0 V over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| IEE | Supply internal current | Absolute value of current | –40°C, 25°C, 85°C | 40 | 85 | mA | |

| ICC | Output and internal supply current | All outputs terminated 50 Ω to VCC – 2 V | -40°C | 354 | mA | ||

| 25°C | 380 | ||||||

| 85°C | 405 | ||||||

| IIN | Input current | Includes pullup/pulldown resistors VIH=VCC, VIL= VCC–2V |

–40°C, 25°C, 85°C | –150 | 150 | μA | |

| VBB | Internally generated bias voltage | VCC = 3 to 3.8 V, IBB= –0.2 mA | –40°C, 25°C, 85°C | VCC – 1.45 | VCC – 1.3 | VCC – 1.15 | V |

| VCC = 2.375 to 2.75 V, IBB = –0.2 mA |

–40°C, 25°C, 85°C | VCC – 1.4 | VCC – 1.25 | VCC – 1.1 | |||

| VIH | High-level input voltage (CLK_SEL) | –40°C, 25°C, 85°C | VCC – 1.165 | VCC – 0.88 | V | ||

| VIL | Low-level input voltage (CLK_SEL) | –40°C, 25°C, 85°C | VCC – 1.81 | VCC – 1.475 | V | ||

| VID | Input amplitude (CLKn, CLKn) | Difference of inpu, see (1), |

–40°C, 25°C, 85°C | 0.5 | 1.3 | V | |

| VCM | Common-mode voltage (CLKn, CLKn) |

DC offset relative to VEE | –40°C, 25°C, 85°C | 1 | VCC – 0.3 | V | |

| VOH | High-level output voltage |

IOH = –21 mA | –40°C | VCC – 1.26 | VCC – 0.85 | V | |

| 25°C | VCC – 1.2 | VCC – 0.85 | |||||

| 85°C | VCC – 1.15 | VCC – 0.85 | |||||

| VOL | Low-level output voltage |

IOL = –5 mA | –40°C | VCC – 1.85 | VCC – 1.5 | V | |

| 25°C | VCC – 1.85 | VCC – 1.45 | |||||

| 85°C | VCC – 1.85 | VCC – 1.4 | |||||

| VOD | Differential output voltage swing |

Terminated with 50 Ω to VCC - 2 V, see Figure 5 |

–40°C, 25°C, 85°C | 600 | mV | ||

6.7 AC Electrical Characteristics

Vsupply: VCC = 2.375 V to 3.8 V, VEE = 0 V or LVECL/LVPECL input VCC = 0 V, VEE = -2.375 V to -3.8 V over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| tpd | Differential propagation delay CLKn, CLKn to all Q0, Q0… Q9, Q9 | See Note D in Figure 2 | 200 | 350 | ps | |

| tsk(o) | Output-to-output skew | See Note A in Figure 2 | 15 | 30 | ps | |

| tsk(pp) | Part-to-part skew | See Note B in Figure 2 | 70 | ps | ||

| taj | Additive phase jitter | Integration bandwidth of 20 kHz to 20 MHz, fout = 125 MHz at 25°CC |

0.04 | < 0.8 | ps | |

| f(max) | Maximum frequency | Functional up to 3.5 GHz | 3500 | MHz | ||

| tr/tf | Output rise and fall time (20%, 80%) | See Note D in Figure 2 | 90 | 200 | ps | |

7 Parameter Measurement Information

7.1 Test Configurations

Figure 3. Output Voltage and Rise and Fall Time

Figure 3. Output Voltage and Rise and Fall Time

Figure 4. Typical Termination for Output Driver (See the Interfacing Between LVPECL, LVDS, and CML Application Note, SCAA056)

Figure 4. Typical Termination for Output Driver (See the Interfacing Between LVPECL, LVDS, and CML Application Note, SCAA056)

Figure 5. LVPECL Output DC Configuration During Device Test

Figure 5. LVPECL Output DC Configuration During Device Test

Figure 6. LVPECL Output AC Configuration During Device Test

Figure 6. LVPECL Output AC Configuration During Device Test

8 Detailed Description

8.1 Overview

The CDCLVP111 is an open emitter for LVPECL outputs. Therefore, proper biasing and termination are required to ensure correct operation of the device and to minimize signal integrity. The proper termination for LVPECL outputs is a 50 Ω to (VCC –2) V, but this DC voltage is not readily available on PCB. Therefore, a Thevenin equivalent circuit is worked out for the LVPECL termination in both direct-coupled (DC) and AC-coupled configurations. These configurations are shown in Figure 8 (a and b) for VCC = 2.5 V and Figure 9 (a and b) for VCC = 3.3 V, respectively. TI recommends to place all resistive components close to either the driver end or the receiver end. If the supply voltage for the driver and receiver is different, AC coupling is required.

8.2 Functional Block Diagram

8.3 Feature Description

The CDCLVP111 is a low-additive jitter universal to LVPECL fan out buffer with 2 selectable inputs. The small package, low-output skew, and low-additive jitter make for a flexible device in demanding applications.

8.4 Device Functional Modes

Select Input Terminal By CLK_SEL Pin

Table 1. Function Table

| CLK_SEL | ACTIVE CLOCK INPUT |

|---|---|

| 0 | CLK0, CLK0 |

| 1 | CLK1, CLK1 |

The two inputs of the CDCLVP111 are internally mixed together and can be selected through the control pin. Unused inputs and outputs can be left floating to reduce overall component cost. Both AC and DC coupling schemes can be used with the CDCLVP111 to provide greater system flexibility.

9 Applications and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

9.1 Application Information

The CDCLVP111 is a low-additive jitter LVPECL fanout buffer that can generate 5 copies of 2 selectable LVDS, CML or SSTL inputs. The CDCLVP111 can accept reference clock frequencies up to 3.5 GHz while providing low-output skew.

9.2 Typical Application

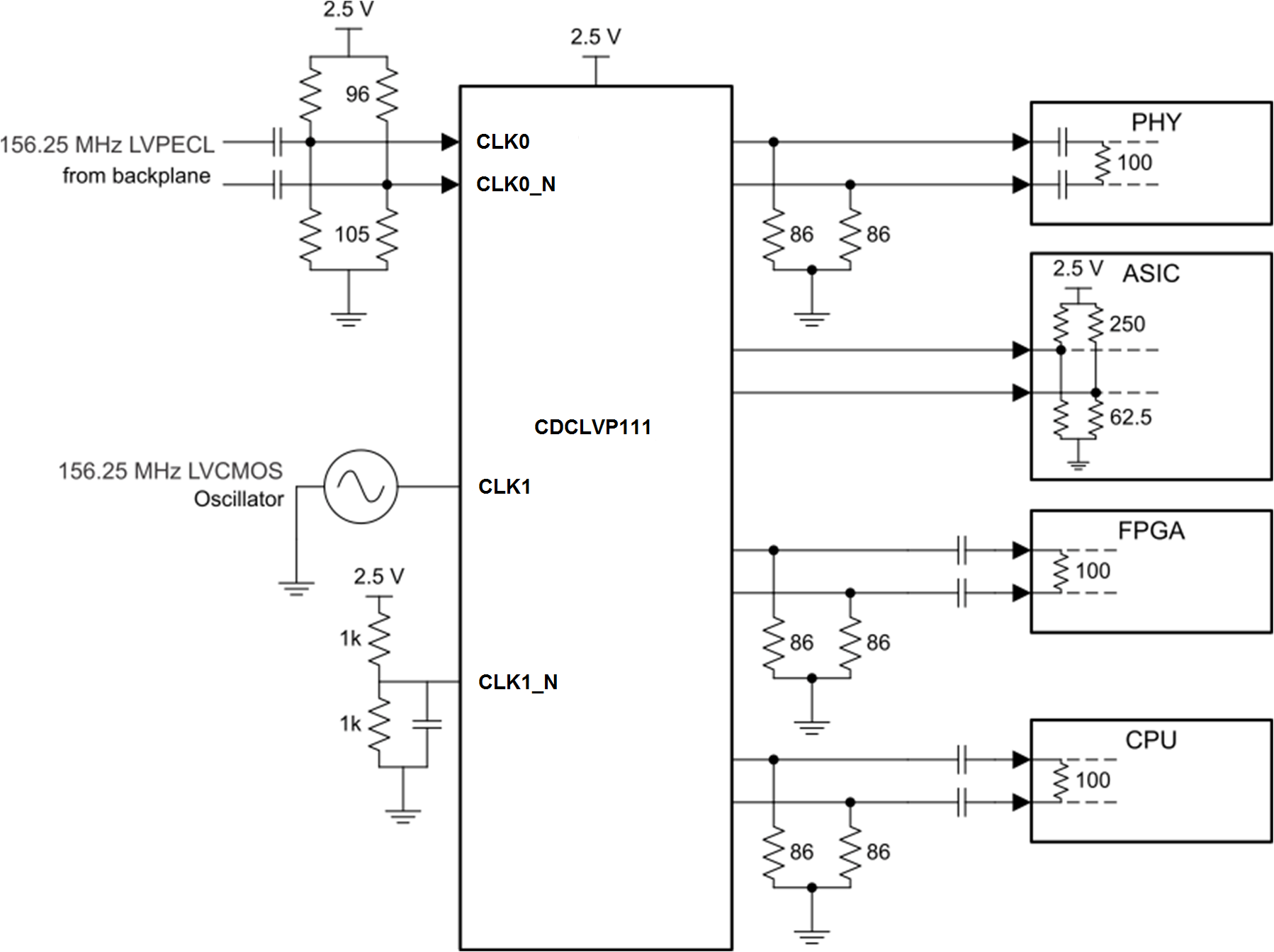

9.2.1 Fanout Buffer for Line Card Application

Figure 7. CDCLVP111 Block Diagram

Figure 7. CDCLVP111 Block Diagram

9.2.1.1 Design Requirements

The CDCLVP111 shown in Figure 7 is configured to be able to select 2 inputs, a 156.25-MHz LVPECL clock from the backplane, or a secondary 156.25-MHz LVCMOS 2.5-V oscillator. Either signal can be then fanned out to desired devices, as shown.

The configuration example is driving 4 LVPECL receivers in a line card application with the following properties:

- The PHY device has internal AC coupling and appropriate termination and biasing. The CDCLVP111 will need to be provided with 86-Ω emitter resistors near the driver for proper operation.

- The ASIC is capable of DC coupling with a 2.5-V LVPECL driver such as the CDCLVP111. This ASIC features internal termination so no additional components are needed.

- The FPGA requires external AC coupling but has internal termination. Again, 86-Ω emitter resistors are placed near the CDCLVP111 and a 0.1-uF are placed to provide AC coupling. Similarly, the CPU is internally terminated and requires external AC coupling capacitors.

9.2.1.2 Detailed Design Procedure

Unused outputs can be left floating.

In this example, the PHY, ASIC, and FPGA/CPU require different schemes. Power-supply filtering and bypassing is critical for low-noise applications.

See Figure 18 for recommended filtering techniques.

9.2.1.2.1 LVPECL Output Termination

Refer to Figure 8 for output termination schemes depending on the receiver application.

Figure 8. LVPECL Output DC and AC Termination for VCC = 2.5 V

Figure 8. LVPECL Output DC and AC Termination for VCC = 2.5 V

Figure 9. LVPECL Output DC and AC Termination for VCC = 3.3 V

Figure 9. LVPECL Output DC and AC Termination for VCC = 3.3 V

9.2.1.2.2 Input Termination

The CDCLVP111 inputs can be interfaced with LVPECL, LVDS, or LVCMOS drivers. Figure 10 illustrates how to DC couple an LVCMOS input to the CDCLVP111. The series resistance (RS) should be placed close to the LVCMOS driver; the value is calculated as the difference between the transmission line impedance and the driver output impedance.

Refer to Figure 10 for proper input terminations, dependent on single ended or differential inputs.

Figure 10. DC-Coupled LVCMOS Input to CDCLVP111

Figure 10. DC-Coupled LVCMOS Input to CDCLVP111

Figure 11 shows how to DC couple LVDS inputs to the CDCLVP111. Figure 12 and Figure 13 describe the method of DC coupling LVPECL inputs to the CDCLVP111 for VCC = 2.5 V and VCC = 3.3 V, respectively.

Figure 11. DC-Coupled LVDS Inputs to CDCLVP111

Figure 11. DC-Coupled LVDS Inputs to CDCLVP111

Figure 13. DC-Coupled LVPECL Inputs to CDCLVP111 (VCC = 3.3 V)

Figure 13. DC-Coupled LVPECL Inputs to CDCLVP111 (VCC = 3.3 V)

Figure 14 and Figure 15 show the technique of AC coupling differential inputs to the CDCLVP111 for VCC = 2.5 V and VCC = 3.3 V, respectively. TI recommends to place all resistive components close to either the driver end or the receiver end. If the supply voltages of the driver and receiver are different, AC coupling is required.

Figure 14. AC-Coupled Differential Inputs to CDCLVP111 (VCC = 2.5 V)

Figure 14. AC-Coupled Differential Inputs to CDCLVP111 (VCC = 2.5 V)

Figure 15. AC-Coupled Differential Inputs to CDCLVP111 (VCC = 3.3 V)

Figure 15. AC-Coupled Differential Inputs to CDCLVP111 (VCC = 3.3 V)

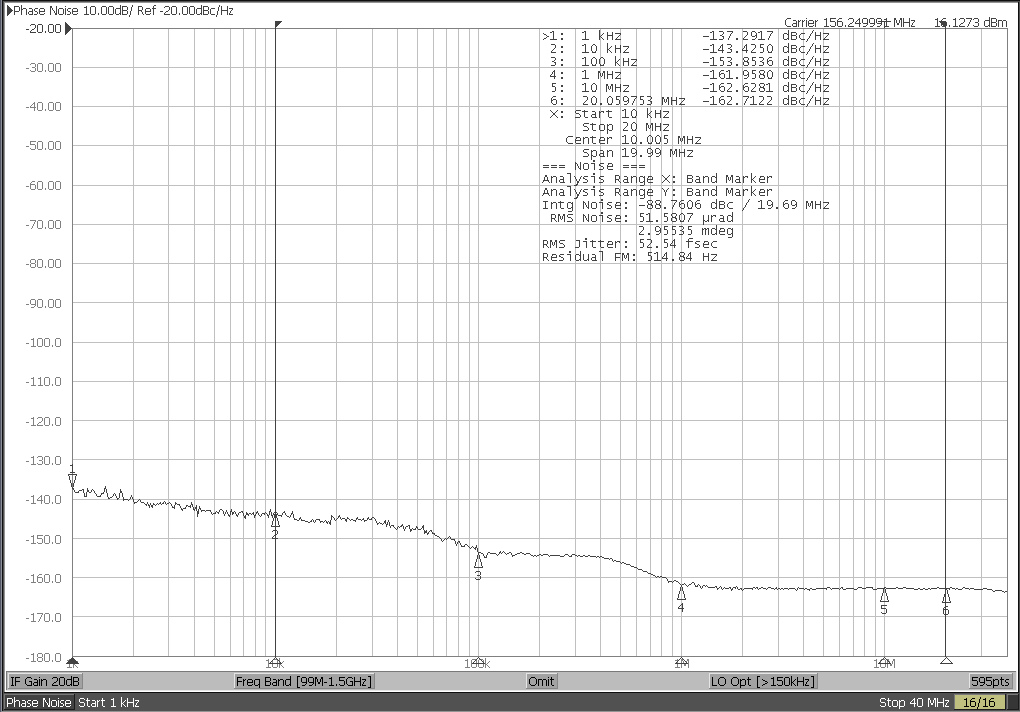

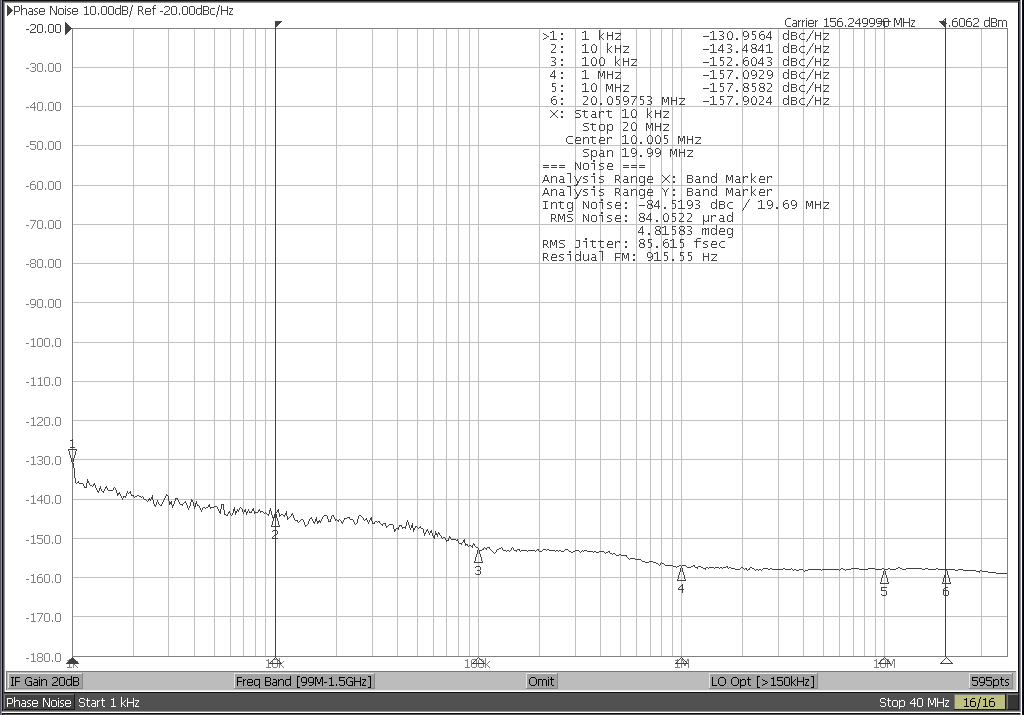

9.2.1.3 Application Curves

The CDCLVP111 low-additive noise can be shown in this line card application. The low-noise, 156.25-MHz signal with 53-fs RMS jitter drives the CDCLVP111, resulting in 86-fs RMS when integrated from 10 kHz to 20 MHz. The resultant-additive jitter is a low 68-fs RMS for this configuration.

| Reference signal is low noise signal generator | ||

(10 kHz to 20 MHz)

(10 kHz to 20 MHz)

10 Power Supply Recommendations

10.1 Power-Supply Filtering

High-performance clock buffers are sensitive to noise on the power supply, which can dramatically increase the additive jitter of the buffer. Thus, it is essential to reduce noise from the system power supply, especially when jitter and phase noise is very critical to applications.

Filter capacitors are used to eliminate the low-frequency noise from the power supply, where the bypass capacitors provide the very low-impedance path for high-frequency noise and guard the power-supply system against the induced fluctuations. These bypass capacitors also provide instantaneous current surges as required by the device and should have low equivalent series resistance (ESR). To properly use the bypass capacitors, they must be placed very close to the power-supply terminals and laid out with short loops to minimize inductance. TI recommends to add as many high-frequency (for example, 0.1-μF) bypass capacitors as there are supply terminals in the package. TI recommends, but does not require, to insert a ferrite bead between the board power supply and the chip power supply that isolates the high-frequency switching noises generated by the clock driver; these beads prevent the switching noise from leaking into the board supply. It is imperative to choose an appropriate ferrite bead with very low dc resistance to provide adequate isolation between the board supply and the chip supply, as well as to maintain a voltage at the supply terminals that is greater than the minimum voltage required for proper operation.

Figure 18 illustrates this recommended power-supply decoupling method.

Figure 18. Power-Supply Decoupling

Figure 18. Power-Supply Decoupling