JAJSCU0A December 2016 – March 2019 CSD18512Q5B

PRODUCTION DATA.

5.3 Typical MOSFET Characteristics

TA = 25°C (unless otherwise stated)

| ID = 30 A | VDS = 20 V | ||

| ID = 250 µA | ||

| ID = 30 A | ||

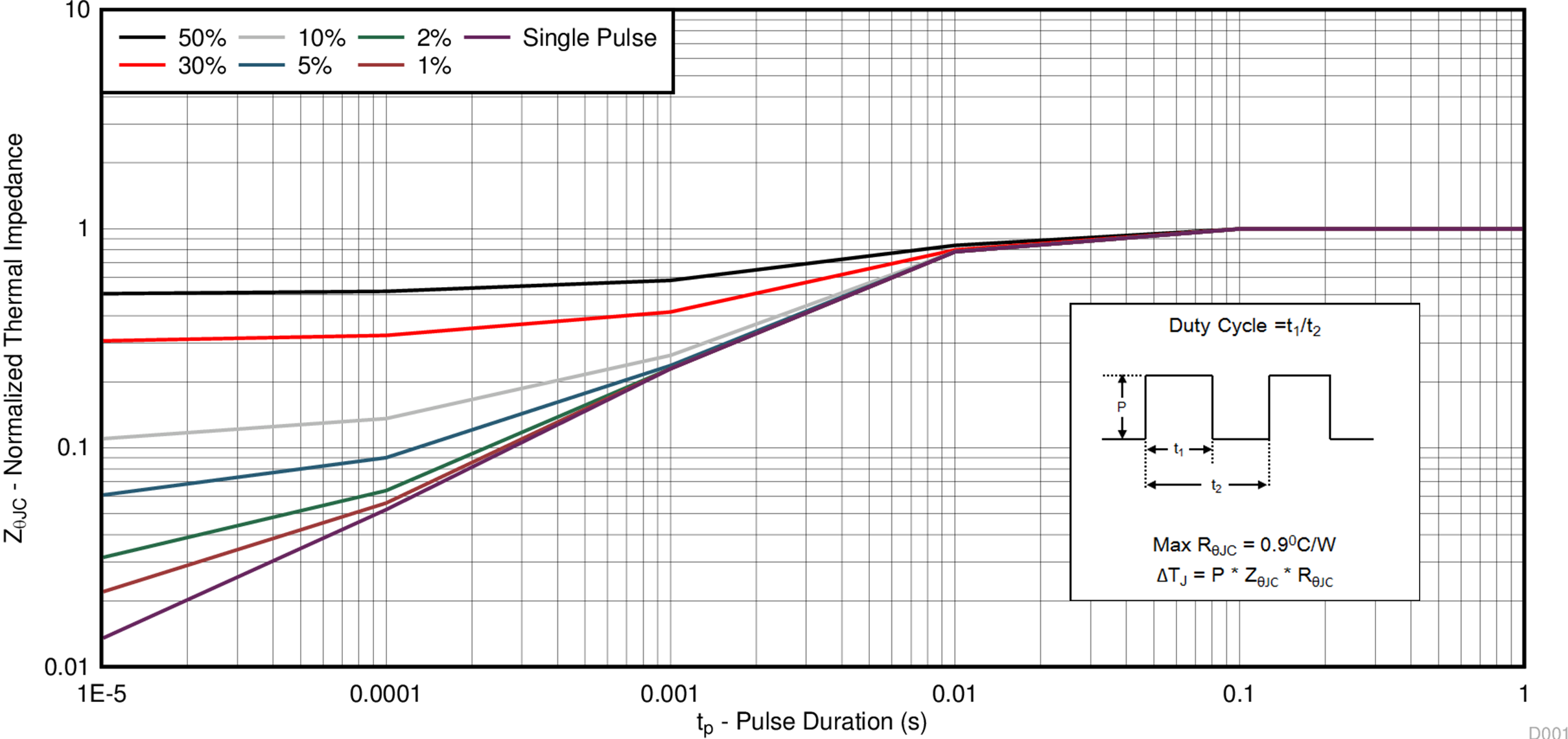

| Max RθJC= 0.9°C/W | ||

| VDS = 5 V | ||